Where are We Now? The Five Classic Components of Computer System - PowerPoint PPT Presentation

Where are We Now? The Five Classic Components of Computer System Architecture a Computer Processor Part II Processor Input Control Memory Chalermek Intanagonwiwat Datapath Output Todays Topic: Designing the Slides courtesy of

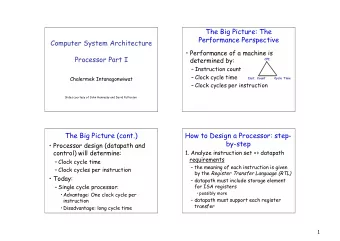

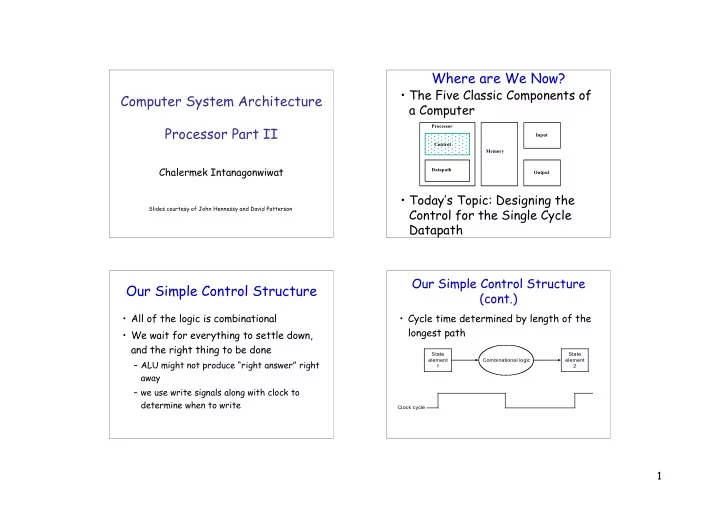

Where are We Now? • The Five Classic Components of Computer System Architecture a Computer Processor Part II Processor Input Control Memory Chalermek Intanagonwiwat Datapath Output • Today’s Topic: Designing the Slides courtesy of John Hennessy and David Patterson Control for the Single Cycle Datapath Our Simple Control Structure Our Simple Control Structure (cont.) • All of the logic is combinational • Cycle time determined by length of the longest path • We wait for everything to settle down, and the right thing to be done State State element Combinational logic element – ALU might not produce “right answer” right 1 2 away – we use write signals along with clock to determine when to write Clock cycle 1

RTL: The Add Instruction Instruction Fetch Unit at the Beginning of Add 31 26 21 16 11 6 0 op rs rt rd shamt funct 6 bits 5 bits 5 bits 5 bits 5 bits 6 bits Inst Instruction<31:0> Memory • add rd, rs, rt Adr – mem[PC] Fetch the instruction • Fetch the instruction from nPC_sel from memory Instruction memory: Instruction <- mem[PC] 4 – R[rd] <- R[rs] + R[rt] The actual Adder – This is the same for all operation 00 instructions Mux PC – PC <- PC + 4 Calculate the next Adder instruction’s address Clk imm16 PC Ext The Single Cycle Datapath during Instruction Fetch Unit at the End of Add Add Instruction<31:0> nPC_sel= +4 Instruction <21:25> <16:20> <11:15> Inst <0:15> Fetch Unit Instruction<31:0> Memory Rd Rt Clk RegDst = 1 Adr 1 0 Mux ALUctr = Add Rs Rt Rt Rs Rd Imm16 RegWr = 1 5 5 5 nPC_sel MemtoReg = 0 • PC <- PC + 4 busA Zero MemWr = 0 Rw Ra Rb busW – This is the same for all 32 32 32-bit ALU 4 0 Registers 32 instructions except: busB 32 Adder 0 Clk Mux 32 Branch and Jump Mux 00 32 1 Mux WrEn Adr Extender PC 1 Data In 32 Data imm16 Adder 32 16 Memory Clk Clk imm16 ALUSrc = 0 ExtOp = x 2

The Single Cycle Datapath during The Single Cycle Datapath during Or Immediate Load Instruction<31:0> Instruction<31:0> nPC_sel= +4 nPC_sel= +4 Instruction <21:25> <16:20> <11:15> Instruction <0:15> <21:25> <16:20> <11:15> <0:15> Fetch Unit Rd Rt Fetch Unit Rd Rt Clk RegDst = 0 Clk RegDst = 0 1 0 Mux 1 0 Mux ALUctr = Rt Rs Rd Imm16 Rs Rt Rt Rs Rd Imm16 Rs Rt RegWr = 1 Add ALUctr = Or 5 5 5 MemtoReg = 1 RegWr = 1 5 5 5 MemtoReg = 0 busA Zero MemWr = 0 busA Zero MemWr = 0 Rw Ra Rb Rw Ra Rb busW 32 busW 32 32-bit 32 ALU 32 32-bit 0 ALU 0 32 Registers busB 32 32 Registers 0 busB 32 0 Clk Mux Clk Mux 32 Mux 32 Mux 32 1 WrEn Adr 1 WrEn Adr Extender Extender 1 Data In 1 32 Data In 32 Data 32 Data imm16 32 imm16 32 16 Memory 16 Memory Clk Clk ALUSrc = 1 ALUSrc = 1 ExtOp = 1 ExtOp = 0 The Single Cycle Datapath during The Single Cycle Datapath during Store Branch Instruction<31:0> Instruction<31:0> nPC_sel= +4 nPC_sel= “Br” Instruction Instruction <21:25> <16:20> <11:15> <21:25> <16:20> <11:15> <0:15> <0:15> Fetch Unit Fetch Unit Rd Rt Rd Rt Clk Clk RegDst = x RegDst = x 1 0 1 0 Mux Mux ALUctr ALUctr = Rs Rt Rt Rs Rd Imm16 Rs Rt Rt Rs Rd Imm16 RegWr = 0 RegWr = 0 = Add Subtract 5 5 5 5 5 5 MemtoReg = x MemtoReg = x busA Zero MemWr = 1 busA Zero MemWr = 0 Rw Ra Rb Rw Ra Rb busW busW 32 32 32 32-bit 32 32-bit ALU ALU 0 0 Registers Registers 32 32 busB 32 busB 32 0 0 Clk Mux Clk Mux 32 32 Mux Mux 32 32 1 1 WrEn Adr WrEn Adr Extender Extender 1 1 Data In 32 Data In 32 Data Data imm16 imm16 32 32 16 Memory 16 Memory Clk Clk ALUSrc = 1 ALUSrc = 0 ExtOp = 1 ExtOp = x 3

Instruction Fetch Unit at the End Step 4: Given Datapath: RTL -> of Branch Control Instruction<31:0> Inst Inst <21:25> <21:25> <16:20> <11:15> Instruction<31:0> <0:15> Memory Memory Adr Adr Op Fun Rt Rs Rd Imm16 • if (Zero == 1) then nPC_sel PC = PC + 4 + Control 4 SignExt[imm16]*4 ; Adder nPC_sel ALUSrc ALUctr MemWr MemtoReg else PC = PC + 4 RegWr RegDst ExtOp Equal 00 Mux PC Adder DATA PATH Clk imm16 A Summary of Control Signals A Summary of Control Signals (cont.) inst Register Transfer LOAD R[rt] <– MEM[ R[rs] + sign_ext(Imm16)]; ADD R[rd] <– R[rs] + R[rt]; PC <– PC + 4 PC <– PC + 4 ALUsrc = RegB, ALUctr = “add”, RegDst = rd, ALUsrc = Im, Extop = “Sn”, ALUctr = “add”, MemtoReg, RegDst = rt, RegWr, nPC_sel = “+4” RegWr, nPC_sel = “+4” SUB R[rd] <– R[rs] – R[rt]; PC <– PC + 4 STORE MEM[ R[rs] + sign_ext(Imm16)] <– R[rs]; PC <– PC + 4 ALUsrc = RegB, ALUctr = “sub”, RegDst = rd, ALUsrc = Im, Extop = “Sn”, ALUctr = “add”, RegWr, nPC_sel = “+4” MemWr, nPC_sel = “+4” ORi R[rt] <– R[rs] | zero_ext(Imm16); PC <– PC + 4 BEQ if ( R[rs] == R[rt] ) then ALUsrc = Im, Extop = “Z”, ALUctr = “or”, PC <– PC + sign_ext(Imm16)] || 00 else PC <– PC + 4 RegDst = rt, RegWr, nPC_sel = “+4” nPC_sel = “Br”, ALUctr = “sub” 4

A Summary of the Control Signals The Concept of Local Decoding (cont.) op 00 0000 00 1101 10 0011 10 1011 00 0100 00 0010 R-type ori lw sw beq jump See func 10 0000 10 0010 We Don’t Care :-) RegDst 1 0 0 x x x Appendix A op 00 0000 00 0000 00 1101 10 0011 10 1011 00 0100 00 0010 ALUSrc 0 1 1 1 0 x MemtoReg 0 0 1 x x x add sub ori lw sw beq jump RegWrite 1 1 1 0 0 0 RegDst 1 1 0 0 x x x MemWrite 0 0 0 1 0 0 Branch 0 0 0 0 1 0 ALUSrc 0 0 1 1 1 0 x Jump 0 0 0 0 0 1 MemtoReg 0 0 0 1 x x x ExtOp x 0 1 1 x x RegWrite 1 1 1 1 0 0 0 ALUop<N:0> “R-type” Or Add Add xxx Subtract MemWrite 0 0 0 0 1 0 0 func nPCsel 0 0 0 0 0 1 0 ALUctr ALU op 6 Main 3 Control Jump 0 0 0 0 0 0 1 ALUop 6 Control (Local) N ExtOp x x 0 1 1 x x ALU ALUctr<2:0> Add Subtract Or Add Add Subtract xxx The Encoding of ALUop The Encoding of ALUop (cont.) func ALU op 6 ALUctr Main Control • To implement the full MIPS ISA, ALUop ALUop Control 6 3 (Local) N has to be 3 bits to represent: • In this exercise, ALUop has to be 2 bits – (1) “R-type” instructions wide to represent: – “I-type” instructions that require the ALU to – (1) “R-type” instructions perform: – “I-type” instructions that require the ALU • (2) Or, (3) Add, (4) Subtract, and (5) And to perform: (Example: andi) • (2) Or, (3) Add, and (4) Subtract R-type ori lw sw beq jump ALUop (Symbolic) “R-type” Or Add Add xxx Subtract ALUop<2:0> 1 00 0 10 0 00 0 00 xxx 0 01 5

The Decoding of the “func” Field The Truth Table for ALUctr func funct<3:0> Instruction Op. ALU op 6 ALUctr Main 0000 add Control ALUop Control 6 3 (Local) R-type ori lw sw beq 0010 subtract ALUop N (Symbolic) “R-type” Or Add Add Subtract 0100 and ALUop<2:0> 1 00 0 10 0 00 0 00 0 01 0101 or R-type ori lw sw beq jump 1010 set-on-less-than ALUop (Symbolic) “R-type” Or Add Add xxx Subtract ALUop<2:0> 1 00 0 10 0 00 0 00 0 01 xxx ALUop func ALU ALUctr Operation 31 26 21 16 11 6 0 bit<2> bit<1> bit<0> bit<3> bit<2> bit<1> bit<0> bit<2> bit<1> bit<0> R-type op rs rt rd shamt funct 0 0 0 x x x x Add 0 1 0 0 x 1 x x x x Subtract 1 1 0 Recall ALU Homework (also P. 286 text): 0 1 x x x x x Or 0 0 1 funct<5:0> Instruction Operation ALUctr ALUctr<2:0> ALU Operation 1 x x 0 0 0 0 Add 0 1 0 10 0000 add 000 Add 1 x x 0 0 1 0 Subtract 1 1 0 10 0010 subtract 001 Subtract 1 x x 0 1 0 0 And 0 0 0 ALU 10 0100 and 010 And 1 x x 0 1 0 1 Or 0 0 1 10 0101 or 110 Or 1 x x 1 0 1 0 Set on < 1 1 1 10 1010 set-on-less-than 111 Set-on-less-than The Logic Equation for ALUctr<2> The Logic Equation for ALUctr<1> ALUop func ALUop func bit<2> bit<1> bit<0> bit<3> bit<2> bit<1> bit<0> ALUctr<2> bit<2> bit<1> bit<0> bit<3> bit<2> bit<1> bit<0> ALUctr<1> 0 x 1 x x x x 1 0 0 0 x x x x 1 1 x x 0 0 1 0 1 0 x 1 x x x x 1 1 x x 1 0 1 0 1 1 x x 0 0 0 0 1 1 x x 0 0 1 0 1 This makes func<3> a don’t care 1 x x 1 0 1 0 1 • ALUctr<2> = !ALUop<2> & ALUop<0> + • ALUctr<1> = !ALUop<2> & !ALUop<1> + ALUop<2> & !func<2> & func<1> & !func<0> ALUop<2> & !func<2> & !func<0> 6

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.