Warmup Use a k-map to fi nd a minimal implementation of this truth - PowerPoint PPT Presentation

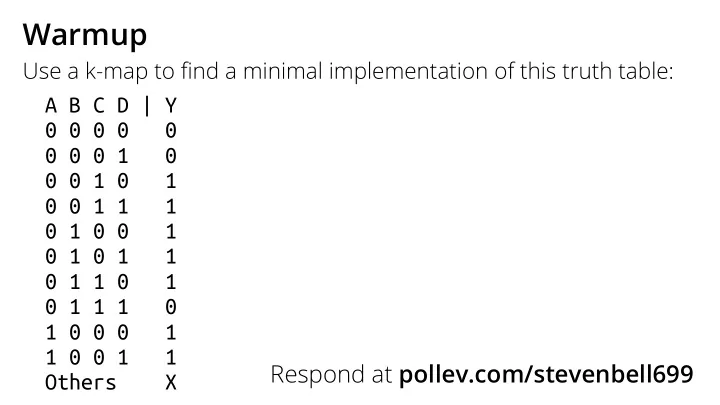

Warmup Use a k-map to fi nd a minimal implementation of this truth table: A B C D | Y 0 0 0 0 0 0 0 0 1 0 0 0 1 0 1 0 0 1 1 1 0 1 0 0 1 0 1 0 1 1 0 1 1 0 1 0 1 1 1 0 1 0 0 0 1 1 0 0 1 1 Respond at pollev.com/stevenbell699

Warmup Use a k-map to fi nd a minimal implementation of this truth table: A B C D | Y 0 0 0 0 0 0 0 0 1 0 0 0 1 0 1 0 0 1 1 1 0 1 0 0 1 0 1 0 1 1 0 1 1 0 1 0 1 1 1 0 1 0 0 0 1 1 0 0 1 1 Respond at pollev.com/stevenbell699 Others X

EE 201: Multiplexers and timing Steven Bell 31 January 2019

By the end of class today, you should be able to: Explain what a multiplexer is Draw a logic diagram using a 2 N -input multiplexer to implement an N-variable boolean equation Describe the basic structure of an FPGA Given a circuit and timing information about the gates, calculate the contamination delay and propagation delay Explain what glitches are and why they occur

Multiplexers Select one of 2 N inputs based on the binary value of N control wires A B C 000 001 010 011 100 101 110 111

A practical example write_enable 0 storage output new element value 1 value (updates continuously)

Implementing XOR Using a mux as a look-up table (LUT) V dd A B 00 Y=A ⊕ B 01 10 11

Multiplexer practice 1 Implement this logic equation using 1) discrete gates 2) 8:1 multiplexer 3) 4:1 multiplexer Y=AB+ABC

Implement a 2-bit adder with multiplexers

iCE40UP block diagram PLB RGB I/O RGB I/O RGB I/O I3C I/O I3C I/O I 2 C I 2 C I/O Bank 0 Clock stu ff PWM IP HFOSC PLL LFOSC 50 ns Delay 5 4 Kb DPRAM 5 4 Kb DPRAM 50 ns Delay 8 Logic Cells = Programmable Logic Block Fixed-function 50 ns Filter 50 ns Filter DSP DSP multipliers Fixed-function 5 4 Kb DPRAM 5 4 Kb DPRAM DSP 5 PLB Rows DSP I/O modules NVCM Memory 5 4 Kb DPRAM 5 4 Kb DPRAM DSP DSP config Logic "fabric" DSP DSP 256 Kb 256 Kb 256 Kb 256 Kb SPRAM SPRAM SPRAM SPRAM config I/O Bank 2 SPI Carry Logic SPI I/O Bank 1_SPI 4 ‐ Input Look ‐ up Table (LUT) Flip ‐ flop with Enableand Reset Controls Figure 3.1. iCE40UP5K Device, Top View

iCE40UP logic element Shared Block ‐ Level Controls Programmable Clock Logic Block (PLB) Enable FCOUT 1 Set/Reset 0 Logic Cell Carry Logic DFF O I0 D Q EN I1 8 Logic Cells (LCs) LUT SR I2 I3 FCIN Four ‐ input Flip ‐ flop with Look ‐ Up Table optional enable and (LUT) set or reset controls = Statically defined by configuration program Figure 3.2. PLB Block Diagram

Timing Depends on lots of things! (excerpts from SN74LS04 datasheet) switching characteristics, V CC = 5 V, T A = 25 ° C (see Figure 1) SN5404 FROM TO SN7404 PARAMETER TEST CONDITIONS UNIT PARAMETER TEST CONDITIONS UNIT (INPUT) (INPUT) (OUTPUT) (OUTPUT) MIN TYP MAX tPLH 12 22 Ω , A A Y Y RL = 400 CL = 15 pF ns ns tPHL 8 15 switching characteristics, V CC = 5 V, T A = 25 ° C (see Figure 1) SN54S04 FROM TO SN74S04 PARAMETER PARAMETER TEST CONDITIONS TEST CONDITIONS UNIT UNIT (INPUT) (INPUT) (OUTPUT) (OUTPUT) MIN TYP MAX tPLH 3 4.5 RL = 280 Ω , A A Y Y CL = 15 pF ns ns tPHL 3 5 tPLH 4.5 Ω , A A Y Y RL = 280 CL = 50 pF ns ns tPHL 5

Timing A Y R L C L

Timing Contamination delay : the soonest that the output might change Propagation delay : the maximum time for the output to settle

Timing practice

Who cares? t cd and t pd combine to determine how fast the circuit can run.

Glitches

For Tuesday 1. Read the book (4.1-4.2) and complete the pre-class quiz www.ece.tufts.edu/ee/201/ Quiz is due at 9AM the day of class, so I can review it cp /ee/201/public_html/quizzes/quiz_04.txt ./ provide ee201 q4 quiz_04.txt 2. Homework (posted tomorrow) will be due next Thursday (2/7)

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.