VMM Emulation of Intel Hardware Transactional Memory Maciej - PowerPoint PPT Presentation

VMM Emulation of Intel Hardware Transactional Memory Maciej Swiech, Kyle Hale, Peter Dinda Northwestern University V3VEE Project www.v3vee.org Hobbes Project 1 What will we talk about? We added the capability to run Intel HTM code on a

VMM Emulation of Intel Hardware Transactional Memory Maciej Swiech, Kyle Hale, Peter Dinda Northwestern University V3VEE Project www.v3vee.org Hobbes Project 1

What will we talk about? • We added the capability to run Intel HTM code on a virtual machine with minimal emulation • We developed a new page-flipping technique that allows capturing of reads and writes at single memory reference granularity • Software implementation of HTM emulation allows for arbitrary transaction size and code testing 2

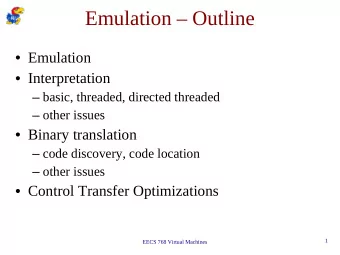

Outline • Motivation / Background • Intel HTM • Architecture • Palacios • Evaluation • Conclusions 3

Outline • Motivation / Background • Intel HTM • Architecture • Palacios • Evaluation • Conclusions 4

Motivation | transactional memory • Processors and applications become more parallel and distributed to cope with growing scale of data and research problems • Need for easier and more reliable methods for concurrent programming 5

Background | transactional memory do_the_things() { write_shared_mem(); do_the_things(); read_shared_mem(); } 6

Background | transactional memory Instead of: acquire_lock(); do_the_things() { write_shared_mem(); do_the_things(); read_shared_mem(); } release_lock(); 7

Background | transactional memory Instead of: acquire_lock(); Have to track locks do_the_things(); Deadlock release_lock(); 8

Background | transactional memory Can do: acquire_lock(); transaction { do_the_things(); do_the_things(); } release_lock(); 9

Background | transactional memory Can do: acquire_lock(); transaction { Unsafe concurrent memory do_the_things(); do_the_things(); accesses are detected by TM } release_lock(); Easier to write safe code UNSAFE: Write after Read Read after Write Write after Write 10

Background | transactional memory • Transactions are • Composable • Easier to reason about • More optimistic than locking • Assumption: no other code will touch memory in TX • HTM is faster than STM 11

Motivation | virtualizing • Currently only Intel Haswell and IBM chipsets have implementations of Hardware Transactional Memory • Adding HTM capabilities to a virtual machine monitor would allow anyone to run transactional code • Allows for testing effects of new hardware implementations on code 12

Outline • Motivation / Background • Intel HTM • Architecture • Palacios • Evaluation • Conclusions 13

Intel HTM | background • In the Haswell generation of processors Intel introduced 2 Hardware Transactional Memory implementations • RTM – Restricted Transactional Memory • HLE – Hardware Lock Elision • 4 new instructions added to the ISA • XBEGIN • XABORT • XEND • XTEST 14

Intel HTM | ISA • XBEGIN imm32 • Marks beginning of a transaction and abort label • XABORT imm32 • Forces transaction abort • XEND • Marks end of transaction • XTEST • Tests if processor is currently in a transaction state 15

Intel HTM | example start_label: XBEGIN abort_label <body of transaction, may use XABORT> XEND success_label: <handle transaction commited> abort_label: <handle transaction aborted> 16

Intel HTM | specification • Intel list many reasons a transaction “ may ” abort • Operations that modify RIP, GPRs, status flags • Operations on XMM, YMM, MXCSR registers • Various other instructions • Synchronous exception events • Asynchronous events such as interrupts • Self-modifying code • Many others… • RaW, WaR, WaW conflicts trigger an abort 17

Outline • Motivation / Background • Intel HTM • Palacios • Architecture • Evaluation • Conclusions 18

Architecture | design • Hypervisor extension • TM events captured and handled in VMM • Redo-log based design with garbage collection • Minimal instruction decoding 19

Architecture | design • MIME • Generate stream of memory read/writes • RTME • Maintains the redo log • Tracks system state • Conflict Detection • Garbage Collection 20

Architecture | RTME Restricted Transactional Memory Engine • Finite State Machine model • SYSTEM state • CORE state • TSX instructions generate #UD exceptions, driving state • Maintains read/write logs for each transaction 21

Architecture | RTME Restricted Transactional Memory Engine • Keeps track of per-core and system transactional state • Places cores in single-stepping mode • If one core single-stepping, all cores • Launches garbage collection of log entries 22

Architecture | example Restricted Transactional Memory Engine start_label: XBEGIN abort_label <body of transaction, may use XABORT> XEND success_label: <handle transaction commited> abort_label: <handle transaction aborted> 23

Architecture | example Restricted Transactional Memory Engine System in TM mode start_label: Core in TM mode XBEGIN abort_label <body of transaction, may use XABORT> XEND success_label: <handle transaction commited> abort_label: <handle transaction aborted> 24

Architecture | example Restricted Transactional Memory Engine start_label: XBEGIN abort_label <body of transaction, may use XABORT> XEND Monitor abort conditions success_label: (incl. XABORT) <handle transaction commited> Maintain redo-log abort_label: <handle transaction aborted> 25

Architecture | example Restricted Transactional Memory Engine start_label: XBEGIN abort_label <body of transaction, may use XABORT> XEND CHECK WaW conflicts success_label: CHECK RaW conflicts CHECK WaR conflicts <handle transaction commited> abort_label: <handle transaction aborted> 26

Architecture | example Restricted Transactional Memory Engine start_label: XBEGIN abort_label <body of transaction, may use XABORT> XEND success_label: COMMIT write log <handle transaction commited> abort_label: <handle transaction aborted> 27

Architecture | example Restricted Transactional Memory Engine start_label: XBEGIN abort_label <body of transaction, may use XABORT> XEND Core out of TM mode success_label: Launch GC <handle transaction commited> abort_label: <handle transaction aborted> 28

Architecture | example Restricted Transactional Memory Engine start_label: XBEGIN abort_label <body of transaction, may use XABORT> XEND Core out of TM mode success_label: Launch GC <handle transaction commited> if no cores in TM, abort_label: System out of TM mode <handle transaction aborted> 29

Architecture | example Restricted Transactional Memory Engine start_label: XBEGIN abort_label <body of transaction, may use XABORT> XEND success_label: If any abort condition is triggered <handle transaction commited> Runs at given code point abort_label : <handle transaction aborted> All intermediate state is discarded 30

Architecture | MIME Memory and Instruction Meta Engine • Leverages • Shadow Page Table page fault hooking • Instruction length decoding • Hypercall insertion Memory access single-stepping • Staging page to keep writes hidden until commit 31

Architecture | example Memory and Instruction Meta Engine prev: addq %rbx, %rax cur: INSTRUCTION next: movq %rdx, %rbx ... target: ... 32

Architecture | example Memory and Instruction Meta Engine prev: addq %rbx, %rax cur: INSTRUCTION Decode instruction length… next: movq %rdx, %rbx ... target: ... 33

Architecture | example Memory and Instruction Meta Engine prev: addq %rbx, %rax cur: INSTRUCTION …replace next instr with hypercall next: VMCALL ... target: ... saved instr: movq %rdx, %rbx 34

Architecture | example Memory and Instruction Meta Engine prev: addq %rbx, %rax Flush the shadow page tables cur: INSTRUCTION next: VMCALL All guest mem access page fault ... target: ... saved instr: movq %rdx, %rbx 35

Architecture | example Memory and Instruction Meta Engine prev: addq %rbx, %rax IFETCH sPT fault cur: INSTRUCTION next: VMCALL Map the instruction page in ... target: ... saved instr: movq %rdx, %rbx 36

Architecture | example Memory and Instruction Meta Engine prev: addq %rbx, %rax Read: map page in as read-only cur: INSTRUCTION Write: map staging page in next: VMCALL ... target: Read: record address ... Write: record address and value saved instr: movq %rdx, %rbx 37

Architecture | example Memory and Instruction Meta Engine prev: addq %rbx, %rax Signals end of instruction cur: INSTRUCTION If staging page was used, copy data next: VMCALL into redo log ... target: ... saved instr: movq %rdx, %rbx 38

Architecture | example Memory and Instruction Meta Engine prev: addq %rbx, %rax cur: INSTRUCTION Restore overwritten instruction next: movq %rdx, rbx ... target: ... saved instr: NULL 39

Architecture | example Memory and Instruction Meta Engine addq %rbx, %rax prev: INSTRUCTION MIME begins again cur: movq %rdx, rbx ... target: ... saved instr: NULL 40

Architecture | example Memory and Instruction Meta Engine prev: addq %rbx, %rax If cur is a control flow inst, cur: INSTRUCTION overwrite target instead of next next: movq %rdx, rbx ... target: VMCALL ... saved instr: ... 41

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.