Upper and Lower Loop Bound Estimation by Symbolic Execution and Loop - PowerPoint PPT Presentation

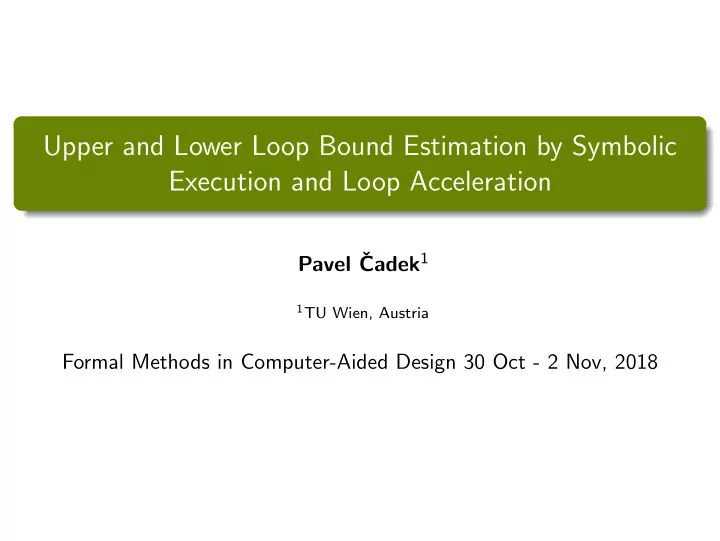

Upper and Lower Loop Bound Estimation by Symbolic Execution and Loop Acceleration Pavel Cadek 1 1 TU Wien, Austria Formal Methods in Computer-Aided Design 30 Oct - 2 Nov, 2018 Loop Bound Analysis Upper loop bound: max { n , 0 } Lower loop

Upper and Lower Loop Bound Estimation by Symbolic Execution and Loop Acceleration Pavel ˇ Cadek 1 1 TU Wien, Austria Formal Methods in Computer-Aided Design 30 Oct - 2 Nov, 2018

Loop Bound Analysis Upper loop bound: max { n , 0 } Lower loop bound: max { n , 0 } i:=0 i<n Usage: worst case execution time i:=i+1 memory consumption i>=n complexity analysis . . . Pavel ˇ Cadek ( TU Wien, Austria ) FMCAD 2018 2 / 5

Symbolic Execution - Path Explosion Path conditions: i:=0 ϕ 1 ≡ 0 ≥ n i<n i>=n ϕ 2 ≡ 0 < n ∧ 1 ≥ n i:=i+1 ϕ 3 ≡ . . . i>=n i<n . . . . . . Pavel ˇ Cadek ( TU Wien, Austria ) FMCAD 2018 3 / 5

Loop Acceleration i:=i+ κ i<n � i:=i+1 i<=n Pavel ˇ Cadek ( TU Wien, Austria ) FMCAD 2018 4 / 5

Combination i:=0 κ >0 Path conditions: ϕ 1 ≡ κ = 0 ∧ 0 ≥ n κ ==0 i:=i+ κ ϕ 2 ≡ κ > 0 ∧ κ ≤ n ∧ κ ≥ n = ⇒ κ = max { n , 0 } i<=n i>=n Pavel ˇ Cadek ( TU Wien, Austria ) FMCAD 2018 5 / 5

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![Permuting Upper and Lower bounds [Aggarwal, Vitter, 88] Page 1 Upper Bound Assume instance is](https://c.sambuz.com/1004934/permuting-upper-and-lower-bounds-s.webp)

![Sorting Upper and Lower bounds [Aggarwal, Vitter, 88] Page 1 Part I: Upper Bound Page 2](https://c.sambuz.com/1029765/sorting-upper-and-lower-bounds-s.webp)

![Permuting Upper and Lower bounds [Aggarwal, Vitter, 88] Page 1 Upper Bound Assume instance is](https://c.sambuz.com/1029795/permuting-upper-and-lower-bounds-s.webp)