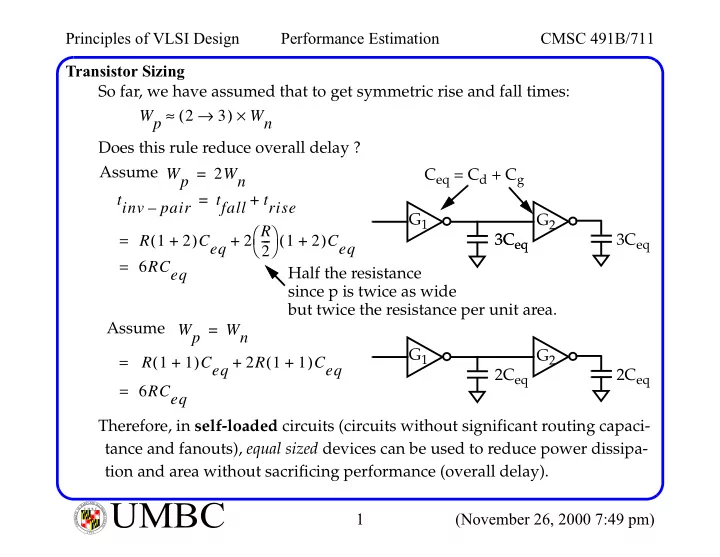

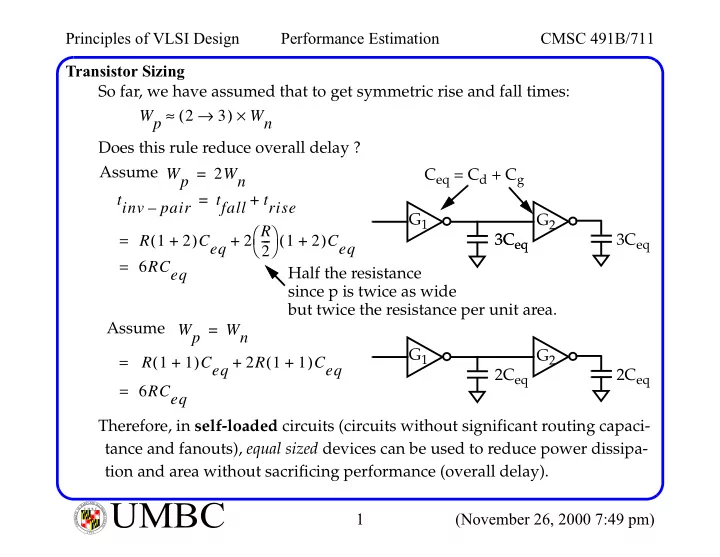

Principles of VLSI Design Performance Estimation CMSC 491B/711 Transistor Sizing So far, we have assumed that to get symmetric rise and fall times: 2 3 ≈ ( → ) × Wp Wn Does this rule reduce overall delay ? = 2 Wn Wp Assume C eq = C d + C g = + tinv tfall trise – pair G 1 G 2 2 R 1 R 1 + 2 + + 2 ( ) Ceq ( ) Ceq 3C eq 3C eq 3C eq = - - - 2 = 6 RCeq Half the resistance since p is twice as wide but twice the resistance per unit area. = Wp Wn Assume G 1 G 2 R 1 + 1 + 2 R 1 + 1 ( ) Ceq ( ) Ceq = 2C eq 2C eq = 6 RCeq Therefore, in self-loaded circuits (circuits without significant routing capaci- tance and fanouts), equal sized devices can be used to reduce power dissipa- tion and area without sacrificing performance (overall delay). L A N R Y D UMBC A B M A L F T U M B C I O M Y O T R 1 (November 26, 2000 7:49 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Performance Estimation CMSC 491B/711 Stage Ratio How do we drive large load capacitances, e.g. off-chip wires via the I/O pads, long buses, etc. ? By using a chain of inverters, where each successive inverter is larger than the previous one. a 2 a 3 1 a G G G 4 G 1 3 2 What is the optimal value of a (the stage ratio) that both • Minimizes the delay through the chain. • Minimizes the area and power. The magic number a is e (~2.7) - see analysis in book. The optimal value may vary depending on process parameters. L A N R Y D UMBC A B M A L F T U M B C I O M Y O T R 2 (November 26, 2000 7:49 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Performance Estimation CMSC 491B/711 Power Dissipation Two components of power dissipation in CMOS circuits: • Static power • Dynamic power Static power dissipation: • Reverse-bias leakage current through parasitic diodes formed by source/ drain diffusion and n-well diffusion. • Through-current of pseudo-nMOS devices. • Subthreshold conduction (current that flows when V in < V tn ). Becoming more important as power supply is scaled down. L A N R Y D UMBC A B M A L F T U M B C I O M Y O T R 3 (November 26, 2000 7:49 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Performance Estimation CMSC 491B/711 Static Dissipation Reverse-bias leakage current qV where I s = the saturation current. - - - - - - kT V = diode voltage. = – 1 I AdIs e Diode equation: kT/q = 25.8mV at 300 degrees K. A d = area of the diode when V is negative, exponential term becomes small. = 0.1 0.5 nA device → ⁄ Ileakage nA cathode n positive at room temperature cathode P leakage of an inverter at 5V = 1 or 2 nW anode p Breakdown voltage Total Static Power dissipation: n m = leakage current supply voltage + through-current ∑ ( × ) ∑ Ps 1 1 L A N R Y D UMBC A B M A L F T U M B C I O M Y O T R 4 (November 26, 2000 7:49 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Performance Estimation CMSC 491B/711 Dynamic Dissipation The current required to charge/discharge capacitive load usually dominates the crowbar (short circuit) current. For example: short circuit I dsn short circuit I dsn I dsn and capacitive I dsp I dsp I dsp - - - + + + + + + - - - 0pF 0.05pF 0.2pF L A N R Y D UMBC A B M A L F T U M B C I O M Y O T R 5 (November 26, 2000 7:49 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Performance Estimation CMSC 491B/711 Capacitive Dissipation However, slow rise and fall times will increase crowbar current of driven gates. Assuming a step input and a repetition frequency of f p , the average dynamic power, P d , is expressed as: 2 = Pd CLVDD fp Therefore power is proportional to • The switching frequency • The capacitive load. 2 . But goes up as V DD Also, power is independent of device parameters, such as V t or beta. L A N R Y D UMBC A B M A L F T U M B C I O M Y O T R 6 (November 26, 2000 7:49 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Performance Estimation CMSC 491B/711 Total Power Dissipation P total = P s + P d + P short-circuit (see text P. 236) Detailed analysis of power is often impractical. Consider the following simplifications: • Calculate total capacitance driven by the gates in the circuit. • Estimate the percentage of the devices operating at the max clock frequency (e.g. 50%). • Use the dynamic power dissipation expression: 2 percent-activity × × Ctotal VDD 1 = fp = Pd - - - - where - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - tp tp Power minimization: • Use complementary logic gates to reduce through current (static) • Use minimum-size devices to reduce diffusion leakage (static). • Reduce V DD , the frequency and the switched capacitance (dynamic). L A N R Y D UMBC A B M A L F T U M B C I O M Y O T R 7 (November 26, 2000 7:49 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Performance Estimation CMSC 491B/711 Sizing Routing Conductors The size of metal conductors is important because: • Metal migration. • Power supply noise and integrity. • RC delay (considered previously). Electro-migration is the transport of metal ions through a conductor induced by direct current. A ’safe’ value of current density, J , is: to 1.0 mA µ m 0.4 mA µ m ⁄ ⁄ For example, consider a clock buffer that drives a 100 pF load at 50 MHz: – 12 6 2 = = 100 × 10 × 25 × 50 × 10 = 125 mW Pd CLVDD fp 125 mW P = = = 25 mA I - - - - - - - - - - - - - - - - - - - - - - 5 V V Using 0.5 mA µ m as the limit, the wire width should be at least 50 µ m ⁄ A safe value would be 100 µ m L A N R Y D UMBC A B M A L F T U M B C I O M Y O T R 8 (November 26, 2000 7:49 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Performance Estimation CMSC 491B/711 Sizing Routing Conductors Power supply noise and integrity: IR drops on V DD and V SS (voltage drops due to current spikes and the resistance of the metal) can occur causing gates to fail. What is the voltage drop (ground bounce) in the power and ground wires if the buffer is 500 microns from the power and ground pads ? 500 µ m = - 0.05 Ω µ m = 0.25 Ω ( ⁄ ) R - - - - - - - - - - - - - - - - 100 µ m = 0.025 A 0.25 = 6.25 mV × IR L A N R Y D UMBC A B M A L F T U M B C I O M Y O T R 9 (November 26, 2000 7:49 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Performance Estimation CMSC 491B/711 Design Margining Sources of variations that effect nominal circuit behavior (2 environmental, 1 manufacturing): • Operating Temperature • Supply Voltage: Data sheets give +/- 10%, e.g., 3.0 to 3.6 for 3.3V. • Process Variation: Normal to keep parts within 2 or 3 sigma. We must design the circuit to operate over all extremes of these variables. Temperature : What happens to I ds with temperature ? 1.38 T 1.5 – ∝ Ids 1.16 1.0 K 0.9 As temperature goes up, Ids 25 ° ( ) 0.7 I ds is reduced. ( ) = Ids T - - - - - - - - - - - - - - - - - - - - - K Military parts requirement Temperature -55 0 25 70 125 L A N R Y D UMBC A B M A L F T U M B C I O M Y O T R 10 (November 26, 2000 7:49 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Performance Estimation CMSC 491B/711 Design Corners Sources of process variation include changes in doping densities, oxide thick- ness and line width variations. The following boundary combinations may result • Fast-n, Fast-p • Fast-n, Slow-p • Slow-n, Fast-p • Slow-n, Slow-p Test at minimum clk Worst power, Fast-n, period -- for margin, high-speed corner Fast-p run clk 10% faster than spec. Test for clock races and Voltage power dissipation. Test for setup and hold Slow-n, time constraints Run at fastest Slow-p clock Worst speed corner Temperature L A N R Y D UMBC A B M A L F T U M B C I O M Y O T R 11 (November 26, 2000 7:49 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Principles of VLSI Design Performance Estimation CMSC 491B/711 Yield Defined as: No. of Good Chips of Wafer = - 100% Y - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - - Total No. of chips Yield verses Testing (ref. Ed McCluskey) Raw materials Manufactured Shipped Manufacturing Parts Parts Testing Process QUALITY YIELD Fraction of parts Fraction of parts Rejects that are Defect-Free that are Defect-Free Yield is influenced by: • Technology • Chip Area • Layout L A N R Y D UMBC A B M A L F T U M B C I O M Y O T R 12 (November 26, 2000 7:49 pm) I E S R C E O V U I N N U T Y 1 6 9 6

Recommend

More recommend