UMBC A B M A L T F O U M B C I M Y O R T 1 - PowerPoint PPT Presentation

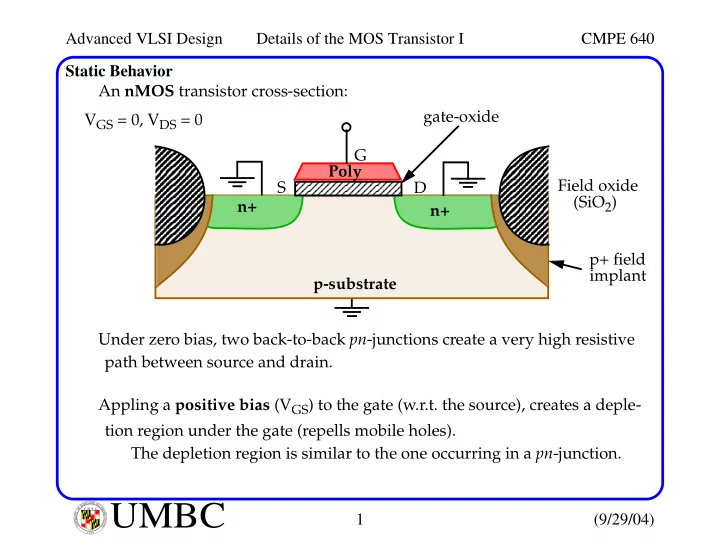

Advanced VLSI Design Details of the MOS Transistor I CMPE 640 Static Behavior An nMOS transistor cross-section: gate-oxide V GS = 0, V DS = 0 G Poly Field oxide S D (SiO 2 ) n+ n+ p+ field implant p-substrate Under zero bias, two

Advanced VLSI Design Details of the MOS Transistor I CMPE 640 Static Behavior An nMOS transistor cross-section: gate-oxide V GS = 0, V DS = 0 G Poly Field oxide S D (SiO 2 ) n+ n+ p+ field implant p-substrate Under zero bias, two back-to-back pn -junctions create a very high resistive path between source and drain. Appling a positive bias (V GS ) to the gate (w.r.t. the source), creates a deple- tion region under the gate (repells mobile holes). The depletion region is similar to the one occurring in a pn -junction. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 1 (9/29/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Details of the MOS Transistor I CMPE 640 Static Behavior Inversion: V GS > 0, V DS = 0 + V GS G - Poly Field oxide S D (SiO 2 ) n+ n+ n+ inversion layer depletion region Depletion region expressions are similar to the diode expressions: 2 ε si φ W d = - - - - - - - - - - - - - Width qN A 2 N A ε si φ Q d Space charge = φ = potential at the oxide-silicon boundary L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 2 (9/29/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Details of the MOS Transistor I CMPE 640 Static Behavior Inversion: At a critical value of V GS , the substrate " inverts " to n-type material. This is called strong inversion and occurs at a voltage that is twice the Fermi Potential : φ F 0.3 V for typical p-type silicon substrates. = – Further increases in V GS do not increase the depletion layer width. The charge is offset with additional inversion-layer electrons (sourced from the heavily doped n+ source region). The conductivity of the n-channel is modulated by V GS . Under strong inversion, the charge in the depletion region is fixed and equals: 2 qN A ε si 2 φ F Q B 0 = – L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 3 (9/29/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Details of the MOS Transistor I CMPE 640 Static Behavior Inversion: A substrate bias voltage, V SB , increases the surface potential needed to create strong inversion to: 2 φ F V SB – + V SB is normally positive for n-channel devices. This changes the charge in the depletion region: 2 qN A ε si 2 φ F Q B V SB = – + The value of V GS where strong inversion occurs is threshold voltage , V T . V T depends on several components, many are material constants: • difference in work function between gate and substrate material. • oxide thickness • Fermi voltage • charge associated with impurities trapped at oxide-channel interface • concentration of implanted ions L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 4 (9/29/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Details of the MOS Transistor I CMPE 640 Static Behavior V T also depends substrate voltage, V SB . Rather than depend on the complete analytical form (which often is not a good predictor of V T ), an empirical parameter is used, V T0 . V T0 is the threshold voltage with V SB = 0. γ ( 2 φ F 2 φ F ) V T V T 0 V SB = + – + – – V T is positive for nMOS and negative for pMOS 2 q ε si N A γ ( γ is the body effect coefficient) = - - - - - - - - - - - - - - - - - - - - - - - - - - C ox γ expresses the impact of changes in V SB . A negative bias on the well or substrate causes V T to increase . γ 2 φ F 0.64 V Given: V T 0 0.75 V = 0.54 = – V SB = 5V = ( ( ) ( ) ) V T 5 V 1.6 V ! = 0.75 + 0.54 – 2 – 0.6 + – – 2 – 0.6 = L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 5 (9/29/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Details of the MOS Transistor I CMPE 640 Static Behavior Current-Voltage Relations: V GS > V T , V DS > 0 + V GS I D G - Poly Field oxide S D (SiO 2 ) n+ n+ n+ - V(x) + L X • Linear Region At a point x along the channel, the voltage is V(x). The gate-to-channel voltage at that point equals V GS -V(x). L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 6 (9/29/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Details of the MOS Transistor I CMPE 640 Static Behavior Linear region Assume that this voltage exceeds the threshold everywhere along the channel. The induced channel charge per unit area at point x is: ( ) [ ( ) ] Q i x C ox V GS V x V T = – – – The gate capacitance per unit area, C ox , is expressed as: ε ox – 13 ε ox × ε 0 × 10 C ox = 3.97 = 3.5 F/cm = - - - - - - - - t ox t ox is gate oxide thickness . It is 10nm or smaller in contemporary processes. For t ox = 5nm, C ox is 7 fF/um 2 . L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 7 (9/29/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Details of the MOS Transistor I CMPE 640 Static Behavior Linear region Current is given as the product of the drift velocity of the carriers and the available charge : υ n = drift velocity υ n x ( ) Q i x ( ) I D W = – W = width of channel The electron velocity , υ , is related to the electric field through a parame- ter called the mobility ( µ ): dV υ n µ n E x ( ) µ n = – = - - - - - - - dx Combining the equations: µ n C ox W V GS ( ) dV I D dx V V T = – – L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 8 (9/29/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Details of the MOS Transistor I CMPE 640 Static Behavior Linear region Integrating this equation over the length of the channel yields the cur- rent-voltage relationship of a nMOS transistor. V DS 2 k n ′ W (1) ( ) V DS I D V GS V T = - - - - - – – - - - - - - - - - - - L 2 k n ′ W k n - - - - - (gain factor) = L µ n ε ox k n ′ µ n C ox (process transconductance parameter) = = - - - - - - - - - - - - - - t ox For typical n-channel devices with: t ox = 20nm k n ′ 80 µ A V 2 ⁄ = For small values of V DS , the quadratic factor can be ignored and we observe a linear relationship between V DS and I D . NOTE: W and L are effective width and length, not the drawn values. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 9 (9/29/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Details of the MOS Transistor I CMPE 640 Static Behavior Saturation When V DS is further increased, the channel voltage all along the channel may cease to be larger than the threshold, e.g., ( ) < V GS V x V T – At that point, the induced charge is zero and the channel disappears or is pinched off . V GS > 0, V DS > 0 V GS - V DS < V T + V GS I D G - Poly Field oxide S D (SiO 2 ) n+ n+ n+ V GS -V T L X L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 10 (9/29/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Details of the MOS Transistor I CMPE 640 Static Behavior Current-Voltage Relation, Saturation. The voltage difference over the induced channel remains fixed at V GS - V T and the current remains constant (or saturates ). Replacing V DS with V GS - V T in equation (1) (since this equation was derived over the channel) yields: k n ′ - W ( ) 2 I D - V GS V T - - - - - - - - - - = – (2) L 2 This equation is not entirely correct, since the channel length changes as a function of V DS . Current increases as channel length (L) decreases , according to equa- tion (2). A more accurate expression for current in saturation is: k n ′ λ : empirical parameter - W - V GS ( ) 2 1 ( λ V DS ) I D V T - - - - - - - - - - = – + L called channel-length modulation 2 L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 11 (9/29/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Details of the MOS Transistor I CMPE 640 Static Behavior Current-Voltage curves V GS = 5V V ds = V gs - V t 2 I-V nMOS transistor curves for a device V GS = 4V with dimensions: I D (mA) 100 µ m W Square = dependence 20 µ m L = 1 V GS = 3V in a 1.2um process. V GS = 2V V GS = 1V 1.0 2.0 3.0 4.0 5.0 V ds (V) L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 12 (9/29/04) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Details of the MOS Transistor I CMPE 640 Static Behavior Current-Voltage Relation. Triode region : The transistor behaves like a voltage-controlled resistor. Saturation region : It behaves like a voltage-controlled current source (ignoring channel-length modulation effects). Linear relationship for values: V DS is held constant 0.020 V GS V T » at 5V. I D Sub-threshold operation 0.010 V T 3.0 2.0 1.0 V GS (V) Note: Analytical expressions of λ have proven inaccurate. Device experiments indicate that λ varies ~ 1/channel length. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 13 (9/29/04) I E S R C E O V U I N N U T Y 1 6 9 6

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.