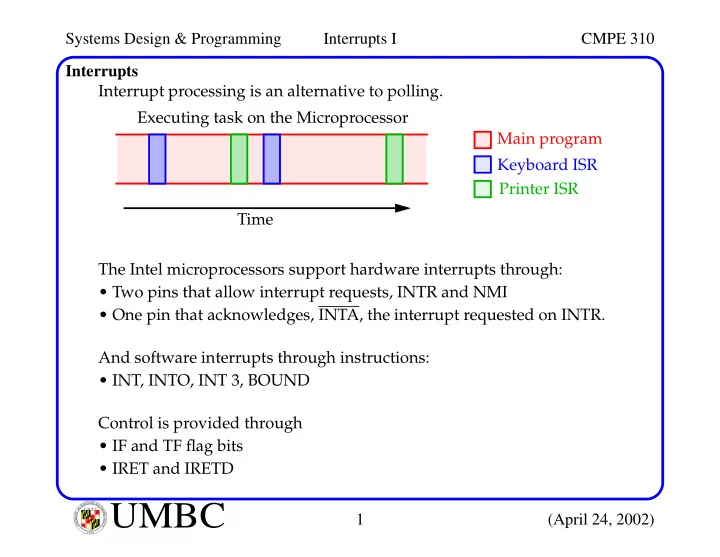

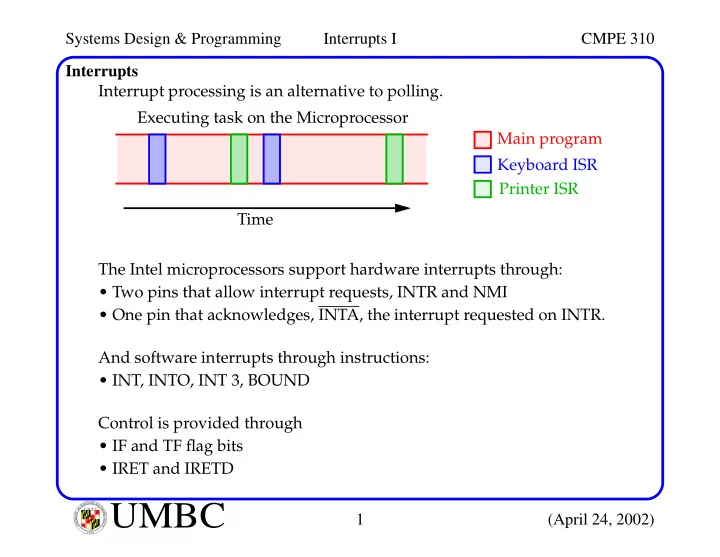

Systems Design & Programming Interrupts I CMPE 310 Interrupts Interrupt processing is an alternative to polling. Executing task on the Microprocessor Main program Keyboard ISR Printer ISR Time The Intel microprocessors support hardware interrupts through: • Two pins that allow interrupt requests, INTR and NMI • One pin that acknowledges, INTA, the interrupt requested on INTR. And software interrupts through instructions: • INT, INTO, INT 3, BOUND Control is provided through • IF and TF flag bits • IRET and IRETD L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 1 (April 24, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design & Programming Interrupts I CMPE 310 Interrupt Vector Table INT and INT3 behave in a similar way. INT n: Calls ISR located at vector n (n*4). The INT instruction requires two bytes of memory, opcode plus n. BOUND and INTO are both conditional. BOUND: BOUND AX , DATA ;Compares AX with DATA AX is compared with DATA and DATA+1, if less than an interrupt occurs. AX is compared with DATA+2 and DATA+3, if greater than an inter- rupt occurs. INTO: Checks the overflow flag (OF). If OF=1, the ISR is called. IRET removes 6 bytes from the stack, 2 for IP, 2 for CS and 2 for FLAGS. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 2 (April 24, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design & Programming Interrupts I CMPE 310 Interrupt Vector Table 32-255 User defined 080H 14-31 Reserved The interrupt vector table is located in the first 1024 bytes of memory at addresses 000000H through 0003FFH. 040H Coprocessor error 16 03CH Unassigned 15 038H 14 Page fault 034H 13 General protection There are 256 4-byte entries (segment 030H 12 Stack seg overrun and offset in real mode). 02CH 11 Segment not present 028H 10 Invalid task state seg 024H 9 Coproc seg overrun 020H 8 Seg high Seg low Offset high Offset low Double fault 01CH 7 Coprocessor not avail Byte 3 Byte 2 Byte 1 Byte 0 018H 6 Undefined Opcode 014H 5 Bound 010H 4 Overflow (INTO) 00CH 3 1-byte breakpoint 008H 2 NMI pin 004H 1 Single-step 000H 0 Divide error L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 3 (April 24, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design & Programming Interrupts I CMPE 310 Real Mode Interrupts After the execution of each instruction, the microprocessor determines whether an interrupt is active by checking, in order: Other instruction executions Single-step NMI Coprocessor segment overrun INTR INT If one or more of these conditions are present, then: FLAGS is pushed onto the stack Both the interrupt (IF) and trap (TF) fl ags ar e cleared, which disables the INTR pin and the trap or single-step feature. The CS and IP are pushed onto the stack. The interrupt vector contents are fetched and loaded into CS and IP and execution resumes in the ISR. On IRET, CS, IP and FLAGS are popped. IF and TF are set to the state prior to the interrupt. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 4 (April 24, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design & Programming Interrupts I CMPE 310 Real and Protected Mode Interrupts The return address (CS/IP) is pushed onto the stack during the interrupt. The return address can point to: The next instruction. The offending (current) instruction. The latter case occurs for interrupts 0, 5, 6, 7, 8, 10, 11, 12 and 13. This makes it possible to try the instruction again. Protected Mode: The same interrupt assignments are made and the same sequence of opera- tions occurs in protected mode but the interrupt table is different. Instead, 256 interrupt descriptors are used in the interrupt descriptor table (IDT). Present 00H Offset (A31-A16) PDPL 01110 Offset (A15-A0) Segment Selector 7 6 5 4 3 2 1 0 L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 5 (April 24, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design & Programming Interrupts I CMPE 310 Hardware Interrupts The INTR pin must be externally decoded to select a vector. Any vector is possible, but the interrupt vectors between 20H and FFH are usually used (Intel reserves vectors between 00H and 1FH). INTA is an output of the microprocessor to signal the external decoder to place the interrupt number on data bus connections D7-D0. The INTR pin is set by an external device (8259A) and cleared in the ISR. The input is automatically disabled by the microprocessor once it is rec- ognized and re-enabled by IRET or IRETD instruction. Timing diagram of the handshake. INTR LOCK INTA D7-D0 Vector number L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 6 (April 24, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design & Programming Interrupts I CMPE 310 Hardware Interrupts Simpliest method of generating an interrupt vector: VCC Always generates interrupt vector FFH in response to INTR. 27K D 0 D 1 D 2 Low data D 3 D 4 bus D 5 D 6 D 7 no connection INTA L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 7 (April 24, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design & Programming Interrupts I CMPE 310 Tri-state Buffer for Generating the Interrupt Vector D 0 D 1 D 2 Low data D 3 D 4 bus D 5 D 6 Applies interrupt D 7 vector 80H in Y 1 ... response to INTA. 74ALS244 A 1 ... GG V CC INTA L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 8 (April 24, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design & Programming Interrupts I CMPE 310 An Example 82C55 Interrupt Configuration 8 82C55 D 7 -- D 0 A 0 D 0 D 0 Y 1 ... ASCII A 1 ... GG D 7 A 7 D 7 B 0 Keyboard IORC RD WR DAV A 0 A 0 A 1 A 1 B 7 Reset Reset C 0 INTA Wait2 STB CS IOWC I 1 A 0 O 1 C 7 A 3 A 4 A 15 A 5 A 14 A 6 A 13 A 7 A 12 A 8 A 11 A 9 O 8 I 10 A 10 16L8 INTR L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 9 (April 24, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design & Programming Interrupts I CMPE 310 Handling more than 1 IRQ D 0 IRQs D 1 6 5 4 3 2 1 0 Vect D 2 D 3 1 1 1 1 1 1 0 FEH D 4 1 1 1 1 1 0 1 FDH D 5 1 1 1 1 0 1 1 FBH D 6 D 7 1 1 1 0 1 1 1 F7H V CC 1 1 0 1 1 1 1 EFH Y 1 ... 1 0 1 1 1 1 1 DFH 74ALS244 A 1 ... GG 0 1 1 1 1 1 1 BFH INTA IRQ 0 INTR IRQ 6 If any of IRQ x goes low, the NAND goes low requesting an interrupt. Note that if more than one IRQ goes low, a unique interrupt vector is gener- ated and an interrupt priority needs to be defined. The Interrupt Vector table must be expanded to accommodate this. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 10 (April 24, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design & Programming Interrupts I CMPE 310 Daisy-Chained Mechanism for Multiple IRQs A 0 D 0 Only one interrupt vector 82C55 required. A 7 D 7 The scheme given earlier B 0 RD that pulls the bus high (FFH) WR can be used as the vector. B 7 A 0 A 1 C 0 Reset CS 74ALS32 C 7 A 0 D 0 82C55 A 7 D 7 B 0 RD WR Priority is determined in B 7 A 0 the ISR through polling A 1 C 0 the individual 82C55s. Reset CS 74ALS32 C 7 L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 11 (April 24, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design & Programming Interrupts I CMPE 310 8259A Programmable Interrupt Controller The 8259A adds 8 vectored priority encoded interrupts to the microprocessor. It can be expanded to 64 interrupt requests by using one master 8259A and 8 slave units. D0 IR0 D1 IR1 Connect either to devices 8259A Bidirectional. D2 IR2 or to upstream slave 8259As Connect to any D3 IR3 8-bit bank. D4 IR4 D5 IR5 D6 IR6 D7 IR7 A0 CS RD WR CAS0 SP/EN CAS1 INT CAS2 INTA CS and WR must be decoded. Other connections are direct to micro. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 12 (April 24, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design & Programming Interrupts I CMPE 310 8259A Programmable Interrupt Controller The meaning of the other connections: WR Connects to a write strobe signal (one of 8 for the Pentium). RD Connects to the IORC signal. INT Connects to the INTR pin on the microprocessor. INTA Connects to the INTA pin on the microprocessor. A0 Selects different command words in the 8259A. CS Chip select - enables the 8259A for programming and control. SP/EN Slave Program (1 for master, 0 for slave)/Enable Buffer (controls the data bus transievers when in buffered mode). CAS2-CAS0 Used as outputs from the master to the slaves in cascaded systems. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 13 (April 24, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Recommend

More recommend