UMBC A B M A L T F O U M B C I M Y O R T 1 (Mar. - PowerPoint PPT Presentation

Systems Design & Programming Memory III CMPE 310 8086 - 80386SX 16-bit Memory Interface These machines differ from the 8088/80188 in several ways: The data bus is 16-bits wide. The IO/M pin is replaced with M/IO (8086/80186) and

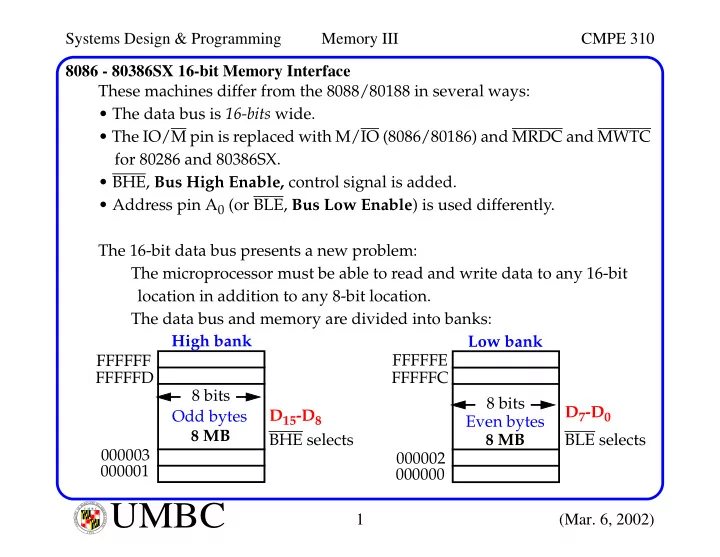

Systems Design & Programming Memory III CMPE 310 8086 - 80386SX 16-bit Memory Interface These machines differ from the 8088/80188 in several ways: • The data bus is 16-bits wide. • The IO/M pin is replaced with M/IO (8086/80186) and MRDC and MWTC for 80286 and 80386SX. • BHE, Bus High Enable, control signal is added. • Address pin A 0 (or BLE, Bus Low Enable ) is used differently. The 16-bit data bus presents a new problem: The microprocessor must be able to read and write data to any 16-bit location in addition to any 8-bit location. The data bus and memory are divided into banks: High bank Low bank FFFFFE FFFFFF FFFFFD FFFFFC 8 bits 8 bits D 7 -D 0 D 15 -D 8 Odd bytes Even bytes 8 MB BHE selects 8 MB BLE selects 000003 000002 000001 000000 L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 1 (Mar. 6, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design & Programming Memory III CMPE 310 8086 - 80386SX 16-bit Memory Interface BHE and BLE are used to select one or both: BHE BLE Function 0 0 Both banks enabled for 16-bit transfer 0 1 High bank enabled for an 8-bit transfer 1 0 Low bank enabled for an 8-bit transfer 1 1 No banks selected Bank selection can be accomplished in two ways: Separate write decoders for each bank (which drive CS). A separate write signal (strobe) to each bank (which drive WE). Note that 8-bit read requests in this scheme are handled by the micropro- cessor (it selects the bits it wants to read from the 16-bits on the bus). There does not seem to be a big difference between these methods although the book claims that there is. Note in either method that A 0 does not connect to memory and bus wire A 1 connects to memory pin A 0 , A 2 to A 1 , etc. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 2 (Mar. 6, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design & Programming Memory III CMPE 310 80386SX 16-bit Memory Interface (Separate Decoders) A 0 O 0 A 1 to A 16 Address Bus D 8 to D 15 ... ... A 15 O 7 MWTC WE A 17 OE 74LS138 A CS A 18 0 3 62512 B 1 CS A 19 C 2 (64K X 8) CS 3 CS BHE 4 Separate Decoders G1 5 CS A 20 6 G2A CS A 80386SX 7 74LS138 A 21 0 G2B CS B 1 A 22 CS 2 A 0 C O 0 3 D 0 to D 7 ... ... 4 A 15 O 7 G1 A 23 5 WE G2A 6 OE Data Bus 7 G2B 74LS138 A CS 0 B 1 62512 CS C 2 MRDC (64K X 8) CS 3 M/IO CS 4 G1 5 CS BLE G2A 6 CS 7 G2B CS CS L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 3 (Mar. 6, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design & Programming Memory III CMPE 310 Memory Interfaces See text for Separate Write Strobe scheme plus some examples of the integra- tion of EPROM and SRAM in a complete system. It is just an application of what we’ve been covering. 80386DX and 80486 have 32-bit data buses and therefore 4 banks of memory. 32-bit , 16-bit and 8-bit transfers are accomplished by different combina- tions of the bank selection signals BE3, BE2, BE1, BE0. The Address bits A 0 and A 1 are used within the microprocessor to gener- ate these signals. They are don’t cares in the decoding of the 32-bit address outside the chip (using a PLD such as the PAL 16L8 ). The high clock rates of these processors usually require wait states for memory access. We will come back to this later. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 4 (Mar. 6, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design & Programming Memory III CMPE 310 Pentium Memory Interface The Pentium, Pentium Pro, Pentium II and III contain a 64-bit data bus. Therefore, 8 decoders or 8 write strobes are needed as well as 8 memory banks. The write strobes are obtained by combining the bank enable signals (BEx) with the MWTC signal. MWTC is generated by combining the M/IO and W/R signals. BE7 WR7 BE6 WR6 BE5 WR5 BE4 W/R WR4 MWTC BE3 M/IO WR3 BE2 WR2 BE1 WR1 BE0 WR0 L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 5 (Mar. 6, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design & Programming Memory III CMPE 310 Pentium Memory Interface A3-A18 WR0 WR1 WR2 D 15 -D 23 WR3 D 24 -D 31 D 8 -D 15 D 0 -D 7 A29 I1 A 0 O 0 A 0 O 0 A 0 O 0 A30 O1 O 0 A 0 I2 ... ... ... ... ... ... A31 ... O2 ... I3 A 15 A 15 A 15 O 7 O 7 O 7 A 15 O 7 O3 I4 16L8 (64K X 8) I5 O4 27512 27512 27512 27512 I6 WE WE WE WE O5 I7 O6 CE CE CE CE I8 O7 OE OE OE I9 OE O8 I10 A19 I1 A20 O1 I2 A 0 O 0 A 0 O 0 A 0 O 0 A 0 O 0 A21 O2 I3 ... ... ... ... ... ... ... ... A22 O3 D 56 -D 63 I4 D 32 -D 39 D 40 -D 47 D 48 -D 55 A 15 A 15 A 15 A 15 O 7 O 7 O 7 O 7 A23 16L8 I5 O4 A24 I6 O5 27512 27512 27512 27512 A25 WE WE WE WE I7 O6 A26 I8 CE CE CE CE O7 A27 I9 O8 A28 OE OE OE OE I10 WR7 WR4 WR5 WR6 MRDC L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 6 (Mar. 6, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design & Programming Memory III CMPE 310 Pentium Memory Interface In order to map previous memory into addr. space FFF80000H - FFFFFFFFH A29 I1 A30 O1 ; pins 1 2 3 4 5 6 7 8 9 10 I2 A31 O2 A29 A30 A31 NC NC NC NC NC NC GND I3 O3 I4 ; pins 11 12 13 14 15 16 17 18 19 20 16L8 I5 O4 U2 CE NC NC NC NC NC NC NC VCC I6 O5 I7 O6 Equations : I8 O7 I9 /CE = /U2 * A29 * A30 * A31 O8 I10 A19 I1 A20 O1 ; pins 1 2 3 4 5 6 7 8 9 10 I2 A21 O2 I3 A19 A20 A21 A22 A23 A24 A25 A26 A27 GND A22 O3 I4 A23 16L8 ; pins 11 12 13 14 15 16 17 18 19 20 I5 O4 A24 A28 U2 NC NC NC NC NC NC NC VCC I6 O5 A25 I7 O6 A26 I8 Equations : O7 A27 I9 O8 A28 /U2 = A19 * A20 * A21 * A22 * A23 * A24 * A25 * I10 A26 * A27 * A28 Use a 16L8 to do the WR0 - WR7 decoding using MWTC and BE0 - BE7. See the text -- Figure 10-35. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 7 (Mar. 6, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design & Programming Memory III CMPE 310 Memory Architecture In order to build an N-word memory where each word is M bits wide (typi- cally 1, 4 or 8 bits), a straightforward approach is to stack memory: A word is selected by setting exactly S 0 one of the select bits, S x , high. Word 0 S 1 Word 1 S 2 Storage cell Word 2 N words This approach works well for small memories but has problems for large memories. S N-2 Word N-2 For example, to build a 1Mword S N-1 Word N-1 (where word = 8 bits) memory, requires 1M select lines, provided by some off-chip device. Input-Output (M bits) This approach is not practical. What can we do? L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 8 (Mar. 6, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design & Programming Memory III CMPE 310 Memory Architecture Add a decoder to solve the package problem: S 0 Binary encoded address Word 0 S 1 Word 1 A 0 S 2 Storage cell Word 2 A 1 Decoder A 2 This reduces the A K-1 number of external address pins from S N-2 Word N-2 1M to 20. S N-1 Word N-1 K = log 2 N Input-Output one-hot (M bits) This does not address the memory aspect ratio problem: The memory is 128,000 time higher than wide (2 20 /2 3 ) ! Besides the bizarre shape factor, the design is extremely slow since the ver- tical wires are VERY long (delay is at least linear to length). L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 9 (Mar. 6, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design & Programming Memory III CMPE 310 Memory Architecture The vertical and horizontal dimensions are usually very similar, for an aspect ratio of unity . Multiple words are stored in each row and selected simultaneously: Bit line S 0 Row address = Storage cell A K to A L-1 S 1 A K S 2 Row Decoder A K+1 A K+2 Word line A L-1 S N-2 S N-1 Column address = A 0 to A K-1 A 0 Sense amps Column decoder A K-1 and drivers not shown A column decoder is added to Input-Output select the desired word from a row. (M bits) L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 10 (Mar. 6, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design & Programming Memory III CMPE 310 Memory Architecture This strategy works well for memories up to 64 Kbits to 256 Kbits. Larger memories start to suffer excess delay along bit and word lines. A third dimension is added to the address space to solve this problem: Block 0 Block i Block P-1 Row Address Column Address Block Block selector Address Global Data bus Global Address: [ Row ][ Block ][ Col ] amplifier/driver I/O L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 11 (Mar. 6, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.