Topics Old bus standards disappear (ISA), or are slowly fading - PDF document

What we Need to Make I/O Work? Lecture 7: I/O and Exceptions A way to connect many types of Devices to the Proc-Mem Topics Old bus standards disappear (ISA), or are slowly fading away (USB 1, parallel printer, AGP) , while new are

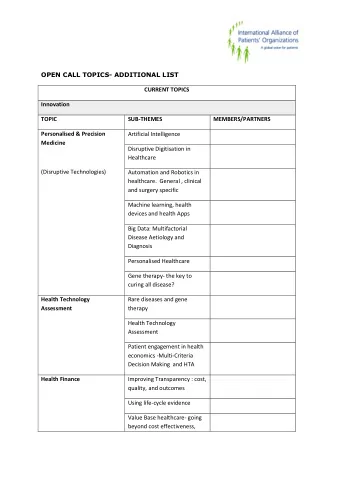

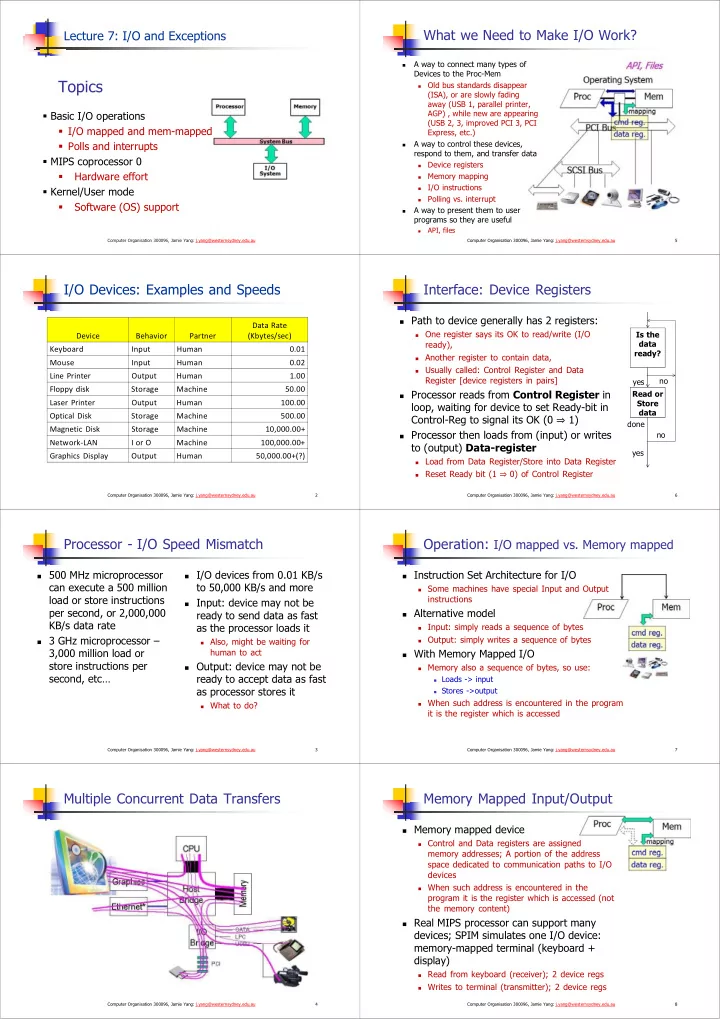

What we Need to Make I/O Work? Lecture 7: I/O and Exceptions A way to connect many types of Devices to the Proc-Mem Topics Old bus standards disappear (ISA), or are slowly fading away (USB 1, parallel printer, AGP) , while new are appearing Basic I/O operations (USB 2, 3, improved PCI 3, PCI I/O mapped and mem-mapped Express, etc.) A way to control these devices, Polls and interrupts respond to them, and transfer data MIPS coprocessor 0 Device registers Hardware effort Memory mapping I/O instructions Kernel/User mode Polling vs. interrupt Software (OS) support A way to present them to user programs so they are useful API, files Computer Organisation 300096, Jamie Yang: j.yang@westernsydney.edu.au Computer Organisation 300096, Jamie Yang: j.yang@westernsydney.edu.au 5 I/O Devices: Examples and Speeds Interface: Device Registers Path to device generally has 2 registers: Data Rate One register says its OK to read/write (I/O Is the Device Behavior Partner (Kbytes/sec) ready), data Keyboard Input Human 0.01 ready? Another register to contain data, Mouse Input Human 0.02 Usually called: Control Register and Data Line Printer Output Human 1.00 Register [device registers in pairs] no yes Floppy disk Storage Machine 50.00 Processor reads from Control Register in Read or Laser Printer Output Human 100.00 Store loop, waiting for device to set Ready-bit in data Optical Disk Storage Machine 500.00 Control-Reg to signal its OK (0 1) done Magnetic Disk Storage Machine 10,000.00+ Processor then loads from (input) or writes no Network‐LAN I or O Machine 100,000.00+ to (output) Data-register yes Graphics Display Output Human 50,000.00+(?) Load from Data Register/Store into Data Register Reset Ready bit (1 0) of Control Register Computer Organisation 300096, Jamie Yang: j.yang@westernsydney.edu.au 2 Computer Organisation 300096, Jamie Yang: j.yang@westernsydney.edu.au 6 Processor - I/O Speed Mismatch Operation: I/O mapped vs. Memory mapped 500 MHz microprocessor I/O devices from 0.01 KB/s Instruction Set Architecture for I/O can execute a 500 million to 50,000 KB/s and more Some machines have special Input and Output load or store instructions instructions Input: device may not be per second, or 2,000,000 Alternative model ready to send data as fast KB/s data rate as the processor loads it Input: simply reads a sequence of bytes 3 GHz microprocessor – Output: simply writes a sequence of bytes Also, might be waiting for 3,000 million load or human to act With Memory Mapped I/O store instructions per Output: device may not be Memory also a sequence of bytes, so use: second, etc… ready to accept data as fast Loads -> input as processor stores it Stores ->output When such address is encountered in the program What to do? it is the register which is accessed Computer Organisation 300096, Jamie Yang: j.yang@westernsydney.edu.au 3 Computer Organisation 300096, Jamie Yang: j.yang@westernsydney.edu.au 7 Multiple Concurrent Data Transfers Memory Mapped Input/Output Memory mapped device Control and Data registers are assigned memory addresses; A portion of the address space dedicated to communication paths to I/O devices When such address is encountered in the program it is the register which is accessed (not the memory content) Real MIPS processor can support many devices; SPIM simulates one I/O device: memory-mapped terminal (keyboard + display) Read from keyboard (receiver); 2 device regs Writes to terminal (transmitter); 2 device regs Computer Organisation 300096, Jamie Yang: j.yang@westernsydney.edu.au 4 Computer Organisation 300096, Jamie Yang: j.yang@westernsydney.edu.au 8

Performance: Cost of Polling? Memory Mapped I/O: SPIM I/O Simulation Certain addresses are not regular memory Assume for a processor with a 1 GHz clock , it takes 400 clock cycles for a polling operation (call polling Instead: they correspond to registers in I/O devices routine, accessing the device, and returning). Determine 0xffffffff control reg. % of processor time for polling. data reg. 0xffff0000 Mouse Polled 30 times/second (polling frequency) so as not to miss user movement Receiver Control reg Floppy disk Transfers data in 2-byte units ( 2-bytes/poll ) and has a mapped to 0xffff0000 data rate of 50 KB/second . No data transfer can be missed. Receiver Data reg mapped to 0xffff0004 Hard disk Transfers data in 16-byte chunks ( 16-bytes/poll ) and can Address 0 transfer at 16 MB/second (data rate). Again, no transfer Transmitter Ctrl reg mapped to 0xffff0008 can be missed. Transmitter Data reg mapped to 0xffff000c Computer Organisation 300096, Jamie Yang: j.yang@westernsydney.edu.au 9 Computer Organisation 300096, Jamie Yang: j.yang@westernsydney.edu.au 13 % of processor time for polling Memory Mapped I/O: SPIM I/O Simulation Control register rightmost bit (bit-0): Ready Mouse Polling In clocks/sec : 30 [polls/sec] * 400 [clocks/poll] = 12000 clocks/sec It cannot be changed by processor (just like $0) % Processor for polling: Receiver : Ready==1 means character in Data Register arrived 12*10 3 (clocks/sec) / 1*10 9 [clocks/sec] = 0.0012% but not yet been read; Polling mouse little impact on processor 1 0 when data is read from Data Register Transmitter : Ready==1 means transmitter is ready to accept a new character; Hard Disk Polling 0 Transmitter still busy writing last char Polling frequency (polls/sec) = 16 [MB/s] /16 [Bytes/poll] = 1M polls/sec Data register rightmost byte has data In clocks/sec: 1M * 400 = 400,000,000 clocks/sec Receiver : last char from keyboard; rest = 0 % Processor for polling: 40*10 7 /1*10 9 = 40% Transmitter : when rightmost byte written, writes character to At 40% processor time cost? Definitely NOT acceptable! display Computer Organisation 300096, Jamie Yang: j.yang@westernsydney.edu.au 10 Computer Organisation 300096, Jamie Yang: j.yang@westernsydney.edu.au 14 Polling (or programmed I/O): What is the alternative to polling? Processor Checks Status before Acting Processor reads from mapped Wasteful to have processor spend most of its time busy wait loop; Control Reg in loop, waiting for Is the “spinwaiting” for I/O to be ready not an efficient device to set Ready-bit in Control data way to use the CPU Wish we could have an unplanned (un-programmed) procedure Reg to signal its OK (0 1) ready? unless the device call that would be invoked only when I/O device is ready… Processor then loads from (input) is very fast! Use exception mechanism (as in arithmetic overflow)! or writes to (output) mapped no yes Data Reg interrupt program when I/O ready, Read or Reset Ready bit (1 0) of return when done with data transfer Store checks for I/O Control Register data An I/O interrupt is just like the exceptions except: completion can be Advantage: done dispersed among More information needs to be transferred no Simple: processor is totally in computation An I/O interrupt is asynchronous with respect to instruction control and does all intensive code execution yes Disadvantage: It does not prevent any instruction from completion Polling overhead can consume Pick convenient point to take an interrupt, let the current a lot of CPU time instruction complete Computer Organisation 300096, Jamie Yang: j.yang@westernsydney.edu.au 11 Computer Organisation 300096, Jamie Yang: j.yang@westernsydney.edu.au 15 Interrupt-Driven I/O Implementation: I/O Polling Example Memory Input: Read from keyboard into $v0 (1) I/O add interrupt lui $t0,0xffff # ffff0000 sub user Waitloop1: lw $t1, 0 ($t0) # receiver control program and andi $t1,$t1,0x0001 (2) Save PC or beq $t1,$zero,Waitloop1 lw $v0, 4 ($t0) # receiver data Output: Write to display from $a0 (3) Interrupt service address lui $t0,0xffff # ffff0000 Waitloop2: lw $t1, 8 ($t0) # transmitter control andi $t1,$t1,0x0001 (4) read beq $t1,$zero,Waitloop2 interrupt store sw $a0, 12 ($t0) # transmitter data service … Processor waiting for I/O called “Polling” routine (5) jr Computer Organisation 300096, Jamie Yang: j.yang@westernsydney.edu.au 12 Computer Organisation 300096, Jamie Yang: j.yang@westernsydney.edu.au 16

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.