Techniques et outils pour la vrification de systmes-sur-puces au - PowerPoint PPT Presentation

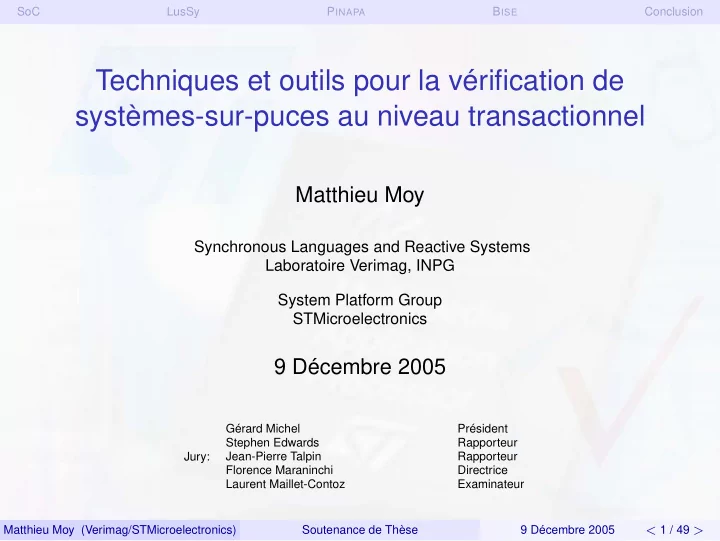

SoC LusSy P INAPA B ISE Conclusion Techniques et outils pour la vrification de systmes-sur-puces au niveau transactionnel Matthieu Moy Synchronous Languages and Reactive Systems Laboratoire Verimag, INPG System Platform Group

SoC LusSy P INAPA B ISE Conclusion Transaction Level Modeling in SystemC SystemC provides the building blocks, but no high-level bus model Additional components are needed for TLM channels Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 15 / 49 >

SoC LusSy P INAPA B ISE Conclusion Transaction Level Modeling in SystemC SystemC provides the building blocks, but no high-level bus model Additional components are needed for TLM channels STMicroelectronics developed several bus models ◮ BASIC: an example channel ◮ TAC: a TLM channel used in production Will hopefully be standardized Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 15 / 49 >

SoC LusSy P INAPA B ISE Conclusion Execution of a SystemC Program Architecture and Behavior ◮ No specific architecture description language ◮ Arbitrary C++ can be used for both aspects Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 16 / 49 >

SoC LusSy P INAPA B ISE Conclusion Execution of a SystemC Program Architecture and Behavior ◮ No specific architecture description language ◮ Arbitrary C++ can be used for both aspects Elaboration phase ◮ Instantiate the components ◮ Bind them together Simulation ◮ Run the processes one by one ◮ With a fixed architecture Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 16 / 49 >

SoC LusSy P INAPA B ISE Conclusion An Example TLM Model in SystemC Components CPU RAM ... if (p.read()) { ... } Interrupt signal Ports Abstract channel TAC channel bool var; ... var = true; ... port.write(var); C++ code ... + SystemC IC ROM Processes constructs Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 17 / 49 >

SoC LusSy P INAPA B ISE Conclusion Elaboration Phase: Build Architecture int sc_main(int argc, char ** argv) { irq_controler * ic = new irq_controler("IRQ"); cpu * cpu = new cpu("CPU0"); ram * ram = new ram("INT_RAM"); rom * rom = new rom("ROM"); tac_channel * channel = new tac_channel("CHANNEL"); sc_signal<bool> sig; cpu->master_port.bind(channel->slave_port); ic->slave_port.bind(channel->master_port); ram->slave_port.bind(channel->master_port); rom->slave_port.bind(channel->master_port); ic->port.bind(sig); cpu->p.bind(sig); sc_start(); } Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 18 / 49 >

SoC LusSy P INAPA B ISE Conclusion Elaboration Phase: Build Architecture // Main function int sc_main(int argc, char ** argv) { irq_controler * ic = new irq_controler("IRQ"); cpu * cpu = new cpu("CPU0"); ram * ram = new ram("INT_RAM"); rom * rom = new rom("ROM"); tac_channel * channel = new tac_channel("CHANNEL"); sc_signal<bool> sig; cpu->master_port.bind(channel->slave_port); ic->slave_port.bind(channel->master_port); ram->slave_port.bind(channel->master_port); rom->slave_port.bind(channel->master_port); ic->port.bind(sig); cpu->p.bind(sig); sc_start(); } Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 18 / 49 >

SoC LusSy P INAPA B ISE Conclusion Elaboration Phase: Build Architecture int sc_main(int argc, char ** argv) { // Components Instantiation (creation of C++ objects) irq_controler * ic = new irq_controler("IRQ"); cpu * cpu = new cpu("CPU0"); ram * ram = new ram("INT_RAM"); rom * rom = new rom("ROM"); tac_channel * channel = new tac_channel("CHANNEL"); sc_signal<bool> sig; cpu->master_port.bind(channel->slave_port); ic->slave_port.bind(channel->master_port); ram->slave_port.bind(channel->master_port); rom->slave_port.bind(channel->master_port); ic->port.bind(sig); cpu->p.bind(sig); sc_start(); } Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 18 / 49 >

SoC LusSy P INAPA B ISE Conclusion Elaboration Phase: Build Architecture int sc_main(int argc, char ** argv) { irq_controler * ic = new irq_controler("IRQ"); cpu * cpu = new cpu("CPU0"); ram * ram = new ram("INT_RAM"); rom * rom = new rom("ROM"); tac_channel * channel = new tac_channel("CHANNEL"); sc_signal<bool> sig; // Binding (link between objects) cpu->master_port.bind(channel->slave_port); ic->slave_port.bind(channel->master_port); ram->slave_port.bind(channel->master_port); rom->slave_port.bind(channel->master_port); ic->port.bind(sig); cpu->p.bind(sig); sc_start(); } Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 18 / 49 >

SoC LusSy P INAPA B ISE Conclusion Elaboration Phase: Build Architecture int sc_main(int argc, char ** argv) { irq_controler * ic = new irq_controler("IRQ"); cpu * cpu = new cpu("CPU0"); ram * ram = new ram("INT_RAM"); rom * rom = new rom("ROM"); tac_channel * channel = new tac_channel("CHANNEL"); sc_signal<bool> sig; cpu->master_port.bind(channel->slave_port); ic->slave_port.bind(channel->master_port); ram->slave_port.bind(channel->master_port); rom->slave_port.bind(channel->master_port); ic->port.bind(sig); cpu->p.bind(sig); // Start simulation (let the kernel execute processes) sc_start(); } Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 18 / 49 >

SoC LusSy P INAPA B ISE Conclusion Outline Context: Embedded Systems and Systems-on-a-Chip 1 L US S Y : A Toolbox for the Analysis of Systems-on-a-Chip at the 2 Transaction Level P INAPA : Syntax and Architecture Extraction 3 B ISE : Semantic Extraction 4 Conclusion 5 Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 19 / 49 >

SoC LusSy P INAPA B ISE Conclusion Importance of TLM in the design flow No automatic synthesis from TLM to RTL A complement for RTL (not a replacement) Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 20 / 49 >

SoC LusSy P INAPA B ISE Conclusion Importance of TLM in the design flow No automatic synthesis from TLM to RTL A complement for RTL (not a replacement) TLM serves as a reference model for RTL validation Embedded software is developed and tested partly on the TLM model Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 20 / 49 >

SoC LusSy P INAPA B ISE Conclusion Importance of TLM in the design flow No automatic synthesis from TLM to RTL A complement for RTL (not a replacement) TLM serves as a reference model for RTL validation Embedded software is developed and tested partly on the TLM model ⇒ Although TLM models are not embedded in the chip, their validation is important Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 20 / 49 >

SoC LusSy P INAPA B ISE Conclusion State of the Art Semantics of SystemC ◮ Several papers for a semantics of RTL SystemC (very strict subset) ◮ Usually do not take into account the real semantics of the scheduler Verification of TLM models ◮ Recent research area ◮ Almost nothing relevant when we started Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 21 / 49 >

SoC LusSy P INAPA B ISE Conclusion State of the Art Semantics of SystemC ◮ Several papers for a semantics of RTL SystemC (very strict subset) ◮ Usually do not take into account the real semantics of the scheduler Verification of TLM models ◮ Recent research area ◮ Almost nothing relevant when we started In the meantime ... ◮ Several tools for SystemC (front-ends, verification, lint, . . . ) ◮ Published work usually target a lower abstraction level than TLM as we use it in STMicroelectronics Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 21 / 49 >

SoC LusSy P INAPA B ISE Conclusion Objectives of the Thesis “Provide a connection from SystemC/TLM to existing verification tools” Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 22 / 49 >

SoC LusSy P INAPA B ISE Conclusion Objectives of the Thesis “Provide a connection from SystemC/TLM to existing verification tools” Main difficulties ◮ TLM mixes hardware and software ⇒ Verification is undecidable ◮ Abstractions will have to be made Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 22 / 49 >

SoC LusSy P INAPA B ISE Conclusion Objectives of the Thesis “Provide a connection from SystemC/TLM to existing verification tools” Main difficulties ◮ TLM mixes hardware and software ⇒ Verification is undecidable ◮ Abstractions will have to be made Main choices ◮ Deal with real SystemC code ◮ Fully automated tool-chain ◮ As few abstractions as possible Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 22 / 49 >

SoC LusSy P INAPA B ISE Conclusion Objectives of the Thesis “Provide a connection from SystemC/TLM to existing verification tools” Main difficulties ◮ TLM mixes hardware and software ⇒ Verification is undecidable ◮ Abstractions will have to be made Main choices ◮ Deal with real SystemC code ◮ Fully automated tool-chain ◮ As few abstractions as possible Consequences ◮ We need a front-end to read the SystemC code ◮ We need a semantics for SystemC ⇒ Formal, Simple, Executable Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 22 / 49 >

SoC LusSy P INAPA B ISE Conclusion Expressing properties Safety properties only (as opposed to liveness) Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 23 / 49 >

SoC LusSy P INAPA B ISE Conclusion Expressing properties Safety properties only (as opposed to liveness) No new specific language Express properties in C++/SystemC ◮ ASSERT(x.read() == true) Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 23 / 49 >

SoC LusSy P INAPA B ISE Conclusion Expressing properties Safety properties only (as opposed to liveness) No new specific language Express properties in C++/SystemC ◮ ASSERT(x.read() == true) Use generic properties (things that you usually don’t want) ◮ Global dead-lock ◮ Multiple write on a sc_signal ◮ Process termination ◮ Mutual exclusion Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 23 / 49 >

SoC LusSy P INAPA B ISE Conclusion The L US S Y Tool Chain SystemC Verification tool Property Transformations Abstract Format Concrete Format External tools/formats (in memory) (file) Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 24 / 49 >

SoC LusSy P INAPA B ISE Conclusion The L US S Y Tool Chain tool-specific SystemC format Verification tool Property Transformations Abstract Format Concrete Format External tools/formats (in memory) (file) Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 24 / 49 >

SoC LusSy P INAPA B ISE Conclusion The L US S Y Tool Chain tool-specific SystemC format Verification Pinapa tool Property Transformations Abstract Format Concrete Format External tools/formats (in memory) (file) Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 24 / 49 >

SoC LusSy P INAPA B ISE Conclusion The L US S Y Tool Chain Abstract tool-specific SystemC SystemC format Verification Pinapa tool Property Transformations Abstract Format Concrete Format External tools/formats (in memory) (file) Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 24 / 49 >

SoC LusSy P INAPA B ISE Conclusion The L US S Y Tool Chain Abstract tool-specific SystemC SystemC format Verification Pinapa Bise tool Property Transformations Abstract Format Concrete Format External tools/formats (in memory) (file) Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 24 / 49 >

SoC LusSy P INAPA B ISE Conclusion The L US S Y Tool Chain Abstract tool-specific SystemC HPIOM SystemC format Verification Pinapa Bise tool Property Transformations Abstract Format Concrete Format External tools/formats (in memory) (file) Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 24 / 49 >

SoC LusSy P INAPA B ISE Conclusion The L US S Y Tool Chain Abstract tool-specific SystemC HPIOM SystemC format Verification Pinapa Bise Back-end tool Property Transformations Abstract Format Concrete Format External tools/formats (in memory) (file) Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 24 / 49 >

SoC LusSy P INAPA B ISE Conclusion The L US S Y Tool Chain Birth Abstract tool-specific SystemC HPIOM SystemC format Verification Pinapa Bise Back-end tool Property Transformations Abstract Format Concrete Format External tools/formats (in memory) (file) Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 24 / 49 >

SoC LusSy P INAPA B ISE Conclusion The L US S Y Tool Chain Birth Abstract tool-specific SystemC HPIOM SystemC format Verification Pinapa Bise Back-end tool Property Transformations Abstract Format Concrete Format External tools/formats (in memory) (file) Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 24 / 49 >

SoC LusSy P INAPA B ISE Conclusion The L US S Y Tool Chain Birth Lustre SMV Abstract tool-specific SystemC HPIOM SystemC format Verification Pinapa Bise Back-end tool Property Transformations Abstract Format Concrete Format External tools/formats (in memory) (file) Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 24 / 49 >

SoC LusSy P INAPA B ISE Conclusion The L US S Y Tool Chain Birth Lustre SMV Abstract tool-specific SystemC HPIOM SystemC format Verification Pinapa Bise Back-end tool Lesar nbac SMV Property gbac Prover Transformations Abstract Format Concrete Format External tools/formats (in memory) (file) Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 24 / 49 >

SoC LusSy P INAPA B ISE Conclusion The L US S Y Tool Chain Birth Lustre SMV ??? Abstract tool-specific SystemC HPIOM SystemC format Verification Pinapa Bise Back-end tool ??? Lesar nbac SMV Property gbac Prover Transformations Abstract Format Concrete Format External tools/formats (in memory) (file) Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 24 / 49 >

SoC LusSy P INAPA B ISE Conclusion The L US S Y Tool Chain LusSy Birth Lustre SMV ??? Abstract tool-specific SystemC HPIOM SystemC format Verification Pinapa Bise Back-end tool ??? Lesar nbac SMV Property gbac Prover Transformations Abstract Format Concrete Format External tools/formats (in memory) (file) Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 24 / 49 >

SoC LusSy P INAPA B ISE Conclusion Outline Context: Embedded Systems and Systems-on-a-Chip 1 L US S Y : A Toolbox for the Analysis of Systems-on-a-Chip at the 2 Transaction Level P INAPA : Syntax and Architecture Extraction 3 B ISE : Semantic Extraction 4 Conclusion 5 Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 25 / 49 >

SoC LusSy P INAPA B ISE Conclusion P INAPA : P inapa I s N ot A PA rser Birth Abstract tool-specific SystemC HPIOM SystemC format Verification Pinapa Bise Back-end tool Property Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 26 / 49 >

SoC LusSy P INAPA B ISE Conclusion Main Choices There are many ways to “parse” SystemC: Write a grammar from scratch ⇒ Needs to take all the C++ grammar into account! Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 27 / 49 >

SoC LusSy P INAPA B ISE Conclusion Main Choices There are many ways to “parse” SystemC: Write a grammar from scratch ⇒ Needs to take all the C++ grammar into account! Use a C++ front-end, and nothing else ⇒ Misses important information like architecture, built at run-time Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 27 / 49 >

SoC LusSy P INAPA B ISE Conclusion Main Choices There are many ways to “parse” SystemC: Write a grammar from scratch ⇒ Needs to take all the C++ grammar into account! Use a C++ front-end, and nothing else ⇒ Misses important information like architecture, built at run-time Use a C++ front-end, and recognize patterns in the elaboration phase ⇒ Big limitation on the coding style of the elaboration Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 27 / 49 >

SoC LusSy P INAPA B ISE Conclusion Main Choices There are many ways to “parse” SystemC: Write a grammar from scratch ⇒ Needs to take all the C++ grammar into account! Use a C++ front-end, and nothing else ⇒ Misses important information like architecture, built at run-time Use a C++ front-end, and recognize patterns in the elaboration phase ⇒ Big limitation on the coding style of the elaboration Use a C++ front-end, and execute the elaboration phase to get the architecture ⇒ Much less limitation, lot of code reuse Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 27 / 49 >

SoC LusSy P INAPA B ISE Conclusion Main Choices There are many ways to “parse” SystemC: Write a grammar from scratch ⇒ Needs to take all the C++ grammar into account! ParSyC, SystemPerl, sc2v, KaSCPar Use a C++ front-end, and nothing else ⇒ Misses important information like architecture, built at run-time Use a C++ front-end, and recognize patterns in the elaboration phase ⇒ Big limitation on the coding style of the elaboration SystemCXML, CoCentric Use a C++ front-end, and execute the elaboration phase to get the architecture ⇒ Much less limitation, lot of code reuse Approach chosen for P INAPA Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 27 / 49 >

SoC LusSy P INAPA B ISE Conclusion Static Vs Dynamic Information in SystemC Programs Information C++ compiler Pinapa in SystemC Static Dynamic Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 28 / 49 >

SoC LusSy P INAPA B ISE Conclusion Static Vs Dynamic Information in SystemC Programs Information C++ compiler Pinapa in SystemC Static Lexicography Syntax Dynamic Architecture Behavior Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 28 / 49 >

SoC LusSy P INAPA B ISE Conclusion Static Vs Dynamic Information in SystemC Programs Information C++ compiler Pinapa in SystemC Static Abstract Syntax Lexicography Tree Syntax (AST) Dynamic Execution Architecture Elaboration Behavior Simulation Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 28 / 49 >

SoC LusSy P INAPA B ISE Conclusion Static Vs Dynamic Information in SystemC Programs Information C++ compiler Pinapa in SystemC Static Abstract Syntax Lexicography Tree Syntax (AST) Dynamic Execution Architecture Elaboration Behavior Simulation Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 28 / 49 >

SoC LusSy P INAPA B ISE Conclusion Static Vs Dynamic Information in SystemC Programs Information C++ compiler Pinapa in SystemC Static Abstract Syntax Lexicography AST Tree Syntax + (AST) ELAB Dynamic Execution Architecture Elaboration Behavior Simulation Simulation Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 28 / 49 >

SoC LusSy P INAPA B ISE Conclusion Static Vs Dynamic Information in SystemC Programs Information C++ compiler Pinapa in SystemC Output of Pinapa Static Abstract Syntax Lexicography AST Tree Syntax + (AST) ELAB Dynamic Execution Architecture Elaboration Behavior Simulation Simulation Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 28 / 49 >

SoC LusSy P INAPA B ISE Conclusion P INAPA : Key Ideas Syntax extraction (AST) ◮ Easy if you have a C++ parser ◮ ⇒ Let’s reuse GCC Architecture extraction (ELAB) ◮ Architecture is built at run-time ◮ ⇒ Let’s execute the elaboration of the program Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 29 / 49 >

SoC LusSy P INAPA B ISE Conclusion P INAPA : Key Ideas Syntax extraction (AST) ◮ Easy if you have a C++ parser ◮ ⇒ Let’s reuse GCC Architecture extraction (ELAB) ◮ Architecture is built at run-time ◮ ⇒ Let’s execute the elaboration of the program Then, what’s difficult?? Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 29 / 49 >

SoC LusSy P INAPA B ISE Conclusion P INAPA : Key Ideas Syntax extraction (AST) ◮ Easy if you have a C++ parser ◮ ⇒ Let’s reuse GCC Architecture extraction (ELAB) ◮ Architecture is built at run-time ◮ ⇒ Let’s execute the elaboration of the program We have to link the syntax and architecture information Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 29 / 49 >

SoC LusSy P INAPA B ISE Conclusion Link Between ELAB and AST ELAB Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 30 / 49 >

SoC LusSy P INAPA B ISE Conclusion Link Between ELAB and AST ELAB AST Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 30 / 49 >

SoC LusSy P INAPA B ISE Conclusion Link Between ELAB and AST ELAB AST Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 30 / 49 >

SoC LusSy P INAPA B ISE Conclusion Link Between ELAB and AST ELAB AST p.read() port.write(val) Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 30 / 49 >

SoC LusSy P INAPA B ISE Conclusion Link Between ELAB and AST: an Example port.write(val); Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 31 / 49 >

SoC LusSy P INAPA B ISE Conclusion Link Between ELAB and AST: an Example port.write(val); write val port Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 31 / 49 >

SoC LusSy P INAPA B ISE Conclusion Link Between ELAB and AST: an Example port.write(val); write val port Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 31 / 49 >

SoC LusSy P INAPA B ISE Conclusion Link Between ELAB and AST: an Example port.write(val); write val port Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 31 / 49 >

SoC LusSy P INAPA B ISE Conclusion Link Between ELAB and AST: an Example port.write(val); write val port Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 31 / 49 >

SoC LusSy P INAPA B ISE Conclusion P INAPA : steps of execution SystemC program Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 32 / 49 >

SoC LusSy P INAPA B ISE Conclusion P INAPA : steps of execution Compilation Executable SystemC program Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 32 / 49 >

SoC LusSy P INAPA B ISE Conclusion P INAPA : steps of execution Compilation Executable Execution SystemC ELAB program Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 32 / 49 >

SoC LusSy P INAPA B ISE Conclusion P INAPA : steps of execution Compilation Executable Execution SystemC ELAB program C++ AST parser Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 32 / 49 >

SoC LusSy P INAPA B ISE Conclusion P INAPA : steps of execution Compilation Executable Execution SystemC ELAB program C++ AST Link parser AST+ELAB Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 32 / 49 >

SoC LusSy P INAPA B ISE Conclusion P INAPA : steps of execution Compilation Executable Execution SystemC ELAB program C++ AST Link parser AST+ELAB Back-end Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 32 / 49 >

SoC LusSy P INAPA B ISE Conclusion Limitations of the Approach No limitation regarding the code of the elaboration Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 33 / 49 >

SoC LusSy P INAPA B ISE Conclusion Limitations of the Approach No limitation regarding the code of the elaboration AST and ELAB built correctly in any case, only link may be problematic. ◮ Dynamic objects (pointers, reference) can hardly be specified with static information ◮ Templates makes the task harder Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 33 / 49 >

SoC LusSy P INAPA B ISE Conclusion Limitations of the Approach No limitation regarding the code of the elaboration AST and ELAB built correctly in any case, only link may be problematic. ◮ Dynamic objects (pointers, reference) can hardly be specified with static information ◮ Templates makes the task harder Much less limitations than other tools Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 33 / 49 >

SoC LusSy P INAPA B ISE Conclusion Conclusion about P INAPA Our approach allowed us to write a SystemC front-end ◮ With very few limitations ◮ Managing the TAC and BASIC channels ◮ With a minimal effort ( < 4000 lines of C++) Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 34 / 49 >

SoC LusSy P INAPA B ISE Conclusion Conclusion about P INAPA Our approach allowed us to write a SystemC front-end ◮ With very few limitations ◮ Managing the TAC and BASIC channels ◮ With a minimal effort ( < 4000 lines of C++) P INAPA is Open Source! ⇒ http://greensocs.sourceforge.net/pinapa/ Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 34 / 49 >

SoC LusSy P INAPA B ISE Conclusion Outline Context: Embedded Systems and Systems-on-a-Chip 1 L US S Y : A Toolbox for the Analysis of Systems-on-a-Chip at the 2 Transaction Level P INAPA : Syntax and Architecture Extraction 3 B ISE : Semantic Extraction 4 Conclusion 5 Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 35 / 49 >

SoC LusSy P INAPA B ISE Conclusion B ISE : B ack-end I ndependent S emantics E xtraction Birth Abstract tool-specific SystemC HPIOM SystemC format Verification Pinapa Bise Back-end tool Property Matthieu Moy (Verimag/STMicroelectronics) Ph.D presentation December 9th, 2005 < 36 / 49 >

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.