Taming complex chip designs with beautiful diagrams Titouan Vervack - PowerPoint PPT Presentation

EclipseCon Europe, Ludwigsburg 2017-10-24 Taming complex chip designs with beautiful diagrams Titouan Vervack redefine.digital.design: Helping you deal with complexity in VHDL and Verilog. Ghent 2 Sigasi 3 What do we do? Eclipse-based VHDL

EclipseCon Europe, Ludwigsburg 2017-10-24 Taming complex chip designs with beautiful diagrams Titouan Vervack redefine.digital.design: Helping you deal with complexity in VHDL and Verilog.

Ghent 2

Sigasi 3

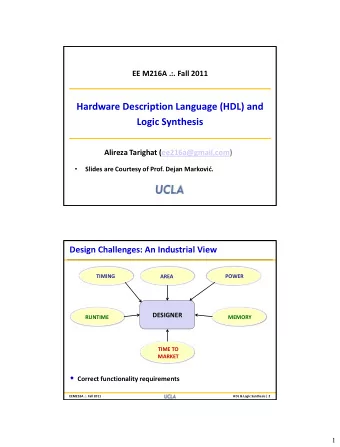

What do we do? Eclipse-based VHDL & SystemVerilog IDE 4

Chip design 5

Chip design 5

Hardware Description Language (HDL) entity and_or_top is Port( A : in bit; -- NAND gate input B : in bit; -- NAND gate input Q : out bit -- NAND gate output ); end and_or_top; architecture Behavioral of and_or_top is begin Q <= A nand B; -- 2 input NAND gate end Behavioral; ● VHDL ● (System)Verilog 6

Graphical editors with HDL HDL code 7

Graphical editors with HDL Generate Graphical HDL code 7

Graphical editors with HDL Generate Compile Warnings & Graphical HDL code Errors 7

Graphical editors with HDL Generate Compile Warnings & Graphical HDL code Errors 7

Graphical editors with HDL ? Generate Compile Warnings & Graphical HDL code Errors 7

Graphical editors with HDL 8

Graphical editors with HDL 9

Graphical editors with HDL ? Generate Compile Warnings & Graphical HDL code Errors 10

Graphical editors with HDL ? Generate Compile Warnings & Graphical HDL code Errors 11

Graphical editors with HDL Navigate Generate Compile Warnings & Graphical view HDL code Errors 12

Graphical View of structure 13

Text-based design with graphical views ELK (Eclipse Layout Kernel) KlighD (Kieler Light Weight Diagrams) Graphviz DOT GEF & Zest 14

Graphical <-> source interaction 15

Graphical <-> source interaction 15

Graphical <-> source interaction 15

Graphical <-> source interaction 15

Graphical <-> source interaction 15

Text-based design with graphical views Perfect solution? ● Cluttered ● Too much detail (e.g. 20MB SVG file) ● No focus 16

Text-based design with graphical views 17

Text-based design with graphical views 18

UI configuration 19

Text-based design with graphical views Goals: ● Filtering ● Mergable ● Reproducible Serializable ● ● Simplify collaboration ● Ability to highlight important parts 20

Our updated view HDL code 21

Our updated view HDL code Navigate C o m p i l e Warnings & Errors 21

Our updated view HDL code Navigate Navigate e t a C r o e m n p e i l e G Warnings & Graphical Errors 21

Our updated view HDL code Navigate Navigate e t a C r o e m n p e i l e G Warnings & Graphical Errors DSL 21

Our updated view HDL code Navigate Navigate e t a C r o e m n p e i l e G Warnings & Graphical Errors DSL 21

Our updated view HDL code Navigate Navigate e t a C r o e m n p e i l e G Warnings & Graphical Compile Errors e t a g i v a N DSL 21

Our updated view HDL code Navigate Navigate e t a C r o e m n p e i l e G Warnings & Graphical Compile Errors Navigate e t a g i G v e a n N e r a t e DSL 21

DSL Separate file: ● Does not taint the original source code ● Multiple views for one source Clocking/reset structure ○ ○ Data flow ● Can be generated (group all wires between blocks) 22

Demo DEMO 23

Testing ● DSL is fully covered ● UI: assume framework works ● SVG export: font size differences are a challenge 24

Testing ● DSL is fully covered ● UI: assume framework works ● SVG export: font size differences are a challenge 25

Testing ● DSL is fully covered ● UI: assume framework works ● SVG export: font size differences are a challenge 26

Conclusion ● Use graphical views, not graphical editors ● One on one projection is often not what you want ● ELK + Xtext + Eclipse 27

Evaluate the Sessions Sign in and vote at eclipsecon.org - 1 0 + 1

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.