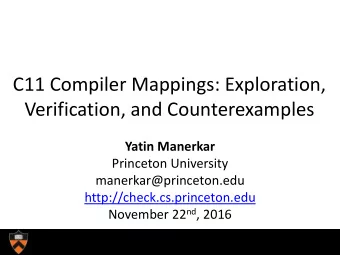

Synthesizing Memory Models from Framework Sketches and Litmus Tests - PowerPoint PPT Presentation

Synthesizing Memory Models from Framework Sketches and Litmus Tests James Bornholt Emina Torlak University of Washington Memory consistency models define memory reordering behaviors on mul>processors Memory consistency models define

Synthesizing Memory Models from Framework Sketches and Litmus Tests James Bornholt Emina Torlak University of Washington

Memory consistency models define memory reordering behaviors on mul>processors

Memory consistency models define memory reordering behaviors on mul>processors …correctness of my compiler… writers Compiler

Memory consistency models define memory reordering behaviors on mul>processors …correctness of …rules to verify my compiler… against… writers Compiler tools 🤗 Verifica@on

Memory consistency models define memory reordering behaviors on mul>processors …correctness of …rules to verify …possible low- my compiler… against… level behaviors… writers Compiler tools 🤗 developers Verifica@on Kernel/library

Memory consistency models define memory reordering behaviors on mul>processors …correctness of …rules to verify …possible low- my compiler… against… level behaviors… writers Compiler tools 🤗 developers Verifica@on Kernel/library Litmus tests and prose

⇒ Memory consistency models define memory reordering behaviors on mul>processors …correctness of …rules to verify …possible low- my compiler… against… level behaviors… writers Compiler tools 🤗 developers Verifica@on Kernel/library ∨ ∀ ⋈ ∃ ∈ ∩ ∧ ⊂ ∪ Litmus tests Formal and prose specifica@ons

⇒ Memory consistency models define memory reordering behaviors on mul>processors …correctness of …rules to verify …possible low- my compiler… against… level behaviors… writers Compiler tools 🤗 developers Verifica@on Kernel/library x86 [Sewell et al, CACM’10] ∨ ∀ ⋈ PowerPC [Alglave et al, CAV’10, etc] ∃ ∈ ∩ ARM [Flur et al, POPL’16] ∧ ⊂ ∪ Litmus tests Formal and prose specifica@ons

⇒ MemSynth ∨ ∀ ⋈ ∃ ∈ ∩ ∧ ⊂ ∪ Litmus tests Formal specifica@ons

⇒ MemSynth Synthesize specifica>ons ∨ ∀ ⋈ ∃ ∈ ∩ ∧ ⊂ ∪ Litmus tests Formal specifica@ons

⇒ MemSynth Framework sketch Synthesize specifica>ons ∨ ∀ ⋈ ∃ ∈ ∩ ∧ ⊂ ∪ Litmus tests Formal specifica@ons

⇒ MemSynth Framework sketch Synthesize specifica>ons ∨ ∀ ⋈ ∃ ∈ ∩ ∧ ⊂ ∪ Detect ambigui>es Litmus tests Formal specifica@ons

⇒ MemSynth Framework sketch Synthesize specifica>ons ∨ ∀ ⋈ ∃ ∈ ∩ ∧ ⊂ ∪ Detect ambigui>es Litmus tests Formal specifica@ons

⇒ MemSynth Synthesize specifica>ons ∨ ∀ ⋈ ∃ ∈ ∩ ∧ ⊂ ∪ Detect ambigui>es

⇒ MemSynth Synthesize specifica>ons ∨ ∀ ⋈ ∃ ∈ ∩ ∧ ⊂ ∪ Detect ambigui>es Framework sketches define a class of memory models

⇒ MemSynth Synthesize specifica>ons ∨ ∀ ⋈ ∃ ∈ ∩ ∧ ⊂ ∪ Detect ambigui>es Framework sketches define a class of memory models MemSynth engine verifica@on, equivalence, synthesis, ambiguity

⇒ MemSynth Synthesize specifica>ons ∨ ∀ ⋈ ∃ ∈ ∩ ∧ ⊂ ∪ Detect ambigui>es Framework sketches define a class of memory models MemSynth engine verifica@on, equivalence, synthesis, ambiguity Results synthesize real-world memory model specs

Memory models and framework sketches

Litmus tests illustrate memory model behavior Thread 1 Thread 2 X = 1 Y = 1 1 3 r1 = Y r2 = X 2 4 Can r1 = 0 ∧ r2 = 0?

Litmus tests illustrate memory model behavior Thread 1 Thread 2 X = 1 Y = 1 1 3 r1 = Y r2 = X 2 4 Can r1 = 0 ∧ r2 = 0? Sequen>al consistency : no

Litmus tests illustrate memory model behavior Thread 1 Thread 2 X = 1 Y = 1 1 3 r1 = Y r2 = X 2 4 Can r1 = 0 ∧ r2 = 0? Sequen>al consistency : no x86 : yes!

Litmus tests illustrate memory model behavior Thread 1 Thread 2 X = 1 Y = 1 1 3 r1 = Y r2 = X 2 4 Can r1 = 0 ∧ r2 = 0? Sequen>al consistency : no x86 : yes! A memory model M is a set of constraints that define the possible execu@ons (outcomes) of a program.

Litmus tests illustrate memory model behavior Thread 1 Thread 2 X = 1 Y = 1 1 3 r1 = Y r2 = X 2 4 Can r1 = 0 ∧ r2 = 0? Sequen>al consistency : no x86 : yes! A memory model M is a set of constraints that define the possible execu@ons (outcomes) of a program. Memory model M allows litmus test T if there exists an execu@on that sa@sfies M’s constraints.

Litmus tests illustrate memory model behavior Memory model Thread 1 Thread 2 M allows test T: Me ∃ E. M(T,E) X = 1 Y = 1 1 3 r1 = Y r2 = X 2 4 Can r1 = 0 ∧ r2 = 0? Sequen>al consistency : no x86 : yes! A memory model M is a set of constraints that define the possible execu@ons (outcomes) of a program.

Memory models, formally Memory model Common formaliza@ons based on rela>onal logic M allows test T: ∃ E. M(T,E) Example for sequen>al consistency : no ^(ws + fr + po + rf + fences) & iden [Alglave et al, CAV’10]

Memory models, formally Memory model Common formaliza@ons based on rela>onal logic M allows test T: ∃ E. M(T,E) Example for sequen>al consistency : no ^(ws + fr + po + rf + fences) & iden Binary rela@ons over program instruc@ons [Alglave et al, CAV’10]

Memory models, formally Memory model Common formaliza@ons based on rela>onal logic M allows test T: ∃ E. M(T,E) Example for sequen>al consistency : happens-before order no ^(ws + fr + po + rf + fences) & iden Binary rela@ons over program instruc@ons [Alglave et al, CAV’10]

Memory models, formally Memory model Common formaliza@ons based on rela>onal logic M allows test T: ∃ E. M(T,E) Example for sequen>al consistency : happens-before order is acyclic no ^(ws + fr + po + rf + fences) & iden Binary rela@ons over program instruc@ons [Alglave et al, CAV’10]

Memory models, formally Memory model Common formaliza@ons based on rela>onal logic M allows test T: ∃ E. M(T,E) Example for sequen>al consistency : happens-before order is acyclic no ^(ws + fr + po + rf + fences) & iden Binary rela@ons over From program syntax program instruc@ons [Alglave et al, CAV’10]

Memory models, formally Memory model Common formaliza@ons based on rela>onal logic M allows test T: ∃ E. M(T,E) Example for sequen>al consistency : happens-before order is acyclic no ^(ws + fr + po + rf + fences) & iden Binary rela@ons over From program syntax program instruc@ons Thread 1 Thread 2 X = 1 Y = 1 1 3 r1 = Y r2 = X 2 4 Can r1 = 0 ∧ r2 = 0? [Alglave et al, CAV’10]

Memory models, formally Memory model Common formaliza@ons based on rela>onal logic M allows test T: ∃ E. M(T,E) Example for sequen>al consistency : happens-before order is acyclic no ^(ws + fr + po + rf + fences) & iden Binary rela@ons over From program syntax program instruc@ons Thread 1 Thread 2 Program order: X = 1 Y = 1 1 3 po = {( , ), ( , )} 1 2 3 4 r1 = Y r2 = X 2 4 Can r1 = 0 ∧ r2 = 0? [Alglave et al, CAV’10]

Memory models, formally Memory model Common formaliza@ons based on rela>onal logic M allows test T: ∃ E. M(T,E) Example for sequen>al consistency : Part of execu@on; implicitly existen@ally quan@fied happens-before order is acyclic no ^(ws + fr + po + rf + fences) & iden Binary rela@ons over From program syntax program instruc@ons Thread 1 Thread 2 Program order: X = 1 Y = 1 1 3 po = {( , ), ( , )} 1 2 3 4 r1 = Y r2 = X 2 4 Can r1 = 0 ∧ r2 = 0? [Alglave et al, CAV’10]

Framework sketches A framework sketch defines the search space for synthesizing a memory model M by including holes in constraints no ^(ws + fr + po + rf + fences) & iden

Framework sketches A framework sketch defines the search space for synthesizing a memory model M by including holes in constraints Expression holes for a synthesizer to complete no ^(ws + fr + po + rf + fences) & iden ?? ?? ??

Framework sketches A framework sketch defines the search space for synthesizing a memory model M by including holes in constraints Expression holes for a synthesizer to complete no ^(ws + fr + po + rf + fences) & iden ?? ?? ?? Framework sketches are the key design tool for synthesizing memory model specifica@ons — they define the “interes@ng” candidate models

Memory model frameworks no ^(ws + fr + po + rf + fences) & iden ?? ?? ?? [Alglave et al, CAV’10]

Memory model frameworks no ^(ws + fr + ppo + grf + fences ) & iden Preserved program Global reads Fence cumula>vity order (same-thread from (inter- (for Power, ARM, reorderings) thread order) etc) [Alglave et al, CAV’10]

Memory model frameworks no ^(ws + fr + ppo + grf + fences ) & iden Preserved program Global reads Fence cumula>vity order (same-thread from (inter- (for Power, ARM, reorderings) thread order) etc) Sequen>al ∅ po rf consistency [Alglave et al, CAV’10]

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.