Backend Tools It is possible to save/load settings using the Save - PowerPoint PPT Presentation

Import Design This step will take a while. Be patient and pick exactly the files specified in the guide. Backend Tools It is possible to save/load settings using the Save button. Do this to avoid browsing for all files multiple times.

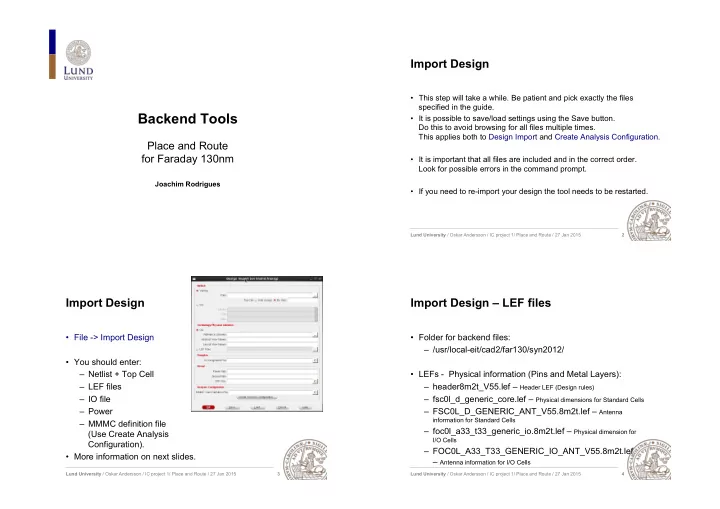

Import Design • This step will take a while. Be patient and pick exactly the files specified in the guide. Backend Tools • It is possible to save/load settings using the Save button. Do this to avoid browsing for all files multiple times. This applies both to Design Import and Create Analysis Configuration. Place and Route for Faraday 130nm • It is important that all files are included and in the correct order. Look for possible errors in the command prompt. Joachim Rodrigues • If you need to re-import your design the tool needs to be restarted. Lund University / Oskar Andersson / IC project 1/ Place and Route / 27 Jan 2015 2 Import Design Import Design – LEF files • File -> Import Design • Folder for backend files: – /usr/local-eit/cad2/far130/syn2012/ • You should enter: – Netlist + Top Cell • LEFs - Physical information (Pins and Metal Layers): – LEF files – header8m2t_V55.lef – Header LEF (Design rules) – IO file – fsc0l_d_generic_core.lef – Physical dimensions for Standard Cells – Power – FSC0L_D_GENERIC_ANT_V55.8m2t.lef – Antenna information for Standard Cells – MMMC definition file – foc0l_a33_t33_generic_io.8m2t.lef – Physical dimension for (Use Create Analysis I/O Cells Configuration). – FOC0L_A33_T33_GENERIC_IO_ANT_V55.8m2t.lef • More information on next slides. – Antenna information for I/O Cells Lund University / Oskar Andersson / IC project 1/ Place and Route / 27 Jan 2015 Lund University / Oskar Andersson / IC project 1/ Place and Route / 27 Jan 2015 3 4

Import Design – Timing Files Import Design - Memories • Folder for backend files: • Memories are found in memory directory. – /usr/local-eit/cad2/far130/syn2012/ • LEFs: • Libs: – SPLD130_512X14BM1A.lef – fsc0l_d_generic_core_xx.lib – Low Power Standard Cell Library – SHLD130_128X32X1BM1.lef – foc0l_a33_t33_generic_io_xx.lib – Low Power I/O Library • Libs: • Performance variations depending on environment: – Best Case : Manufacturing Process, Voltage, Temperature. • SPLD130_512X14BM1A_BC.lib • MAX-timing = worst timing => Worst Case • SHLD130_128X32X1BM1_BC.lib – ss1p08v125c ( slow NMOS – slow PMOS ) (1.08V) (125°C) – Worst Case: • Min-Timing = best timing => Best Case • SPLD130_512X14BM1A_WC.lib – ff1p32vm40c ( fast NMOS – fast PMOS ) (1.32V) (- 40°C) • SHLD130_128X32X1BM1_WC.lib Lund University / Oskar Andersson / IC project 1/ Place and Route / 27 Jan 2015 5 Lund University / Oskar Andersson / IC project 1/ Place and Route / 27 Jan 2015 6 Import Design - Import Design Create Analysis Configuration • After you have entered: • The empty configuration looks like this. – Netlist + Top Cell • Feel free to read the wizard – LEF files about Multi-mode-multi- corner. – IO file • The idea is to analyze the – Power designed chip in multiple • It should look something environments at different manufacturing process like this. variations. To make sure the • First: Click Save. fabricated chip works in all cases. • Afterwards: Click on Create • We will now pupulate Analysis Configuration elements in the MMMC viewer. Lund University / Oskar Andersson / IC project 1/ Place and Route / 27 Jan 2015 Lund University / Oskar Andersson / IC project 1/ Place and Route / 27 Jan 2015 7 8

Import Design - Import Design - Create Analysis Create Analysis Configuration Configuration • Start by right clicking on • Continue to create two RC Library set and select New. corners. • Create one set FF for best • Create one FF for best case case timing timing – Add the best case timing – Change Temperature to libraries. -40°C. – Shown on Previous slide, • Use 125°C for Worst Case don’t forget the memory (SS). files (not shown in figure). • Create a similar set SS for worst case timing. Lund University / Oskar Andersson / IC project 1/ Place and Route / 27 Jan 2015 9 Lund University / Oskar Andersson / IC project 1/ Place and Route / 27 Jan 2015 10 Import Design - Import Design - Create Analysis Create Analysis Configuration Configuration • Create two OpConds. • Add two delay corners. FF, and SS. • Name them: WCCOM – (SS) Worst Case • Choose the existing RC BCCOM – (FF) Best Case corner and corresponding Library Set. • These are operating conditions defined in the lib • Enter the OpCond and copy files, and therefore, named the Opcond Lib from the different. previous OpCond dialog. • Use the Voltage and Temperature for the specific library. Lund University / Oskar Andersson / IC project 1/ Place and Route / 27 Jan 2015 Lund University / Oskar Andersson / IC project 1/ Place and Route / 27 Jan 2015 11 12

Import Design - Import Design - Create Analysis Create Analysis Configuration Configuration • Now add the clock constraints • Now it is time to combine all from the SDC file (created this information. during synthesis). • Create two Analysis views using the existing Delay corner and Constraint Mode. • Select to SS Analysis View as Setup Analysis View • Select to FF Analysis View as Hold Analysis View • The design should look like the screenshot. • Do not forget to save the MMMC file. Lund University / Oskar Andersson / IC project 1/ Place and Route / 27 Jan 2015 13 Lund University / Oskar Andersson / IC project 1/ Place and Route / 27 Jan 2015 14 Import Design Global Net Connect • It should now look • To connect the power something like this. networks: Power -> • First: Click Save. Connect Global Nets … • Afterwards: Click on OK • Two types: Pin & TieHi/Low • Next time you can use Load instead, and skip • Power network, e.g., VCC browsing for all files. connect to TIEHI, Pin VCC. • Ground network, e.g., GND connects to TIELO, Pin GND. • Scope: Apply All Lund University / Oskar Andersson / IC project 1/ Place and Route / 27 Jan 2015 Lund University / Oskar Andersson / IC project 1/ Place and Route / 27 Jan 2015 15 16

Floorplan Place and rotate memories • Resize floorplan to fit memories • Move memories by selecting movement tool or press ”Shift+R”. • Floorplan -> Specify Floorplan • Need to rotate memories to have pin connections inside the core. • The size of memories can be • Rotate memories by edit proporties for measured with the ruler tool. selected object by pressing ”q”. • To zoom use the zoom buttons: • Orientation set to R180 for 180 degree rotation. • Zoom in (z), Zoom out (shift+z), Fit • Afterwards change to normal pointer by to screen (f) selecting the arrow next to or press • Also right-click and drag a square to ”a”. zoom in a to a desired area. Lund University / Oskar Andersson / IC project 1/ Place and Route / 27 Jan 2015 17 Lund University / Oskar Andersson / IC project 1/ Place and Route / 27 Jan 2015 18 Add Halo Cut Rows • Floorplan -> Edit Floorplan -> Edit Halo • Floorplan -> Row -> Cut Core Row • Deletes core rows beneath memories. • To create a ring around the memory macro, where no standard cells can be • NOTE: Be sure to select memories before cutting. placed. • Now is a good time to save the design: • Routing is still possible File -> Save Design – • Be sure to specify a distance, Data Type: Encounter e.g. 10 µ m. • To restore: File -> Restore Design • By moving memories, the cut rows are shown. • Use undo to move back. Lund University / Oskar Andersson / IC project 1/ Place and Route / 27 Jan 2015 Lund University / Oskar Andersson / IC project 1/ Place and Route / 27 Jan 2015 19 20

Power rings Power rings • Power -> Power Planning -> Add Rings • Make sure that an entire ring is visible under the advanced tab. • To add Power rings around core specify Width: 2, Spacing: 2, Offset 2. • Use metal3 for Horizontal wires and • If applied correctly your design should metal4 for Vertical wires. look like this. Lund University / Oskar Andersson / IC project 1/ Place and Route / 27 Jan 2015 21 Lund University / Oskar Andersson / IC project 1/ Place and Route / 27 Jan 2015 22 Power rings Power rings • Select the memory macros and • For the upper memory no extra power select as in the figure. routes are necessary for the top and left sides. • This will create a block ring around the memory block. • Used to connect VDD and GND for memory. • If memories are placed along the border of the die, some power- routing can be re-used. Lund University / Oskar Andersson / IC project 1/ Place and Route / 27 Jan 2015 Lund University / Oskar Andersson / IC project 1/ Place and Route / 27 Jan 2015 23 24

Power rings Power stripes • If successfull the design • Power -> Power Planning -> Add should look like the picture. Stripes • Select metal4 for vertical and metal3 for horizontal • If not, type the command: ”deleteAllPowerPreroutes”, use Tab key to autocomplete. • This command clears all power routing. Lund University / Oskar Andersson / IC project 1/ Place and Route / 27 Jan 2015 25 Lund University / Oskar Andersson / IC project 1/ Place and Route / 27 Jan 2015 26 Place well taps Place standard cells • Place -> Physical Cell -> Add well Tap • Place -> Specify -> Placement Blockage • Adds contacts for well and substrate. • Place -> Place Standard cells • Use cell FILLER4ELD • Use a spacing of 25 µ m. • Change from ”Floorplan view” to ”Physical view” to • Prefix WELLTAP see placed cells: Lund University / Oskar Andersson / IC project 1/ Place and Route / 27 Jan 2015 Lund University / Oskar Andersson / IC project 1/ Place and Route / 27 Jan 2015 27 28

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.