Symbol Timing Synchronization ELEC 433 - Spring 2013 Michael Wu - PowerPoint PPT Presentation

Symbol Timing Synchronization ELEC 433 - Spring 2013 Michael Wu & Evan Everett Question from Lab 6 2. Introduce a variable delay between the upconverter and downconverter, with the delay value selectable in your software that runs on the

Symbol Timing Synchronization ELEC 433 - Spring 2013 Michael Wu & Evan Everett

Question from Lab 6 2. Introduce a variable delay between the upconverter and downconverter, with the delay value selectable in your software that runs on the PPC. The addressable shift register block will be useful here. Observe the effect on the received constellations. Why?

Question from Lab 6 t -3T -2T -T T 2T 3T Intersymbol Interference (ISI)

One way to visualize the effect S1 S2 S3 S4 The “correct” delay yielded good results Matched Filter Transmitted Symbol

One way to visualize the effect S1 S2 S3 S4 } Poor Synchronization ⇒ S1 and S2 Interfere (ISI) Think of this case as what would happen if the receiver turns on a little too late Matched Filter Transmitted Symbol

One way to visualize the effect S1 S2 S3 S4 It’s even worse than just an initial offset... what if the TX sampling clock is a slightly different frequency than the RX? The windows drift Matched Filter Transmitted Symbol

Our Mission Can we track and compensate for this drift?

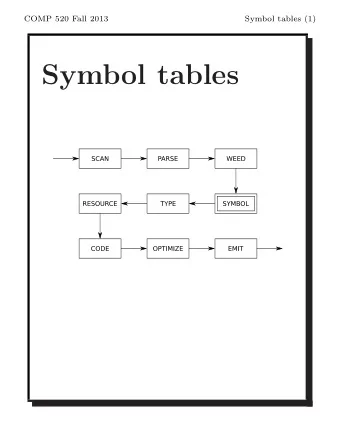

Symbol Timing Synchronization • Generally can’t change hardware clock • Frequency & phase fixed • Need to synchronize using only signal processing • Basic approach analogous to carrier recovery • Timing error detector • Loop filter • Timing error correction

Receive Chain Carrier Offset Recovery Received Down- Decimating Signal converter Matched Filter Phase Error Loop Filter Detector

Receive Chain Symbol Timing Synchronization Received Variable Down- Decimating Signal Delay converter Matched Filter Delay Timing Error Loop Filter Tracker Detector

Timing Error Detector Received Variable Down- Decimating Signal Delay converter Matched Filter Delay Timing Error Loop Filter Tracker Detector

Timing Error Detector • Assume an alternating I or Q Matched Filter Output • For positive I or Q • Sampling at the correct point yields a slope of zero in the bandlimited waveform • Sampling early yields a positive slope in the bandlimited waveform • Sampling late yields a negative slope in the bandlimited waveform • For negative I or Q, the slopes are negated

Timing Error Detector • Use a filter with h [ n ] = d( h MF [ n ]) • Called a derivative matched filter • Hint: d( h [ n ]) ≈ conv( h [ n ],[1 0 -1]) • Output should be zero at correct instant • Output is max/min at worst sampling instant Downconverted I MF sign terror dMF

Timing Error Detector • What if I or Q isn’t alternating positive and negative? ��� correct sample, but non-zero slope � ��� ��������� � ���� �� ���� � � �� �� �� �� �� ����

Timing Error Detector • Our input data is random, should have enough level transitions • We can just let the loop filter average out the errors in the timing error calculation • There are a few ways to deal with insufficient level transitions • Manchester codes and 8b/10b encoding are techniques used in wireline communications to increase level transitions • Scrambling data (like 802.11) increases level transitions

Loop Filter Received Variable Down- Decimating Signal Delay converter Matched Filter Delay Timing Error Loop Filter Tracker Detector

Loop Filter • Same 2 nd order filter structure as carrier recovery • Different coefficients K_P terror terror-filt K K_I Accumulator

Delay Tracker Received Variable Down- Decimating Signal Delay converter Matched Filter Delay Timing Error Loop Filter Tracker Detector

Delay Tracker • Computes required delay to correct timing • M is upsampling rate • Error input comes from loop filter • Runs at fast clock (M*symbol rate) 0...(M-1) d Counter (2/M) Reg en Delay terror-filt ±1 Limited Rollover Accumulator Detector

Example 1 - Perfect Sampling a 0...(M-1) d Counter (2/M) Reg en Delay b terror-filt 0 ±1 Limited Rollover Accumulator Detector M-1 a 0 1 b 0 } 2/M

Example 2 - Late Sampling a 0...(M-1) d Counter (2/M) Reg en Delay b terror-filt d ±1 Limited Rollover Accumulator Detector M-1 a 0 1 b 0 } 2/M } 2/M + d (If the correction fixed the problem)

Example 3 - Early Sampling a 0...(M-1) d Counter (2/M) Reg en Delay b terror-filt -d ±1 Limited Rollover Accumulator Detector M-1 a 0 1 b 0 } 2/M - d } 2/M (If the correction fixed the problem)

Variable Delay Received Variable Down- Decimating Signal Delay converter Matched Filter Delay Timing Error Loop Filter Tracker Detector • Output of delay tracker computes the required delay • Up to you to implement the variable delay • Hint: addressable shift register (ASR)

Summary • Test the design in simulation for a variety of starting delays between TX and RX. • No hardware build this week Received Variable Down- Decimating Signal Delay converter Matched Filter Delay Timing Error Loop Filter Tracker Detector

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.