SPI Serial Port (in AVR Microcontrollers) Contents Serial - PowerPoint PPT Presentation

Microprocessors , Lecture 7: SPI Serial Port (in AVR Microcontrollers) Contents Serial communication with SPI Serial communication programming in C Reference: Chapter 17 of the Mazidis book University of Tehran 2 Serial ports

Microprocessors , Lecture 7: SPI Serial Port (in AVR Microcontrollers)

Contents • Serial communication with SPI • Serial communication programming in C • Reference: Chapter 17 of the Mazidi’s book University of Tehran 2

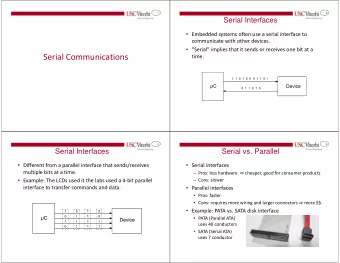

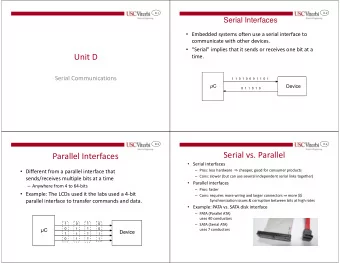

Serial ports in AVR University of Tehran 3

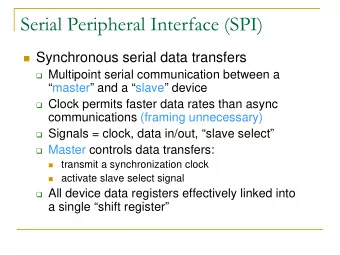

Serial ports in AVR • USART: and old and widely used standard (pins 14 and 15 of ATmega32) • SPI: very high-speed (~ two orders of magnitude faster than USART) synchronous serial port – For example for high-speed data transfer to EPROM – Pins 5 to 8 of Atmega32 • I2C (Inter IC) – Connection using a shared bus connecting up to 128 devices – Pins 22 and 23 of ATmega32 University of Tehran 4

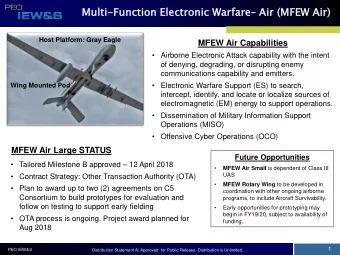

SPI • SPI : serial peripheral interface • Originally started by Motorola (now Freescale), – Now, a widely used standard adapted by many semiconductor chip companies including Atmel • Very faster than USART University of Tehran 5

SPI wiring • Uses only 2 pins for data transfer – SDI (Din) – SDO (Dout) • Requires a SCLK (shift clock) pin: to synchronize the data transfer • Requires a CE (chip enable) pin: used to initiate and terminate the data transfer • Called MOSI, MISO, SCK, and SS in AVR University of Tehran 6

3-wire SPI • Alternative: a 3-wire interface bus – SCLK and CE, and only a single pin for data transfer • The SPI 4-wire bus can become a 3-wire interface when the SDI and SDO data pins are tied together University of Tehran 7

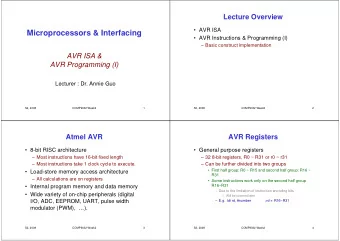

SPI architecture • Two 8-bit shift registers, one in the master and the other in the slave side • A clock generator in the master side – generates the clock for the shift registers University of Tehran 8

SPI architecture • Connections: • Serial-out pin of the master shift register to the serial-in pin of the slave shift register by MOSI (Master Out Slave In) • Serial-in pin of the master shift register to the serial-out pin of the slave shift register by MISO (Master In Slave Out) • After 8 clock pulses, the contents of the two shift registers are University of Tehran 9 interchanged

SS pin in SPI • Slave Select (SS) pin of the SPI bus is used to select a slave to initiate and terminate the data transfer • Makes sense in devices connected to several slaves • In master mode: – SS=0: enable slave – SS=1: disable slave – Active low! University of Tehran 10

SPI timing • Synchronization by clock – CPOL (clock polarity) – CPHA (clock phase ) • At CPOL= 0 the base value of the clock is zero, while at CPOL = 1 the base value of the clock is one University of Tehran 11

SPI timing • Synchronization by clock – CPOL (clock polarity) – CPHA (clock phase ) • CPHA = 0 means sample (read) on the first clock edge, while CPHA = 1 means sample on the second clock University of Tehran 12

SPI registers in AVR • SPSR (SPI Status Register) • SPCR (SPI Control Register) • SPDR (SPI Data Register) University of Tehran 13

SPSR (SPI Status Register) University of Tehran 14

SPCR (SPI Control Register) University of Tehran 15

SPCR (SPI Control Register) University of Tehran 16

SCK frequency University of Tehran 17

SPDR (SPI Data Register) • When a new data a written to this register, the SCK is generated for 8 cycles and then stops University of Tehran 18

SPI Operation • SPI can be used for simple data transfer – Just write data to SPDR – 8 clocks are generated automatically to transfer data – Slave can never start sending data • Standard mechanisms for master to read and write data from a memory address – First send address (and also tell if the transfer is read or write), then send/receive data University of Tehran 19

Steps for writing data to an SPI device • Single byte: – Make CE = 0 to begin writing – The 8-bit address is shifted in, one bit at a time, with each edge of SCLK » A7 = 1 for the write operation – After all 8 bits of the address are sent in, the SPI device expects to receive the data belonging to that address location immediately – The 8-bit data is shifted in one bit at a time, with each edge of the SCLK – Make CE = 1 to indicate the end of the write cycle University of Tehran 20

Multi-byte burst write • Burst mode: storing to consecutive locations • Provide the address of the first location, followed by the data for that location • While CE = 0, consecutive bytes are written to consecutive memory locations – The SPI device internally increments the address location as long as CE is LOW University of Tehran 21

Steps for reading data from an SPI device • Single byte: – Make CE = 0 to begin reading – The 8-bit address is shifted in one bit at a time, with each edge of SCLK » A7 = 0 for the read operation – After all 8 bits of the address are sent in, the SPI device sends out data belonging to that location – The 8-bit data is shifted out one bit at a time, with each edge of the SCLK – Make CE = 1 to indicate the end of the read cycle University of Tehran 22

Multi-byte burst read • Much like the burst write • The addresses are incremented by SPI device as long as CE is enable University of Tehran 23

SPI programming in C • Write an AVR program to initialize the SPI for master, with CLCK frequency = Fosc/l6, and then transmit 'G' via SPI repeatedly. The received data should be displayed on Port A. University of Tehran 24

SPI programming in C • Write an AVR program to initialize the SPI for master, with CLCK frequency = Fosc/l6, and then transmit 'G' via SPI repeatedly. The received data should be displayed on Port A. University of Tehran 25

SPI programming in C • Write an AVR program to initialize the SPI for slave, with CLCK frequency = Fosc/4, and then show the received data on Port D DDRB=0001,0000 // MISO as output other pins input DDRD=0xFF; //port D as output SPCR= 1100,0000 // enable interrupt, enable SPI, clk=f/4 SPSR=0; #asm (“sei”) interrupt [SPI] void spi_isr() { while (1) PORTD=SPDR; { } } University of Tehran 26

SPI in PCs • Basic Input/Output System (BIOS): – The first software run by a PC when powered on – Initialize and test the system hardware components, and to load a bootloader or an operating system • BIOS is stored on programmable ROM – The ROM is connected to Southbridge of motherboard by SPI University of Tehran 27

LPC interface • Before SPI, LPC used to be adopted to connect to BIOS • LPC: Low-pin count bus • Before 2006, Bios used to connect to Southbridge through LPC interface – Now, some laptops use LPC for bios • A 7-wire bus University of Tehran 28

SPI in a Modern Soughtbridge • ICH8 Southbridge by Intel • Two chip select signals to connect to two ROMs University of Tehran 29

Serial Flash Command Set • SPI just provides a mechanism to exchange data • Every protocol can be made on top of SPI • Example: A SPI-based flash device must support a set of commands in order to be interoperable with the SPI port of ICH8 University of Tehran 30

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.