Sensor Post-processing using MCMD technology Lars Eklund Alex - PowerPoint PPT Presentation

Sensor Post-processing using MCMD technology Lars Eklund Alex Chilingarov (Lancaster) et al. University of Cambridge, University of Glasgow, Lancaster University, University of Liverpool, Queen Mary University of London, Rutherford

Sensor Post-processing using MCMD technology • Lars Eklund • Alex Chilingarov (Lancaster) et al. • University of Cambridge, University of Glasgow, Lancaster University, University of Liverpool, Queen Mary University of London, Rutherford Appleton Laboratory +Backthinning • Andy Blue et al.

Outline • Integrated Hybrids • The first post-processing run • Results: – I/V and C/V characteristics – Capacitive load on front-end – Inter-strip resistance – Flatness and yield • Summary and Outlook – Towards a fully functional hybrid 2

Post-processing of Hybrids • Traditional silicon module build (electrical parts) – Sensors, flex circuit, substrate, pitch adaptor, wire bonds, FE-chips, passive components • A novel approach: – Multi-Chip Module – Deposited (MCMD) – Deposit dielectric and metal layers directly on the silicon sensor – Layout concepts similar to PCBs – All-in-one: Sensor, hybrid, pitch-adaptor and strip connections • Applicable to VESPA pixel or strip designs Current ATLAS/SCT module – Replace double metal on strip – Power & control timepix – Mount hybrid on sensor – four layer hybrid, with surface mounted components • Commercially available technology – Semi-industrial partner 3

Benefits and concerns Potential benefits • Reduced material – Thinner layers, no hybrid substrate • Reduced build complexity – Single object from industry • Increased integration – Higher interconnect density – Bump bonding of FE chips possible Points to prove • Electrical performance – Sensor – Hybrid (e.g. power distribution) • Radiation hardness • Thermal performance • Production yields Connecting vias to sensor pads • Cost 4

Technology description – MCM-D on Si wafers • Post-process existing micron Silicon strip sensors • Dielectric layers: Benzocyclobutene (BCB) – Deposited in layers of 3-15 µm thickness – Dielectric constant of 2.65 • Conducting layers: sputtered Cu/Ti – Standard thickness 1 µm • Connecting vias: opened through the BCB before curing – To the sensor – Between metal layers • Feature sizes – Lithographic resolution: 10 µm – Good yield at 30 µm track width/spacing – Minimal via size at 15 µm thickness: 65 µm 5

First post-processing fabrication run • Purpose of the first run: feasibility study – Investigate influence of post-processing on the sensors – Implement the first layer of a full design • Properties to be investigated – I/V & C/V characteristics – Capacitive load on front-end – Inter-strip resistance – Punch-through voltage – Yield – Sensor flatness • 4“ wafer (500 µm) with 26 mini-sensors 6

Cross-section of prototype run 4 � m Ni + Passivation Cu/Ti layer Via (3-4 � m BCB) (1 � m) 150 nm Au • etched opening in the BCB (45 º) • coated with Cu/Ti BCB (6 or 12 � m) (dielectric) Passivation (SiO 2 ) Al strip SiO 2 implant Si substrate Implement the first layer of a fully functional hybrid: GNP plane plus strip connections 7

Photos from prototype run Sensor with meshed GND plane Connections to bias and guard rings Strip pad connections 8

Yields / IV & CV • Yields – 10 wafers processors – 4/260 sensors with macroscopic defects – No electrical problems, 3000 vias probed • IV / CV – Similar to unprocessed – 50/52 sensors operate at 400 V with < 1 uA current – 30-40V depletion 9

Punch through Voltage / Inter-strip resistance • Apply voltage between strip DC pad and bias rail – Behaviour as unprocessed sensors • Measured inter-strip resistance – limit of Ris > 250 MOhm Sensor flatness •Same as unprocessed wafer scan 10

Capacitance Total capacitance of one strip • Normally dominated by coupling to nearest neighbours C IS – Small decrease as compensation for trapped surface charges • Ground back plane (C sBP ) small additional contribution • The MCMD GND plane add a new capacitive load MCMD GND plane C sG C sG C sG C Is C Is C GBP C sBP C sBP C sBP Back-plane 11

Summary of capacitive load measurements • Estimate capacitive load by C tot = C sG + C IS + C sBP • Strip length: 10 mm (8.5 mm covered by the GND plane) – Unit is approximately pF/cm C IS [pF] C sG [pF] C tot [pF] GND plane type 6 µm 12 6 µm 12 6 µm 12 µm µm µm Solid 0.63 0.75 1.84 1.03 2.7 2.0 GND 50% fill, 30 µm line width 0.71 0.82 1.30 0.82 2.2 1.8 GND 50% fill, 80 µm line width 0.75 0.84 1.14 0.68 2.1 1.7 GND 25% fill, 30 µm line width 0.83 0.89 0.76 0.48 1.8 1.6 BCB only + 3 µm passivation 1.02 1.05 - - 1.2 1.3 Bare sensor < 0.9 - ~1.1 The two values in red are interpolated values, not direct measurements Adds ~ 1pF/cm in area covered by MCMD GND plane 12

Backthinning Andy Blue et al. • Minimise mass by backthinning FE chip Backthinned APS sensor Improve APS sensitivity in UV • Common practice for CCDs • Applied to APS sensors, backthinned to 20µm – Lapping, reactive ion etching, laser annealing • Work with E2V 13

Summary and outlook • Sensor characteristics largely unaffected – I/V, CV characteristics similar to non-processed sensors – No observed change in inter-strip resistance or punch- through – No change in curvature – Increase in capacitive load observed – thick first BCB layer required • Next steps in the R&D programme (underway) – Measure irradiated samples at full upgrade fluence (under – Produce fully working four layer hybrid. – Simulate thermal performance • Backthinning well proven • Extensive experience in TSVs through 3D work • MCMD, backthinning,TSV integrated in UK VESPA upgrade programme 14

Backup 15

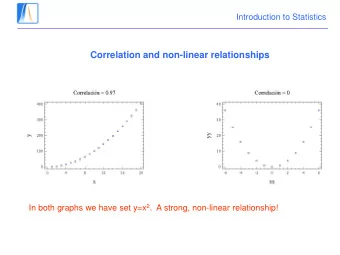

Inter-strip capacitance (C IS ) – bare & BCB covered • Bare sensors show decrease in C IS over time due to surface charge-up – Compensates for trapped charges – Need high voltage and long time to reach final value – Environmentally dependen • BCB is a very good insulator: no charge compensation C IS vs. time for bare and BCB covered (9 µm) sensors at 100 kHz 16

Inter-strip capacitance (C IS ) – adding the GND plane • Four different GND plane configurations covering the sensor – Solid and meshed with 25% or 50% fill, 30 or 80 µm line width Cf. value from no metal • C IS (bare) < 0.9 pF • C IS (BCB) = 1.02 pF plot shows results for wafer mesh 25%-30 µm with 6 µm BCB layer mesh 50%-80 µm mesh 50%-30 µm Solid GND plane 17

Capacitance to GND plane - C sG • Capacitance from strip to GND plane measured separately – Measure between bias rail and GND plane in R S -C S mode – R S = R bias / N strips , C S = C sG * N strips C sG [pF] GND plane type 6 µm 12 µm Solid 1.84 1.03 50% fill, 30 1.30 0.82 um line 50% fill, 80 1.14 0.68 um line 25% fill, 30 0.76 0.48 um line Parallel plate capacitor estimate for 6 µm BCB 1.06 < C sG < 2.65 Total capacitance between bias rail and GND plane vs. frequency strip width = 32 µm strip pitch = 80 µm 18

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.