Ratchet Intermittent Computation without Hardware Support or - PowerPoint PPT Presentation

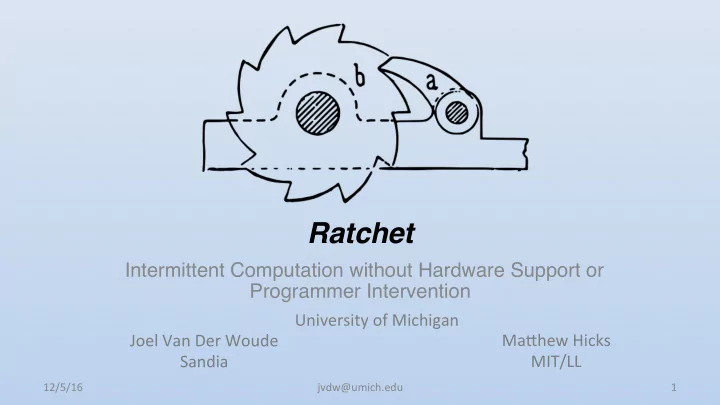

Ratchet Intermittent Computation without Hardware Support or Programmer Intervention University of Michigan Ma>hew Hicks Joel Van Der Woude MIT/LL Sandia 12/5/16 jvdw@umich.edu 1 12/5/16 jvdw@umich.edu 2 Batteries are bulky and

Ratchet Intermittent Computation without Hardware Support or Programmer Intervention University of Michigan Ma>hew Hicks Joel Van Der Woude MIT/LL Sandia 12/5/16 jvdw@umich.edu 1

12/5/16 jvdw@umich.edu 2

Batteries are bulky and inconvenient 12/5/16 jvdw@umich.edu 3

Energy harvesting 12/5/16 jvdw@umich.edu 4

Hardware monitoring vs. programmer insight or 12/5/16 jvdw@umich.edu 5

Goals of Ratchet • Burden the compiler not the programmer • Without hardware to measure voltage • Ensure forward progress under frequent power failures (~100ms) 12/5/16 jvdw@umich.edu 6

Checkpointing • Save volatile state to non-volatile memory Progress • After a power fail – restart – restore – continue Time 12/5/16 jvdw@umich.edu 7

Re-execution causes incorrectness mem[a] = mem[b] Initial Initial Initial Initial Correct Correct Correct At Fail At Fail Error mem[b] = 42 a a x x y y y y 42 mem[a] a x x y … b b y y 42 42 42 42 42 mem[b] b y y 42 return a Write a(er Read (WAR) 12/5/16 jvdw@umich.edu 8

What is idempotence? • Re-execution generates semantically correct result • A section of code that does not overwrite/ update inputs 12/5/16 jvdw@umich.edu 9

Idempotence enabling re-execution mem[a] = mem[b] Initial Initial Initial Initial Correct Correct Correct At Fail At Fail Error mem[b] = 42 a a x x y y y y y a a x x y … b b y y 42 42 42 42 42 b b y y 42 return a 12/5/16 jvdw@umich.edu 10

Ratchet system overview .c file .o file Ratchet Ratchet Idempotence Fix-up Analysis Instruction Selection ASM ASM IR IR Combine & Frontend Finalize Function Redundant Register Entry Checkpoints Allocation Emit Insert Minimum Checkpoints Checkpoint 12/5/16 jvdw@umich.edu 11

Idempotence analysis .c file .o file Ratchet Ratchet Idempotence Fix-up Analysis Instruction Selection ASM ASM IR IR Combine & Frontend Finalize Function Redundant Register Entry Checkpoints Allocation Emit Insert Minimum Checkpoints Checkpoint 12/5/16 jvdw@umich.edu 12

Identifying WARs mem[a] = mem[b] mem[b] = 42 … return a 12/5/16 jvdw@umich.edu 13

Insert checkpoints .c file .o file Ratchet Ratchet Idempotence Fix-up Analysis Instruction Selection ASM ASM IR IR Combine & Frontend Finalize Function Redundant Register Entry Checkpoints Allocation Emit Insert Minimum Checkpoints Checkpoint 12/5/16 jvdw@umich.edu 14

Seperating WARs with checkpoints • Weighted with mem[c] = 42 r0 = mem[a] r1 = mem[b] – Loop depth – # of WAR cut r2 = mem[c] checkpoint() r2 = mem[c] mem[b] = r1+1 checkpoint() mem[b] = r1+1 r3 = φ(r0,r2) mem[a] = r3+1 mem[c] = r1 12/5/16 jvdw@umich.edu 15

Fix-up .c file .o file Ratchet Ratchet Idempotence Fix-up Analysis Instruction Selection ASM ASM IR IR Combine & Frontend Finalize Function Redundant Register Entry Checkpoints Allocation Emit Insert Minimum Checkpoints Checkpoint 12/5/16 jvdw@umich.edu 16

The backend may create WARs • Stack Teardown … SP return addr new addr new regs r0-r3 • Register Spilling locals 12/5/16 jvdw@umich.edu 17

Redundant checkpoints .c file .o file Ratchet Ratchet Idempotence Fix-up Analysis Instruction Selection ASM ASM IR IR Combine & Frontend Finalize Function Redundant Register Entry Checkpoints Allocation Emit Insert Minimum Checkpoints Checkpoint 12/5/16 jvdw@umich.edu 18

Relocating checkpoints to combine • Redundant checkpoints r0 = mem[a] r0 = mem[a] r1 = mem[b] caused by… r1 = mem[b] r3 = r0+r1 r3 = r0+r1 r4 = r3+1 – Optimizations r4 = r3+1 checkpoint() checkpoint() – Scheduling Decisions R5 = r3+r4 r5 = r3+r4 mem[a] = r3 mem[a] = r3 – Register Spills checkpoint() mem[b] = r5 mem[b] = r5 12/5/16 jvdw@umich.edu 19

Minimum checkpoint .c file .o file Ratchet Ratchet Idempotence Fix-up Analysis Instruction Selection ASM ASM IR IR Combine & Frontend Finalize Function Redundant Register Entry Checkpoints Allocation Emit Insert Minimum Checkpoints Checkpoint 12/5/16 jvdw@umich.edu 20

Optimizing Ratchet • Ratchet Unoptimized • RatchetFE Function Entry • RatchetFE+RD +Remove Duplicates • RatchetFE+RD+LR +Live Registers • Ideal Single Checkpoint 12/5/16 jvdw@umich.edu 21

How we evaluated Ratchet • Simulator – Cycle accurate – Random power failures – Dynamically track idempotence – https://github.com/impedimentToProgress/thumbulator • Benchmarks – MIBench – newlib – https://github.com/impedimentToProgress/MiBench2 12/5/16 jvdw@umich.edu 22

12/5/16 jvdw@umich.edu 23

12/5/16 jvdw@umich.edu 24

12/5/16 jvdw@umich.edu 25

12/5/16 jvdw@umich.edu 26

Conclusion 12/5/16 jvdw@umich.edu 27

Questions? 12/5/16 jvdw@umich.edu 28

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.