Progr gram amming ing Rec econf nfigur igurable able Devi - PowerPoint PPT Presentation

Progr gram amming ing Rec econf nfigur igurable able Devi vices ces via FPGA Regio vi ions ns & De Devi vice e Tre ree Ove verl rlays A User View Benchmark on a Declarative FPGA Reconfiguration Framework Stefan Wiehler

Progr gram amming ing Rec econf nfigur igurable able Devi vices ces via FPGA Regio vi ions ns & De Devi vice e Tre ree Ove verl rlays A User View Benchmark on a Declarative FPGA Reconfiguration Framework Stefan Wiehler (University of Ulm, Missing Link Electronics) Ulrich Langenbach (Beuth University of Applied Sciences Berlin, Missing Link Electronics) 1

Example le System 2

Linux x FPGA Framewor ework k Architecture ecture 3

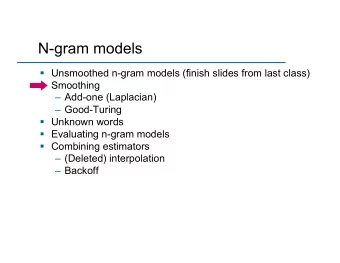

A Declar clarat ative ive FPGA A Reconf nfigur gurat ation on Fram amewor ework 4

Configuration Latency ormance nce Perform on Per ation igurati nfigu Reconf 5 Deconfiguration Latency

Scheduling ling Latency y - Profil iling ing Resu sult lts • Measurement of example system (AES accelerator) • Measured latencies via ftrace function entry and exit timestamps • Bitstream Size: 5.9 MiB 16 20 • Overall latency: ≈ 135 ms ms 1 Load Bitstream Runtime [%] Partial Reconfiguration Load Platform Driver 63 Rest incl. Framework 6

Defic icienci iencies es / F Futu ture re Work Additional Components Performance Bottlenecks • Scheduler / Governor • Firmware caching • User space interface for device tree • FPGA reconfiguration interface manipulation (Scope of FPGA vendors) • Shields & modular embedded systems • Reconfigurable systems (FPGA) • FPGA vendor tools to support DTO generation 7

Simplif ifies ies Reconf nfigur gurabl able e Computi uting ng on Linux x Systems • Linux DTO & FPGA Framework enables efficient operation of reconfigurable computing systems • Supports scheduling time slices in fractions of minutes • > 10 s between reconfigurations ≈2 % overhead in our case • Enables efficient development of heterogeneous systems on MPSoC-FPGAs • Reboot free debug and test cycles for fast turnaround times • Both static and runtime reconfigurable systems profit 8

Referenc erences es 1. Moritz Fischer, “FPGA Manager & Device Tree Overlays”, FOSDEM 2016, Brussels, 30-Jan-2016. 2. Alan Tull , “Reprogrammable Hardware under Linux”, Embedded Linux Conference Europe 2015, Dublin, 05-Okt-2015. 3. Pantelis Antoniou, “Transactional Device Tree & Overlays: Making Reconfigurable Hardware Work”, Embedded Linux Conference 2015, San Jose, 23-Mar-2015. 9

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.