Probe Card System for DHP Chip Testing VXD Workshop, Wetzlar, - PowerPoint PPT Presentation

Probe Card System for DHP Chip Testing VXD Workshop, Wetzlar, February 4-6, 2013 H. Krger, Bonn University Motivation To/from DCD PXD modules are sensitive to single- (86 CMOS/HSTL) point-of-failure of the DHP 18x CMOS 64x HSTL 4x

Probe Card System for DHP Chip Testing VXD Workshop, Wetzlar, February 4-6, 2013 H. Krüger, Bonn University

Motivation To/from DCD • PXD modules are sensitive to single- (86 CMOS/HSTL) point-of-failure of the DHP 18x CMOS 64x HSTL 4x JTAG • Up to know very little statistics of the DHP yield (+ flip chip mounting to wirebond adapters with low yield only) • Need to qualify ICs before flip-chip 4 x LVDS mounting To Switcher (4x LVDS) DHP 4x LVDS 4x JTAG Gbit TX To/from DHH (9x LVDS) VXD Workshop, Wetzlar, Feb. 2013, H. Krüger, Uni Bonn 2

DHP Chip Probing Prerequisites • What is needed: – Needle card for solder bump probing – Test bench for DHP environment • IO signals from test system (DHH like) • DCD input/output emulation – Test procedure to provide full coverage – Definition of cut parameters for chip classification • Design is based on DHP 0.2 • DHPT 1.x will be pin compatible to DHP 0.2 VXD Workshop, Wetzlar, Feb. 2013, H. Krüger, Uni Bonn 3

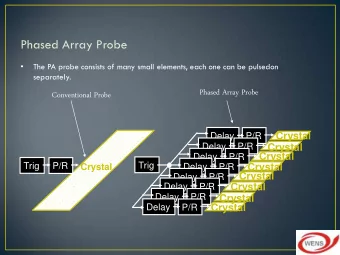

DHP Chip Probe Test System Needle Card PCB Power Supply FPGA JTAG DHP test DCD emulation DAC system Sequencer r/b Infiniband (XUPV5 FPGA Board) GPIB or USB Probe Needles Eth DHP Probe Station VXD Workshop, Wetzlar, Feb. 2013, H. Krüger, Uni Bonn 4

0 Thousands 0 1 2 3 Thousands • 159 bumps need to be connected • Material: lead free, LTS • Pitch: 200µm (y), 180µm (x) • ~110µm diameter -1 • Connections: – JTAG (4x LVDS) DHP test – Timing (4x LVDS) system – Data Link (1x CML) – Aux clock (2x LVDS) 3685µm 200µm – SWITCHER (4x LVDS) 180µm -2 – DCD out (8x 8 HSTL) FPGA – DCD in (8x 2 CMOS) bumps to connect: – DCD timing (2x CMOS) 159 out of 296 – DCD JTAG – DCD_ref (analog) – Power (8x VSS, 4x VDD, 2x VDD_CML) – PLLxx2Fast -3 – FrameSync – ResetB (CMOS) – Analog IO test signals 3685µm VXD Workshop, Wetzlar, Feb. 2013, H. Krüger, Uni Bonn 5 -4

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 180 540 900 1260 1620 1980 2340 2700 1 A no bump 0 0 0 0 0 0 0 0 0 360 720 1080 1440 1800 2160 2520 2 B 100 100 100 100 100 100 100 100 180 540 900 1260 1620 1980 2340 2700 3 C 200 200 200 200 200 200 200 200 0 360 720 1080 1440 1800 2160 2520 4 D 300 300 300 300 300 300 300 300 • 180 540 900 1260 1620 1980 2340 2700 Bump coordinates in µm 5 E 400 400 400 400 400 400 400 400 0 360 720 1080 1440 1800 2160 2520 6 F 500 500 500 500 500 500 500 500 • Origin in upper left corner 180 540 900 1260 1620 1980 2340 2700 7 G 600 600 600 600 600 600 600 600 0 360 720 1080 1440 1800 2160 2520 8 H 700 700 700 700 700 700 700 700 • No bump at location ( 0,0) 180 540 900 1260 1620 1980 2340 2700 9 J 800 800 800 800 800 800 800 800 0 360 720 1080 1440 1800 2160 2520 10 K • 900 900 900 900 900 900 900 900 Bumps with no needle 180 540 900 1260 1620 1980 2340 2700 11 L 1000 1000 1000 1000 1000 1000 1000 1000 0 360 720 1080 1440 1800 2160 2520 connection shown in gray 12 M 1100 1100 1100 1100 1100 1100 1100 1100 180 540 900 1260 1620 1980 2340 2700 13 N 1200 1200 1200 1200 1200 1200 1200 1200 0 360 720 1080 1440 1800 2160 2520 14 O 1300 1300 1300 1300 1300 1300 1300 1300 180 540 900 1260 1620 1980 2340 2700 15 P 1400 1400 1400 1400 1400 1400 1400 1400 0 360 720 1080 1440 1800 2160 2520 16 Q 1500 1500 1500 1500 1500 1500 1500 1500 180 540 900 1260 1620 1980 2340 2700 17 R 1600 1600 1600 1600 1600 1600 1600 1600 0 360 720 1080 1440 1800 2160 2520 18 S 1700 1700 1700 1700 1700 1700 1700 1700 180 540 900 1260 1620 1980 2340 2700 19 T 1800 1800 1800 1800 1800 1800 1800 1800 0 360 720 1080 1440 1800 2160 2520 20 U 1900 1900 1900 1900 1900 1900 1900 1900 180 540 900 1260 1620 1980 2340 2700 21 V 2000 2000 2000 2000 2000 2000 2000 2000 0 360 720 1080 1440 1800 2160 2520 22 W 2100 2100 2100 2100 2100 2100 2100 2100 180 540 900 1260 1620 1980 2340 2700 23 X 2200 2200 2200 2200 2200 2200 2200 2200 0 360 720 1080 1440 1800 2160 2520 24 Y 2300 2300 2300 2300 2300 2300 2300 2300 180 540 900 1260 1620 1980 2340 2700 25 Z 2400 2400 2400 2400 2400 2400 2400 2400 0 360 720 1080 1440 1800 2160 2520 26 AA 2500 2500 2500 2500 2500 2500 2500 2500 180 540 900 1260 1620 1980 2340 2700 27 AB 2600 2600 2600 2600 2600 2600 2600 2600 0 360 720 1080 1440 1800 2160 2520 28 AC 2700 2700 2700 2700 2700 2700 2700 2700 180 540 900 1260 1620 1980 2340 2700 29 AD 2800 2800 2800 2800 2800 2800 2800 2800 0 360 720 1080 1440 1800 2160 2520 30 AE 2900 2900 2900 2900 2900 2900 2900 2900 180 540 900 1260 1620 1980 2340 2700 31 AF 3000 3000 3000 3000 3000 3000 3000 3000 0 360 720 1080 1440 1800 2160 2520 32 AG 3100 3100 3100 3100 3100 3100 3100 3100 180 540 900 1260 1620 1980 2340 2700 33 AH 3200 3200 3200 3200 3200 3200 3200 3200 0 360 720 1080 1440 1800 2160 2520 34 AJ 3300 3300 3300 3300 3300 3300 3300 3300 180 540 900 1260 1620 1980 2340 2700 35 AK 3400 3400 3400 3400 3400 3400 3400 3400 0 360 720 1080 1440 1800 2160 2520 36 AL 3500 3500 3500 3500 3500 3500 3500 3500 180 540 900 1260 1620 1980 2340 2700 37 AM VXD Workshop, Wetzlar, Feb. 2013, H. Krüger, Uni Bonn 6 3600 3600 3600 3600 3600 3600 3600 3600

DHP 0.2 Layout Examples from vendor VXD Workshop, Wetzlar, Feb. 2013, H. Krüger, Uni Bonn 8

Debug Probe Card • PCB with active components, will need some debugging • Very sensitive with needles attached Dedicated debug “Probe” Card • (almost) same netlist as needle card PCB • replace needle footprint with DHP 0.2 wire bond adapter Debug PCB is ready and tested • DHP communication • FPGA programming (DCD emulation, Switcher sequencer read-back) Debug Probe Card VXD Workshop, Wetzlar, Feb. 2013, H. Krüger, Uni Bonn 9

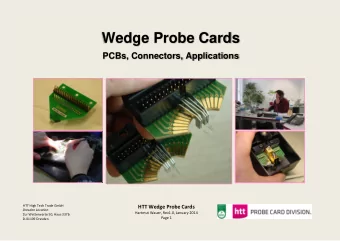

Needle Card PCB Specs • 6 layer PCB • 3mm thick mechanical stiffness Status – PCB Design & Production – Component mounting – Testing – Needle mounting • needs ~4 weeks (@ HTT) Needle Probe Card (w/o needles) VXD Workshop, Wetzlar, Feb. 2013, H. Krüger, Uni Bonn 10

Probe Station Setup • Needle card fixture • We have diced chips only – put single chips on chuck (Ok for now) – “chess board” fixture with array of cavities for production testing tbd • External components: – Power supply – DHP test system (FPGA board via Infiniband cables) – extra JTAG for on board FPGA programming/readback , optional: can use JTAG from Infiniband connection VXD Workshop, Wetzlar, Feb. 2013, H. Krüger, Uni Bonn 11

Probe Card System Status • Hardware components of the needle card test system – Debug probe card for HW verification and debugging – Needle probe card: components mounted and tested, shipped for needle mounting end of January (takes ~4 weeks) – Mechanical fixture for probe station • Software – based on DHP test system from Mikhail ( ) – needs further extensions (for basic testing ok) • (more) systematic sequencer and DHP DAC output read-back • automation of test sequences • coverage… • definition of cut parameters • … • Planning – Start commissioning of the needle card system by end of Feb – First (rudimentary) tested DHP chips supposed to be available in March VXD Workshop, Wetzlar, Feb. 2013, H. Krüger, Uni Bonn 12

DHP Chip Availability • Only small number of DHP 0.2 chips left (~15) • Next chip version (DHPT 1.0) available by mid 2013 • Need certain number of tested chips for E-MCM and PXD6 large matrix assemblies Possible scenarios: a) DHP has high yield, enough Ok tested die for E-MCM + PXD6 (very optimistic) no action needed b) DHP yield not sufficient, need more chips (more likely) i) Buy remaining MPW chips from MOSIS (rather expensive) ii) Wait for DHPT 1.0 to become available (maybe too late) iii) Recover unsuccessful DHP 0.2 flip chip assemblies (quite a few) Recovery procedure • De-solder and clean DHP chips (Valencia ?) • Place new bumps (Heidelberg ?) VXD Workshop, Wetzlar, Feb. 2013, H. Krüger, Uni Bonn 13

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.