Part III Part III Storage Management Storage Management Chapter - PowerPoint PPT Presentation

Part III Part III Storage Management Storage Management Chapter 9: Virtual Memory Chapter 9: Virtual Memory 1 Fall 2010 Observations Observations A complete program does not have to be in memory because memory, because error

Part III Part III Storage Management Storage Management Chapter 9: Virtual Memory Chapter 9: Virtual Memory 1 Fall 2010

Observations Observations � A complete program does not have to be in memory because memory, because � error handling codes are not frequently used � arrays, tables, large data structures usually � t bl l d t t t ll allocate memory more than necessary and many parts are not used at the same time many parts are not used at the same time � some options and cases may be used rarely � If they are not needed, why must they be in � If th t d d h t th b i memory? 2

Benefits Benefits Benefits Benefits � P � Program length is not restricted to real l th i t t i t d t l memory size. That is, virtual address size can be larger than physical memory size. b l th h i l i � Can run more programs because space originally allocated for the un-loaded parts can be used by other programs. � Save load/swap I/O time because we do not have to load/swap a complete program. p p p g 3

Virtual Virtual Memory Virtual Virtual Memory Memory Memory � Virtual memory is the separation of user logical � Virtual memory is the separation of user logical memory from physical memory. � This permits to have extremely large virtual � This permits to have extremely large virtual memory, which makes programming large systems easier systems easier. � Because memory segments can be shared, this further improves performance and save time further improves performance and save time. � Virtual memory is commonly implemented with demand paging demand segmentation or with demand paging, demand segmentation or demand paging+segmentation. 4

Demand Demand Paging Demand Demand Paging Paging Paging virtual memory page table physical memory page frame table 0 i 0 0 0 1 v 7 proc A pg 4 proc A, pg 4 1 1 2 1 1 i 3 2 i 2 2 4 v 1 3 i i 5 5 3 3 3 3 4 6 i 5 4 4 6 5 5 5 5 proc A, pg 1 7 6 6 8 7 9 process A 8 9 valid/invalid or 5 present/absent bit

Address Address Translation Address Address Translation Translation ranslation � Address translation from a virtual address to a � Address translation from a virtual address to a physical address is the same as a paging system. � However there is an additional check If the � However, there is an additional check. If the needed page is not in physical memory ( i.e ., its valid bit is not set), a page fault ( i.e ., a trap) occurs. bit is not set) a page fault ( i e a trap) occurs � If a page fault occurs, we need to do the following: � Find an unused page frame If no such page � Find an unused page frame. If no such page frame exists, a victim must be found and evicted. � Write the old page out and load the new page in � Write the old page out and load the new page in. � Update both page tables. � R � Resume the interrupted instruction. h i d i i 6

Details of Handling a Page Fault Details of Handling a Page Fault Trap to the OS // a context switch occurs p Make sure it is a page fault; If the address is not a legal one then address error, return Find a page frame // page replacement algorithm Write the victim page back to disk // page out Write the victim page back to disk // page out Load the new page from disk // page in Update both page tables // two pages are involved! p p g p g Resume the execution of the interrupted instruction 7

Hardw are Hardw are Support Hardw are Hardw are Support Support Support � Page Table Base Register, Page Table Length Register, and a Page Table. � Each entry of a page table must have a valid/invalid bit. Valid means that page is in p g physical memory. The address translation hardware must recognize this bit and generate a page fault if the valid bit is not set. � Secondary Memory: use a disk. � Secondary Memory: use a disk. � Other hardware components may be needed and will be discussed later and will be discussed later. 8

Too Too Too Many Too Many Many Memory any Memory Memory Accesses?! Memory Accesses?! Accesses?! Accesses?! � Each address reference may use at least two memory accesses, one for page table look up f bl l k and the other for accessing the page. It may be worse! See below: worse! See below: A C How many memory accesses are there? May be more than eight! ADD A, B, C B 9

Performance Performance Issue: Performance Performance Issue: Issue: 1/2 Issue: 1/2 1/2 1/2 � Let p be the probability of a page fault, the page p p y p g p g fault rate, 0 ≤ p ≤ 1. � The effective access time is (1- p )*memory access time + p *page fault time � The page fault rate p should be small, and � The page fault rate p should be small, and memory access time is usually between 10 and 200 nanoseconds. � To complete a page fault, three components are important: � Serve the page-fault trap � Page-in and page-out, a bottleneck g p g , � Resume the interrupted process 10

Performance Performance Issue: Performance Performance Issue: Issue: 2/2 Issue: 2/2 2/2 2/2 � Suppose memory access time is 100 nanoseconds � Suppose memory access time is 100 nanoseconds, paging requires 25 milliseconds (software and hardware). Then, effective access time is ) , (1- p )*100 + p *(25 milliseconds) = (1- p )*100 + p *25 000 000 nanoseconds (1- p ) 100 + p 25,000,000 nanoseconds = 100 + 24,999,900* p nanoseconds � If page fault rate is 1/1000 the effective access time � If page fault rate is 1/1000, the effective access time is 25,099 nanoseconds = 25 microseconds. It is 250 times slower! times slower! � If we wish only 10% slower, effective access time is no more than 110 and p =0 0000004 no more than 110 and p 0.0000004. 11

Three Three Important Three Three Important Important Issues mportant Issues Issues in Issues in in V.M. in V M � P � Page tables can be very large. If an address has t bl b l If dd h 32 bits and page size is 4K, then there are 2 32 /2 12 2 20 (2 10 ) 2 2 32 /2 12 =2 20 =(2 10 ) 2 = 1M entries in a page table per 1M t i i t bl process! � Virtual to physical address translation must be fast. This is done with TLB. � Page replacement. When a page fault occurs and there is no free page frame, a victim page must p g p g be found. If the victim is not selected properly, system degradation may be high. y g y g 12

Page Page Table Page Page Table Table Size Table Size Size ize virtual address index 1 index 2 index 3 offset page table 8 6 6 12 memory memory base register base register Only level 1 page tables are in level 1 page table level 2 physical memory. level 3 page table page table Other page tables may be page table paged-in when they are May be in virtual memory referred to. 13

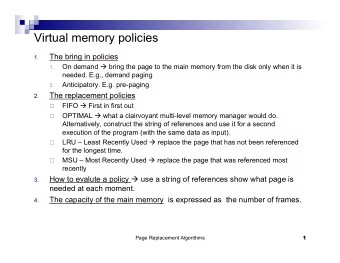

Pa Page Re g g e Replacement: p p lacement: 1/2 1/2 � The following is a basic scheme � Find the desired page on disk � Find a free page frame in physical memory p g p y y � If there is a free page frame, use it � If there is no free page frame, use a page- If there is no free page frame, use a page replacement algorithm to find a victim page � Write this victim page back to disk and Write this victim page back to disk and update the page table and page frame table � Read the desired page into the selected frame � Read the desired page into the selected frame and update page tables and page frame table � Restart the interrupted instruction � Restart the interrupted instruction 14

Page Page Replacement: Page Page Replacement: Replacement: 2/2 Replacement: 2/2 2/2 2/2 � If there is no free page frame, two page transfers ( i e page in and page out) may be required ( i.e ., page-in and page-out) may be required. � A modify bit may be added to a page table entry. The modify bit is set if that page has been modified The modify bit is set if that page has been modified ( i.e ., storing info into it). It is initialized to 0 when a page is loaded into memory page is loaded into memory. � Thus, if a page is not modified ( i.e ., modify bit = 0), it does not have to be written back to disk it does not have to be written back to disk. � Some systems may also have a reference bit. When a page is referenced ( i e reading or writing) its a page is referenced ( i.e ., reading or writing), its reference bit is set. It is initialized to 0 when a page is brought in. g � Both bits are set by hardware automatically. 15

Pa Page Re g g e Replacement Al p p lacement Algorithms g orithms � We shall discuss the following page replacement algorithms: l i h � First-In-First-Out - FIFO � The Least Recently Used – LRU � The Optimal Algorithm p g � The Second Chance Algorithm � The Clock Algorithm � The Clock Algorithm � The fewer number of page faults an algorithm generates, the better the algorithm performs. generates, the better the algorithm performs. � Page replacement algorithms work on page numbers. A string of page numbers is referred to numbers. A string of page numbers is referred to as a page reference string. 16

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.