Part III Part III Gain- -based synthesis based synthesis Gain - PowerPoint PPT Presentation

Part III Part III Gain- -based synthesis based synthesis Gain enabler for correct- -by by- -construction design construction design enabler for correct ASP- -DAC01 Tutorial DAC01 Tutorial ASP Patrick Groeneveld

Part III Part III Gain- -based synthesis based synthesis Gain enabler for ‘correct- -by by- -construction’ design construction’ design enabler for ‘correct ASP- -DAC’01 Tutorial DAC’01 Tutorial ASP Patrick Groeneveld Patrick Groeneveld (patrick patrick@magma @magma- -da da.com) .com) ( Magma Design Automation Magma Design Automation Cupertino, CA Cupertino, CA ASP-DAC'01 - Patrick Groeneveld 1

Summary Summary I Iterative flow Iterative flow vs vs. stepwise refinement . stepwise refinement I I Derivation of a simple delay model Derivation of a simple delay model I I Gain based delay optimization Gain based delay optimization I I Building a tool flow around this model Building a tool flow around this model I I Standard cell library issues Standard cell library issues I I Getting timing during routing Getting timing during routing I I Recommendations Recommendations I III-2 ASP-DAC'01 - Patrick Groeneveld

Preliminaries Preliminaries I Timing closure: Obtaining a feasible layout of a circuit Timing closure: Obtaining a feasible layout of a circuit I that meets the given timing specification. that meets the given timing specification. I Objective: Obtain closure as fast and effortless as Objective: Obtain closure as fast and effortless as I possible. possible. I Assumptions: Assumptions: I N ASIC design style. ASIC design style. N Standard cell abstraction. Standard cell abstraction. N Static CMOS. Static CMOS. I Neglect other design issues Neglect other design issues I III-3 ASP-DAC'01 - Patrick Groeneveld

Interconnect parasitics parasitics (C and R) (C and R) Interconnect I Speed is entirely determined by Speed is entirely determined by parasitics parasitics I I Parasitics Parasitics are tiny are tiny I I Parasitics Parasitics depend on the depend on the exact exact layout layout I I Therefore they are hard or impossible to estimate, Therefore they are hard or impossible to estimate, I especially before placement. especially before placement. III-4 ASP-DAC'01 - Patrick Groeneveld

Timing Uncertainty Timing Uncertainty Gate- Gate -to to- -gate delay depends on: gate delay depends on: • Wire length (unknown during synthesis) Wire length (unknown during synthesis) • • The layer of the wire (determined during routing) The layer of the wire (determined during routing) • • The configuration of the neighboring wires: The configuration of the neighboring wires: • distance, near/far (unknown before detailed routing) distance, near/far (unknown before detailed routing) • Timing window and slope of the neighboring wires. • Timing window and slope of the neighboring wires. III-5 ASP-DAC'01 - Patrick Groeneveld

Meeting timing gets harder Meeting timing gets harder q Flip Flip Flip Flip d flop flop q flop flop q Flip Flip d Flip Flip flop flop flop flop q q Flip Flip flop flop q 5 ns 5 ns max max III-6 ASP-DAC'01 - Patrick Groeneveld

Timing is a result of the placement Timing is a result of the placement I The bad news: the worst timing sets the clock speed! The bad news: the worst timing sets the clock speed! I s slack C dream C real slack III-7 ASP-DAC'01 - Patrick Groeneveld

Prediction vs reality Prediction vs reality circuit does circuit does not work not work number of number of nets nets -100% 100% +100% +100% fastest/best fastest/best slowest/worst slowest/worst Average, Average, wireload model, wireload model, what you what you designed for designed for Real delay - predicted delay Real delay predicted delay III-8 ASP-DAC'01 - Patrick Groeneveld

The end of the wire load model The end of the wire load model I Model is used in Model is used in coventional coventional synthesis tools synthesis tools I I It guesses load based on the number of pins of the It guesses load based on the number of pins of the I net net I The average is correct but... The average is correct but... I III-9 ASP-DAC'01 - Patrick Groeneveld

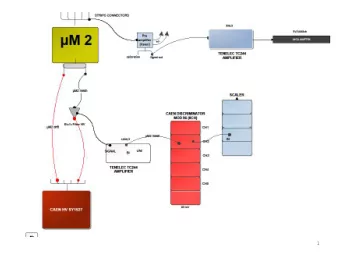

Today’s Conventional Flow Today’s Conventional Flow RTL I Synthesis does not Synthesis does not I Logic Synthesis Logic Synthesis accurately model accurately model interconnect interconnect Placement I Cell sizes fixed before Cell sizes fixed before I placement. placement. Multiple Routing I Place & route unable Place & route unable I iterations to meet timing goal to meet timing goal Extraction Timing Analysis Met timing? You must iterate! You must iterate! NO GDSII III-10 ASP-DAC'01 - Patrick Groeneveld

The trial and error iteration The trial and error iteration logic synthesis place & route III-11 ASP-DAC'01 - Patrick Groeneveld

Methodology Problems Methodology Problems I To avoid endless iterations, the design must be ‘on To avoid endless iterations, the design must be ‘on I the safe side’ the safe side’ I Iterations are very slow and may not converge Iterations are very slow and may not converge I I You’re never sure if you’ll make it You’re never sure if you’ll make it I I Only a painful trial and error process reports design Only a painful trial and error process reports design I feasibility. feasibility. III-12 ASP-DAC'01 - Patrick Groeneveld

Ways to attack timing closure Ways to attack timing closure I Iterate through SPEF or internally Iterate through SPEF or internally I I Post Post- -placement optimization (ECO) placement optimization (ECO) I I Partition the design into smaller pieces Partition the design into smaller pieces I N Variation in wire length will decrease Variation in wire length will decrease N Better timing closure on each block if #gates < 50,000 Better timing closure on each block if #gates < 50,000 I Gain Gain- -based synthesis based synthesis I III-13 ASP-DAC'01 - Patrick Groeneveld

Hierarchy: a solution? Hierarchy: a solution? I Make problems smaller Make problems smaller I I Structure makes the problem Structure makes the problem I better manageable better manageable I Solve sub Solve sub- -problems problems I independently independently I Enables efficient re Enables efficient re- -use use I I Enables consistent verification Enables consistent verification I III-14 ASP-DAC'01 - Patrick Groeneveld

Physical hierarchy and timing closure Physical hierarchy and timing closure I Wires need to slalom around blocks or traverse Wires need to slalom around blocks or traverse I through or over blocks through or over blocks I How to set pin locations? How to set pin locations? I I Where to put the buffers? Where to put the buffers? I I Automatic floor planning problem is unsolved Automatic floor planning problem is unsolved I I Large hidden inefficiency Large hidden inefficiency I III-15 ASP-DAC'01 - Patrick Groeneveld

Physical hierarchy is a necessary evil Physical hierarchy is a necessary evil macro macro 2,000,000 2,000,000 20 x 20 x approx approx. 100,000 . 100,000 standard cells flat? standard cells flat? standard cells standard cells I If you can do it, do it as flat If you can do it, do it as flat macro I as possible! as possible! 4 blocks of 500,000 4 blocks of 500,000 I Also do Also do datapath datapath flat flat I standard cells? standard cells? III-16 ASP-DAC'01 - Patrick Groeneveld

Conventional layout synthesis Conventional layout synthesis s slack C dream C real slack III-17 ASP-DAC'01 - Patrick Groeneveld

Gain- -based synthesis: based synthesis: Gain s slack C dream C real III-18 ASP-DAC'01 - Patrick Groeneveld

Focus for timing closure Focus for timing closure I Combine logical and physical worlds. Combine logical and physical worlds. I I Crisp: focus on the main effect, skip irrelevant details Crisp: focus on the main effect, skip irrelevant details I I Enable blazingly fast optimization Enable blazingly fast optimization I I Compact: Memory efficient for tomorrow’s 50M gate chip Compact: Memory efficient for tomorrow’s 50M gate chip I III-19 ASP-DAC'01 - Patrick Groeneveld

Good practices, bad practices Good practices, bad practices Use a simple model, and adapt reality to it. Use a simple model, and adapt reality to it. I At each step, freeze a single constraint, postpone decisions on others. At each step, freeze a single constraint, postpone decisions on others. I Allow sufficient freedom in future steps to fulfill all remaining g Allow sufficient freedom in future steps to fulfill all remainin I constraints. constraints. Bail out early if there’s no use continuing Bail out early if there’s no use continuing I Fix multiple objectives at once. Fix multiple objectives at once. I Iterate. Iterate. I Indulge in ‘accurate’ models Indulge in ‘accurate’ models I Attempt to be optimal Attempt to be optimal I III-20 ASP-DAC'01 - Patrick Groeneveld

Is ‘Optimal’ optimal??, an example Is ‘Optimal’ optimal??, an example Contacts in layout have Contacts in layout have parasitic resistance and parasitic resistance and affect reliability affect reliability 8 contacts 8 contacts Optimal Optimal with contact minimization: with contact minimization: 0 contacts 0 contacts But….. But….. There are still 8 contacts! There are still 8 contacts! (they were just pushed (they were just pushed into the neighboring regions) into the neighboring regions) III-21 ASP-DAC'01 - Patrick Groeneveld

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.