Parallel prefix adders Kostas Vitoroulis, 2006. Presented to Dr. - PowerPoint PPT Presentation

Parallel prefix adders Kostas Vitoroulis, 2006. Presented to Dr. A. J. Al-Khalili. Concordia University. Overview of presentation Parallel prefix operations Binary addition as a parallel prefix operation Prefix graphs Adder

Parallel prefix adders Kostas Vitoroulis, 2006. Presented to Dr. A. J. Al-Khalili. Concordia University.

Overview of presentation � Parallel prefix operations � Binary addition as a parallel prefix operation � Prefix graphs � Adder topologies � Summary

Parallel Prefix Operation Terminology background: � Prefix: The outcome of the operation depends on the initial inputs. � Parallel: Involves the execution of an operation in parallel. This is done by segmentation into smaller pieces that are computed in parallel. � Operation: Any arbitrary primitive operator “ ° ” that is associative is parallelizable it is fast because the processing is accomplished in a parallel fashion. �

Example: Associative operations are parallelizable Consider the logical OR operation: a + b The operation is associative: a + b + c + d = ((( a + b ) + c) + d ) = (( a + b ) + ( c + d)) Serial implementation: Parallel implementation:

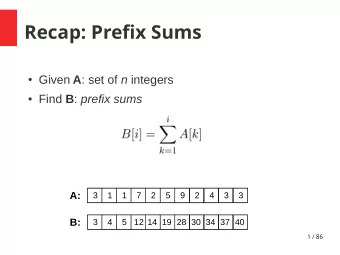

Mathematical Formulation: Prefix Sum � this is the unary operator � Operator: “ ° ” known as “scan” or “prefix sum” � Input is a vector: A = A n A n-1 … A 1 � Output is another vector: B = B n B n-1 … B 1 where B 1 = A 1 B 2 = A 1 ° A 2 � B n represents the … operator being applied to B n = A 1 ° A 2 … ° A n all terms of the vector.

Example of prefix sum Consider the vector: A = A n A n-1 … A 1 where element A i is an integer The “*” unary operator, defined as: *A = B With B = B n B n-1 … B 1 B 1 = A 1 B 2 = A 1 * A 2 B 3 = A 1 * A 1 * A 3 … and ‘ * ’ here is the integer addition operation.

Example of prefix sum Calculation of *A, where A = 6 5 4 3 2 1 yields: B = *A = 21 15 10 6 3 1 Because the summation is associative the calculation can be done in parallel in the following manner: Parallel implementation versus Serial implementation 6 6 5 5 4 4 3 3 2 2 1 1 6 6 5 5 4 4 3 3 2 2 1 1 + + + + B 3 = (A 1 + A 2) + A B 1 = A1 = 1 B 2 = A 1 + A 2 = 3 + B 6 = A 6 +… +A 1 3 + + = (A 6 + A 5 ) + + = 6 + + ((A 4 +A 3 ) +(A 2 +A 1 )) + = 21 + B 6 B 6 B 5 B 5 B 4 B 4 B 3 B 3 B 2 B 2 B 1 B 1 B 6 B 6 B 5 B 5 B 4 B 4 B 3 B 3 B 2 B 2 B 1 B 1

Binary Addition This is the pen and paper addition of two 4-bit binary numbers x and y . c represents the generated carries. s represents the produced sum bits. c 3 c 2 c 1 c 0 x 3 x 2 x 1 x 0 A stage of the addition is the set of + x and y bits being used to produce y 3 y 2 y 1 y 0 the appropriate sum and carry bits. s 4 s 3 s 2 s 1 s 0 For example the highlighted bits x 2 , y 2 constitute stage 2 which generates carry c 2 and sum s 2 . Each stage i i adds bits a i , b i , c i-1 and produces bits s i , c i The following hold: a i b i c i Comment: Formal definition: = + k x y 0 0 0 The stage “kills” an incoming carry. “Kill” bit: i i i 0 1 c i-1 The stage “propagates” an incoming carry “Propagate” bit: = ⊕ p x y i i i 1 0 c i-1 The stage “propagates” an incoming carry = • g x y 1 1 1 The stage “generates” a carry out “Generate” bit: i i i

Binary Addition a i b i c i Comment: Formal definition: = + 0 0 0 The stage “kills” an incoming carry. “Kill” bit: k x y i i i 0 1 c i-1 The stage “propagates” an incoming carry “Propagate” bit: = ⊕ p x y i i i 1 0 c i-1 The stage “propagates” an incoming carry = • g x y 1 1 1 The stage “generates” a carry out “Generate” bit: i i i The carry c i generated by a stage i i is given by the equation: ( ) = + ⋅ = ⋅ + ⊕ ⋅ c g p c x y x y c − − i i i i 1 i i i i i 1 ( ) This equation can be simplified to: = ⋅ + + ⋅ = + ⋅ c x y x y c g a c − − i i i i i i i i i 1 1 The “a i ” term in the equation being the “alive” bit. The later form of the equation uses an OR gate instead of an XOR which is a more efficient gate when implemented in CMOS technology. Note that: a = k i i Where k i is the “kill” bit defined in the table above.

Carry Look Ahead adders The CLA adder has the following 3-stage structure: Pre-calculation of p i , g i for each stage Calculation of carry c i for each stage. Combine c i and p i of each stage to generate the sum bits s i Final sum.

Carry Look Ahead adders � The pre-calculation stage is implemented using the equations for p i , g i shown at a previous slide: x 1 y 1 x 0 y 0 x 2 y 2 g 1 p 1 g 0 p 0 g 2 p 2 � Alternatively using the “alive” bit: x 1 y 1 x 0 y 0 x 2 y 2 g 1 a 1 g 0 a 0 g 2 a 2 � Note the symmetry when we use the “propagate” or the “alive” bit… We can use them interchangeably in the equations!

Carry Look Ahead adders � The carry calculation stage is implemented using the equations produced when unfolding the recursive equation: = + ⋅ = + ⋅ c g p c g a c − − i i i i i i i 1 1 g 1 p 1 g 0 p 0 g 2 p 2 = c g 0 0 = + ⋅ c g p g 1 1 1 0 ( ) = + ⋅ = + ⋅ + ⋅ c g p c g p g p g Carry generator block 2 2 2 1 2 2 1 1 0 = + ⋅ + ⋅ ⋅ g p g p p g 2 2 1 2 1 0 K etc c 2 c 1 c 0

Carry Look Ahead adders � The final sum calculation stage is implemented using the carry and propagate bits c i ,p i : = ⊕ = ⊕ s p c , with p x y − i i i 1 i i i Note : = + ⋅ = + s g a c , with a x y − i i i i 1 i i i c 2 p 3 c 1 p 2 c 0 p 1 c in p 0 s 3 s 2 s 1 s 0 � If the ‘alive’ bit a i is used the final sum stage becomes more complex as implied by the equations above.

Binary addition as a prefix sum problem. � We define a new operator: “ ° ” � Input is a vector of pairs of ‘propagate’ and ‘generate’ bits: ( )( ) ( ) K g , p g , p g , p − − n n n 1 n 1 0 0 � Output is a new vector of pairs: ( )( ) ( ) K G , P G , P G , P − − n n n 1 n 1 0 0 � Each pair of the output vector is calculated by the following definition: = o G P g p G P ( , ) ( , ) ( , ) − − i i i i i 1 i 1 Where : = ( G , P ) ( g , p ) 0 0 0 0 = + ⋅ ⋅ o ( g , p ) ( g , p ) ( g p g , p p ) x x y y x x y x y + ⋅ with , being the OR , AND operations

Binary addition as a prefix sum problem. � Properties of operator “ ° ”: � Associativity (hence parallelization) � Easy to prove based on the fact that the logical AND, OR operations are associative. � With the definition: = o ( G , P ) ( g , p ) ( G , P ) − − i i i i i 1 i 1 = Where ( G , P ) ( g , p ) 1 1 1 1 G i becomes the carry signal at stage i of an adder. Illustration on next slide. � The operation is idempotent = + ⋅ ⋅ = o ( g , p ) ( g , p ) ( g p g , p p ) ( g , p ) x x x x x x x x x x x � Which implies = o ( G , P ) ( G , P ) ( G , P ) i : j i : j i : n i : n m : j m : j ≥ ≥ Where i j and m n

Binary Addition as a prefix sum problem. A stage i will generate a carry if g i =a i b i a 3 a 2 a 1 a 0 and propagate a carry if + p i =XOR(a i, b i ) b 3 b 2 b 1 b 0 Hence for stage i: c i =g i +p i c i - 1 With Where : : = = o ( G , P ) ( g , p ) ( G , P ) ( g , p ) ( G , P ) − − 0 0 0 0 i i i i i 1 i 1 = + ⋅ ⋅ o g p g p g p g p p ( , ) ( , ) ( , ) x x y y x x y x y … The familiar We have : carry bit generating = ( G , P ) ( g , p ) equations for stage i i 1 1 1 1 = = + ⋅ ⋅ in a CLA adder. o G P g p G P g p g p p ( , ) ( , ) ( , ) ( , ) 2 2 2 2 1 1 2 2 1 2 1 = = + ⋅ + ⋅ ⋅ ⋅ o G P g p G P g p g p g p p p ( , ) ( , ) ( , ) ( ( ), ) 3 3 3 3 2 2 3 3 2 2 1 3 2 1 = + ⋅ + ⋅ ⋅ ⋅ ⋅ ( g p g p p g ), p p p ) 3 3 2 3 2 1 3 2 1 K etc

Addition as a prefix sum problem. Conclusion: The equations of the well known CLA adder can be formulated as a parallel prefix problem by employing a special operator “ ° ”. This operator is associative hence it can be implemented in a parallel fashion. A Parallel Prefix Adder (PPA) is equivalent to the CLA adder… The two differ in the way their carry generation block is implemented. In subsequent slides we will see different topologies for the parallel generation of carries. Adders that use these topologies are called Parallel Prefix Adders .

Parallel Prefix Adders � The parallel prefix adder employs the 3-stage structure of the CLA adder. The improvement is in the carry generation stage which is the most intensive one: Straight forward as Pre-calculation of P i , G i terms in the CLA adder Prefix graphs Calculation of the carries. can be used to describe the This part is parallelizable to structure that reduce time. performs this part. Simple adder to generate the sum Straight forward as in the CLA adder

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.