} (pages and frames, respectively) free frames can be tracked using a - PowerPoint PPT Presentation

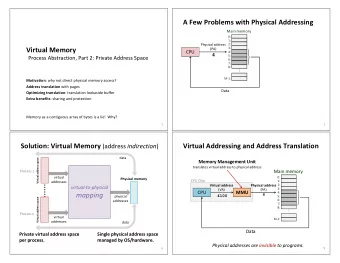

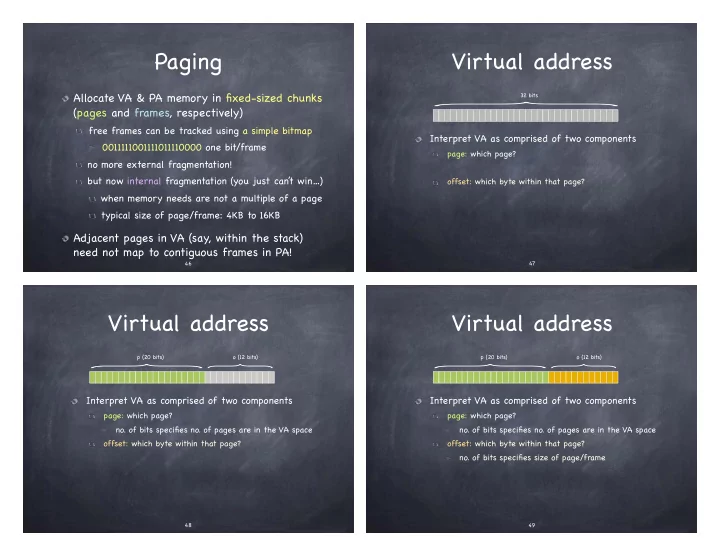

Paging Virtual address Allocate VA & PA memory in fixed-sized chunks 32 bits } (pages and frames, respectively) free frames can be tracked using a simple bitmap Interpret VA as comprised of two components 0011111001111011110000 one bit/frame

Paging Virtual address Allocate VA & PA memory in fixed-sized chunks 32 bits } (pages and frames, respectively) free frames can be tracked using a simple bitmap Interpret VA as comprised of two components 0011111001111011110000 one bit/frame page: which page? no more external fragmentation! but now internal fragmentation (you just can’ t win…) offset: which byte within that page? when memory needs are not a multiple of a page typical size of page/frame: 4KB to 16KB Adjacent pages in VA (say, within the stack) need not map to contiguous frames in PA! � 46 � 47 Virtual address Virtual address p (20 bits) o (12 bits) p (20 bits) o (12 bits) } } } } Interpret VA as comprised of two components Interpret VA as comprised of two components page: which page? page: which page? no. of bits specifies no. of pages are in the VA space no. of bits specifies no. of pages are in the VA space offset: which byte within that page? offset: which byte within that page? no. of bits specifies size of page/frame � 48 � 49

Physical Memory Virtual address Basic Paging p (20 bits) o (12 bits) CPU o f } } p o Page Table To access a byte Page Table 2 20 -1 8 (stores frame nos) f extract page number . . . map that page number into a frame . f . number using a page table . . The Page Table . extract offset . lives in memory . p . access byte at offset in frame at the physical address stored 4 4 in the Page Table Base Register 0 3 2 6 PTBR saved/restored on 1 PTBR 1 context switch 0 2 � 50 � 51 Page Table Entries Sharing Referenced Caching Modified Protection Frame number Valid disabled By now, it’ s old hat: Valid/Invalid bit Frame no. Processes share pages by Set if entry stores a valid Physical mapping virtual pages to Page Table Physical Protection mapping If not, page fault Page table memory Page Table Process 1 Memory bits (R/W/X) the same frame Process 0 } 15 4 i Cache modified bit Caching 14 11 Fine tuning using 7 i 7 disabled 13 2 i Set for memory-mapped I/O protection bits (RWX) 2 12 Referenced 0 i 6 11 7 v 9 Referenced bit Modified 10 6 i 5 We can refine COW to operate 9 5 v 4 at the granularity of pages 4 Set if page has been referenced 8 4 i Valid/ invalid 7 2 i 5 on fork, mark all pages 3 6 0 i Modified bit 5 3 v 0 read only 2 4 4 v Set if page has been modified 3 0 v 1 on write, copy only the 1 2 6 v affected page 3 Protection bits (R/W/X) 1 1 v 0 0 2 v � 52 � 53

0 Example Space overhead PA Space VA I 1 J Space Page size: 4 bytes Two sources, in tension: K 0 A data structure overhead (the Page Table itself) L B Page fragmentation 2 C Table How large should a page be? D 0 4 Overhead for paging: E 1 F E 1 3 (#entries x sizeofEntry) + (#“segments” x pageSize/2) = 3 G F = ((VA_Size/pagesize) x sizeofEntry) + (#“segments” x pageSize/2) H G 2 1 I H 2 Size of entry J A 4 enough bits to identify physical page (log 2 (PA_Size / page size)) K B should include control bits (valid, modified, referenced, etc) L C usually word or byte aligned D � 55 Computing paging What’ s not to love? overhead Space overhead 1 MB maximum VA, 1 KB page, 3 segments (program, stack, heap) With a 64-bit address space, size of page table can ((2 20 / 2 10 ) x sizeofEntry) + (3 x 2 9 ) be huge If I know PA is 64 KB then sizeofEntry = 6 bits (2 6 Time overhead frames) + control bits if 7 control bits, byte aligned size of entry: 16 bits Accessing data now requires two memory accesses must also access page table, to find mapped frame � 56 � 57

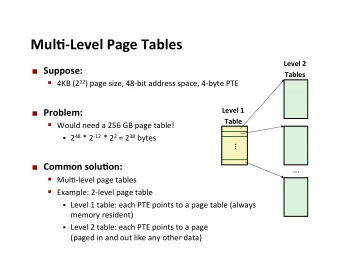

Reducing the Storage Reducing the Storage Overhead of Page Tables Overhead of Page Tables Size of the page table } Size of the page table } VP 0 PTE 0 VP 0 . . . . . . . . . for a machine with 64- for a machine with 64- 2K pages 2K pages VP 1023 PTE 1023 VP 1023 code/data code/data bit addresses and a bit addresses and a PTE 0 VP 1024 VP 1024 . . . PTE 1 . . . page size of 4KB? page size of 4KB? PTE 0 PTE 2 (null) VP 2047 VP 2047 . . . PTE 3 (null) } } an array of 2 52 an array of 2 52 PTE 1023 PTE 4 (null) 6K pages 6K pages entries! entries! PTE 5 (null) Gap Gap unallocated unallocated PTE 6 (null) PTE 7 (null) Good news Good news PTE 8 } } 1023 1023 1023 pages 1023 null 1023 pages most space is unused most space is unused unallocated unallocated (9-1024) unallocated PTEs unallocated pages null PTEs pages PTE 1023 1 page 1 page Use a better data VP 9215 Use a better data VP 9215 for stack for stack structure to express structure to express unallocated unallocated Example pages Example pages the Page Table the Page Table 32 bit address space 32 bit address space a tree! a tree! 4Kb pages 4Kb pages 4 bytes PTE 4 bytes PTE � 58 � 59 Multi-level Paging Example 10 bits 8 bits 6 bits 8 bits } } } } Structure virtual address space as a tree Virtual address of a SPARC What is the page size? 63 p 1 p 2 p 3 o 63 v 8 6 6 12 p 3 p 2 0 255 0 16K 8K p 1 4K 1 0 0 PTBR

Example Example 10 bits 8 bits 6 bits 8 bits 10 bits 8 bits 6 bits 8 bits } } } } } } } } What is the page size? What is the page size? Page size is 256 bytes Page size is 256 bytes What is the Page Table size for a process with a 256KB What is the Page Table size for a process with a 256KB VAS starting at address 0? VAS starting at address 0? The process needs to map 1024 pages (256KB/256 bytes) To do so, it is sufficient to materialize the following tree 0 since 1024/ 64 = 16 } 64 entries 1 So, assuming each PTE is 2 bytes 256 } entries } 1024 x 2 + 256 x 2 + 16 x 64 x 2 = 4608 bytes 1024 15 entries

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![ni Txizx ] " Independence, Continued Example: Max of Two Exponentials Min of n Uniforms](https://c.sambuz.com/837031/ni-s.webp)