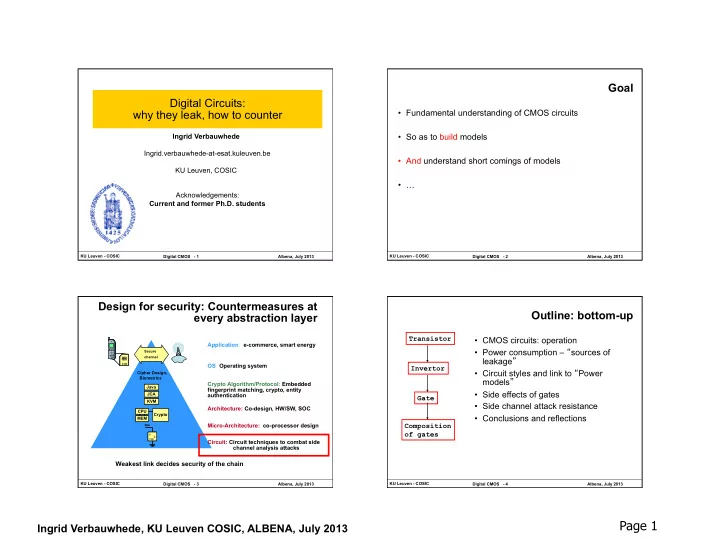

Page 1 Ingrid Verbauwhede, KU Leuven COSIC, ALBENA, July 2013 - PowerPoint PPT Presentation

Goal Digital Circuits: Fundamental understanding of CMOS circuits why they leak, how to counter Ingrid Verbauwhede So as to build models Ingrid.verbauwhede-at-esat.kuleuven.be And understand short comings of models KU Leuven, COSIC

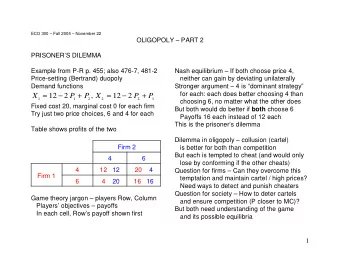

Goal Digital Circuits: • Fundamental understanding of CMOS circuits why they leak, how to counter Ingrid Verbauwhede • So as to build models Ingrid.verbauwhede-at-esat.kuleuven.be • And understand short comings of models KU Leuven, COSIC • … Acknowledgements: Current and former Ph.D. students KU Leuven - COSIC KU Leuven - COSIC Digital CMOS - 1 Albena, July 2013 Digital CMOS - 2 Albena, July 2013 Design for security: Countermeasures at Outline: bottom-up every abstraction layer Transistor • CMOS circuits: operation Application: e-commerce, smart energy • Power consumption – “ sources of Secure channel leakage ” SIM SIM SIM SIM OS: Operating system Invertor Cipher Design, • Circuit styles and link to “ Power Biometrics models ” Crypto Algorithm/Protocol: Embedded Java Java fingerprint matching, crypto, entity JCA JCA authentication • Side effects of gates Gate JVM KVM • Side channel attack resistance Architecture: Co-design, HW/SW, SOC CPU CPU Crypto MEM MEM • Conclusions and reflections Vcc Vcc Micro-Architecture: co-processor design Composition D Q D Q of gates CLK CLK Circuit: Circuit techniques to combat side channel analysis attacks Weakest link decides security of the chain KU Leuven - COSIC Digital CMOS - 3 Albena, July 2013 KU Leuven - COSIC Digital CMOS - 4 Albena, July 2013 Page 1 Ingrid Verbauwhede, KU Leuven COSIC, ALBENA, July 2013

Outline Transistor • CMOS circuits: operation • Power consumption – “ sources of leakage ” Invertor – Current CMOS invertor – Dynamic power – Static power power and energy fundamentals KU Leuven - COSIC KU Leuven - COSIC Digital CMOS - 5 Albena, July 2013 Digital CMOS - 6 Albena, July 2013 CMOS Inverter The CMOS Inverter: A First Glance The image cannot be N Well displayed. Your V V DD computer may not DD have enough memory V DD to open the image, or the image may have PMOS 2 λ been corrupted. Restart your computer, and then Contacts open the file again. If the red x still appears, you may have to PMOS delete the image and then insert it again. V V in out In Out Out In Polysilicon Metal 1 C L NMOS NMOS GND Slide courtesy: J. Rabaey Slide courtesy: J. Rabaey KU Leuven - COSIC Digital CMOS - 7 Albena, July 2013 KU Leuven - COSIC Digital CMOS - 8 Albena, July 2013 Page 2 Ingrid Verbauwhede, KU Leuven COSIC, ALBENA, July 2013

Two Inverters CMOS Inverter: First-Order DC Analysis Share power and ground = STATIC behavior V V DD DD Abut cells R p V OL = 0 V DD V OH = V DD Connect in Metal V M = f(R n , R p ) V out V out R n Why we like CMOS!! V in 5 V V in 5 0 DD Slide courtesy: J. Rabaey Slide courtesy: J. Rabaey KU Leuven - COSIC KU Leuven - COSIC Digital CMOS - 9 Albena, July 2013 Digital CMOS - 10 Albena, July 2013 CMOS Inverter: Transient Response Where Does Power Go in CMOS? = DYNAMIC behavior V V DD DD • Dynamic Power Consumption t = f(R .C ) • Charging and discharging capacitors pHL on L R p = 0.69 R C on L • Short Circuit Currents • Short circuit path between supply rails V out V out during switching C L • No longer an issue in deep submicron C L R n • Leakage • Leaking diodes and transistors V in 5 0 V in 5 V DD (a) Low-to-high (b) High-to-low Slide courtesy: J. Rabaey KU Leuven - COSIC Digital CMOS - 11 Albena, July 2013 KU Leuven - COSIC Digital CMOS - 12 Albena, July 2013 Page 3 Ingrid Verbauwhede, KU Leuven COSIC, ALBENA, July 2013

Dynamic Power Dissipation Leakage current Vdd Vdd T Vin h Vout e i m Vout C L Drain Junction 2 Leakage Energy/transition = C * V L dd 2 Power = Energy/transition * f = C * V * f L dd Sub-Threshold Current Not a function of transistor sizes! Sub-threshold current one of most compelling issues Need to reduce C , V , and f to reduce power. L dd in low-energy circuit design! • Strong function of temperature • New source of side-channel leakage = State! KU Leuven - COSIC KU Leuven - COSIC Digital CMOS - 13 Albena, July 2013 Digital CMOS - 14 Albena, July 2013 Outline • CMOS circuits: operation • Power consumption – “ sources of leakage ” • Circuit styles and link to “ Power models ” – Static CMOS Static CMOS – Dynamic, pre-charged CMOS – Differential CMOS – Dynamic – differential CMOS Gate – Link to Hamming Weight – Hamming Distance • Side effects of gates Basics and construction rules • Side channel attack resistance • Conclusions and reflections KU Leuven - COSIC Digital CMOS - 15 Albena, July 2013 KU Leuven - COSIC Digital CMOS - 16 Albena, July 2013 Page 4 Ingrid Verbauwhede, KU Leuven COSIC, ALBENA, July 2013

Static Complementary CMOS NMOS Transistors in Series/Parallel Connection V DD Transistors can be thought as a switch controlled by its gate signal NMOS switch closes when switch control input is high In1 PMOS only In2 PUN … A B InN F(In1,In2, … InN) Y = X if A and B X Y In1 A In2 PDN … NMOS only InN B X Y = X if A OR B Y PUN and PDN are dual logic networks NMOS Transistors pass a “strong” 0 but a “weak” 1 KU Leuven - COSIC KU Leuven - COSIC Digital CMOS - 17 Albena, July 2013 Digital CMOS - 18 Albena, July 2013 Complementary CMOS Logic Style PMOS Transistors in Series/Parallel Connection PMOS switch closes when switch control input is low A B X Y = X if A AND B = A + B Y A B Y = X if A OR B = AB X Y PMOS Transistors pass a “strong” 1 but a “weak” 0 KU Leuven - COSIC Digital CMOS - 19 Albena, July 2013 KU Leuven - COSIC Digital CMOS - 20 Albena, July 2013 Page 5 Ingrid Verbauwhede, KU Leuven COSIC, ALBENA, July 2013

Example Gate: NAND Example Gate: NOR Quiz: preference for NAND or NOR? KU Leuven - COSIC KU Leuven - COSIC Digital CMOS - 21 Albena, July 2013 Digital CMOS - 22 Albena, July 2013 Complex CMOS Gate Static CMOS Properties: ROBUST • Full rail-to-rail swing; high noise margins • Logic levels not dependent upon the relative device sizes; B ratioless A • Always a path to Vdd or Gnd in steady state; low output C impedance • Extremely high input resistance; nearly zero steady-state input D current • No direct path steady state between power and ground; no static OUT = D + A • (B + C) power dissipation A • Propagation delay function of load capacitance and resistance of D transistors B C • Style of choice for standard cell based design! KU Leuven - COSIC Digital CMOS - 23 Albena, July 2013 KU Leuven - COSIC Digital CMOS - 24 Albena, July 2013 Page 6 Ingrid Verbauwhede, KU Leuven COSIC, ALBENA, July 2013

Standard Cell Zoom In Module Generation For data-path operators: structure is in bit-slices Computer generated layout as function of wordlength Compact, predictable IP Instruction, Clock vdd Power vss Data layout KU Leuven - COSIC KU Leuven - COSIC Digital CMOS - 25 Albena, July 2013 Digital CMOS - 26 Albena, July 2013 Standard Cell and Module Standard Cell Datapath Random Logic More levels of metal: top levels not shown Courtesy: J. Van Campenhout RUG Few levels of metal KU Leuven - COSIC Digital CMOS - 27 Albena, July 2013 KU Leuven - COSIC Digital CMOS - 28 Albena, July 2013 Page 7 Ingrid Verbauwhede, KU Leuven COSIC, ALBENA, July 2013

Dynamic CMOS • In static circuits at every point in time (except when switching) the output is connected to either GND or V DD via a low resistance path. – fan-in of n requires 2 n ( n N-type + n P-type) devices Dynamic CMOS • Dynamic circuits rely on the temporary storage of signal values on the capacitance of high impedance nodes. Basics and construction rules – requires on n + 2 ( n +1 N-type + 1 P-type) transistors KU Leuven - COSIC KU Leuven - COSIC Digital CMOS - 29 Albena, July 2013 Digital CMOS - 30 Albena, July 2013 Dynamic Gate Conditions on Output • Once the output of a dynamic gate is discharged, it cannot be charged again until the next precharge operation. off Clk Clk M p M p on • Inputs to the gate can make at most one transition during 1 Out Out evaluation. ((AB)+C) In 1 C L A In 2 PDN • Output can be in the high impedance state during and after C In 3 evaluation (PDN off), state is stored on C L B Clk M e off Thus by construction, dynamic gates cannot glitch! M e Clk on Two phase operation Precharge (Clk = 0) Evaluate (Clk = 1) KU Leuven - COSIC Digital CMOS - 31 Albena, July 2013 KU Leuven - COSIC Digital CMOS - 32 Albena, July 2013 Page 8 Ingrid Verbauwhede, KU Leuven COSIC, ALBENA, July 2013

Cascading Dynamic Gates Domino Logic V Clk M p M kp Clk M p Clk Clk Clk Out1 Out2 M p M p 1 → 1 Out2 1 → 0 Out1 0 → 0 In 1 In 0 → 1 In In 4 PDN In 2 PDN In 5 V Tn In 3 Clk Clk M e M e Out1 Clk M e Clk M e Δ V Out2 t All inputs to dynamic gate are set to 0 at end of precharge phase. So only 0 to 1 possible during evaluation. Only 0 → 1 transitions allowed at inputs! Moreover, bottom clk transistor is not needed. KU Leuven - COSIC KU Leuven - COSIC Digital CMOS - 33 Albena, July 2013 Digital CMOS - 34 Albena, July 2013 Why Domino? Differential (Dual Rail) Domino off on Clk Clk M p M kp M kp M p Clk Out = AB Out = AB 1 0 1 0 A !A !B In i PDN In i PDN In i PDN In i PDN B In j In j In j In j Clk Clk M e Solves the problem of non-inverting logic Like falling dominos! Can build complex pull-down networks KU Leuven - COSIC Digital CMOS - 35 Albena, July 2013 KU Leuven - COSIC Digital CMOS - 36 Albena, July 2013 Page 9 Ingrid Verbauwhede, KU Leuven COSIC, ALBENA, July 2013

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.