Page 1 ibenik, Croatia, June 2014 Outline Transistor CMOS - PowerPoint PPT Presentation

ibenik, Croatia, June 2014 Goal Digital Circuits: why they leak, how to counter Fundamental understanding of CMOS circuits So as to build models Ingrid Verbauwhede Ingrid.verbauwhede-at-esat.kuleuven.be And understand short

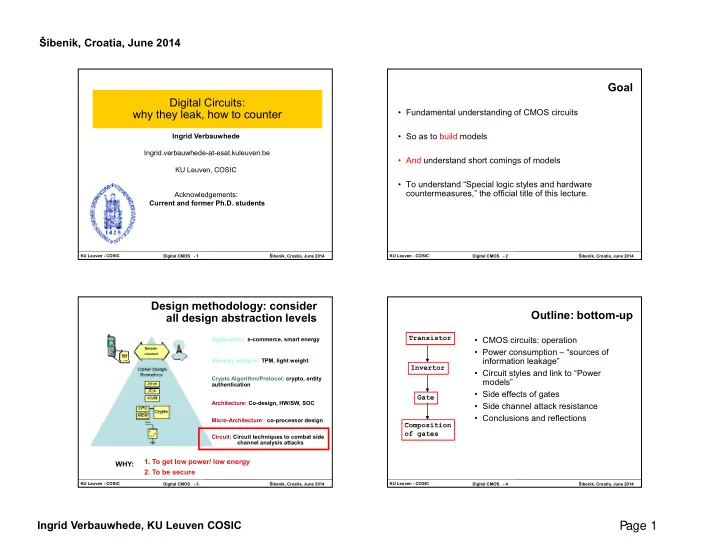

Šibenik, Croatia, June 2014 Goal Digital Circuits: why they leak, how to counter • Fundamental understanding of CMOS circuits • So as to build models Ingrid Verbauwhede Ingrid.verbauwhede-at-esat.kuleuven.be • And understand short comings of models KU Leuven, COSIC • To understand “Special logic styles and hardware countermeasures,” the official title of this lecture. countermeasures, the official title of this lecture. Acknowledgements: Acknowledgements: Current and former Ph.D. students KU Leuven - COSIC KU Leuven - COSIC Digital CMOS - 1 Šibenik, Croatia, June 2014 Digital CMOS - 2 Šibenik, Croatia, June 2014 Design methodology: consider Outline: bottom-up all design abstraction levels Transistor • CMOS circuits: operation Application: e-commerce, smart energy • Power consumption – “sources of information leakage information leakage” Security analysis: TPM light weight? Security analysis: TPM, light weight? Invertor • Circuit styles and link to “Power Crypto Algorithm/Protocol: crypto, entity models” authentication • Side effects of gates Gate Architecture: Co-design, HW/SW, SOC • Side channel attack resistance • Conclusions and reflections Micro-Architecture: co-processor design Composition Composition of gates Circuit: Circuit techniques to combat side channel analysis attacks 1. To get low power/ low energy WHY: 2. To be secure KU Leuven - COSIC Digital CMOS - 3 Šibenik, Croatia, June 2014 KU Leuven - COSIC Digital CMOS - 4 Šibenik, Croatia, June 2014 Ingrid Verbauwhede, KU Leuven COSIC Page 1

Šibenik, Croatia, June 2014 Outline Transistor • CMOS circuits: operation • Power consumption – “sources of information leakage” information leakage Invertor – Current CMOS invertor – Dynamic power – Static power power and energy fundamentals KU Leuven - COSIC KU Leuven - COSIC Digital CMOS - 5 Šibenik, Croatia, June 2014 Digital CMOS - 6 Šibenik, Croatia, June 2014 CMOS Inverter The CMOS Inverter: A First Glance The image cannot be displayed. Your computer may not have enough memory to open the image, or the image may have been corrupted. Restart your computer, and then open the file again. If the red x still appears, you may have to delete the image and then insert it again. N Well VDD V DD V DD PMOS 2 Contacts PMOS V in V out In Out Out In Metal 1 C L Polysilicon NMOS NMOS GND Slide courtesy: J. Rabaey Slide courtesy: J. Rabaey KU Leuven - COSIC Digital CMOS - 7 Šibenik, Croatia, June 2014 KU Leuven - COSIC Digital CMOS - 8 Šibenik, Croatia, June 2014 Ingrid Verbauwhede, KU Leuven COSIC Page 2

Šibenik, Croatia, June 2014 AC/DC of CMOS Inverter: DC Two Inverters V DD V DD Share power and ground = STATIC behavior LEGO style: Abut cells LEGO style: Abut cells R p V OL = 0 V DD V OH = V DD Connect in Metal V out V out R n n Why we like CMOS!! • Full swing • NO DC current!!* V in = V DD V in = 0 *to first order, see further Slide courtesy: J. Rabaey Slide courtesy: J. Rabaey KU Leuven - COSIC KU Leuven - COSIC Digital CMOS - 9 Šibenik, Croatia, June 2014 Digital CMOS - 10 Šibenik, Croatia, June 2014 AC/DC of CMOS Inverter: AC Where Does Power Go in CMOS? = DYNAMIC behavior V DD V DD • Dynamic Power Consumption = AC • Charging and discharging capacitors Charging and discharging capacitors t pHL = f(R on .C L ) R p • [Short Circuit Currents = AC] = 0.69 R on C L • Short circuit path between supply rails during V out V out switching • No longer an issue in deep submicron C L C L R n R n • Leakage = DC SPA, DPA attack AC!! • Leaking diodes and transistors V in = V DD V in = 0 (b) High-to-low (a) Low-to-high Slide courtesy: J. Rabaey KU Leuven - COSIC Digital CMOS - 11 Šibenik, Croatia, June 2014 KU Leuven - COSIC Digital CMOS - 12 Šibenik, Croatia, June 2014 Ingrid Verbauwhede, KU Leuven COSIC Page 3

Šibenik, Croatia, June 2014 AC – Dynamic Power consumption AC – SPA, DPA • SPA and DPA monitor power Vdd • Which values depend on data? – Monitor α , the activity of circuit Vin Vout – Monitor C L , the capacitance • Hamming weight: C L – Measures activity between current and (past) known value – Typically for pre-charged values 2 * α Energy/transition = C L * V dd • Hamming Distance: g Power = Energy/transition * f = C L * V dd 2 * α * f – Measures activity between current and previous value – Typical for standard cell based design • Energy = independent of clock frequency! – Also for FPGA • Energy = depends on activity α ! • Energy, power = independent of transistor sizes • Need to reduce C L , V dd, α and f to reduce power KU Leuven - COSIC KU Leuven - COSIC Digital CMOS - 13 Šibenik, Croatia, June 2014 Digital CMOS - 14 Šibenik, Croatia, June 2014 Example: power model bus CPA – Hamming Weight model • 8 bit bus on a smart card, pre-charged • (relatively) large capacitance • Hamming weight model = numbers of bits set to 1 Side-note: on a pre-charged bus which is pre-set to 1 maximum power Side note: on a pre charged bus which is pre set to 1, maximum power consumption is for data all zero. KU Leuven - COSIC Digital CMOS - 15 Šibenik, Croatia, June 2014 KU Leuven - COSIC Digital CMOS - 16 Šibenik, Croatia, June 2014 Ingrid Verbauwhede, KU Leuven COSIC Page 4

Šibenik, Croatia, June 2014 AC - Correlation Power Analysis • R := reference state – Which bit pattern was previously present? E.g. A A pre-charged value h d l An opcode on the bus DC A previously stored value in a register • Power model: leakage currents as a HW ( SBox ( x k ) R ) b i Side channel information leakage Side-channel information leakage a,b are constant, linear model HW is defined as Hamming Weight = counts number of 1’s. KU Leuven - COSIC KU Leuven - COSIC Digital CMOS - 17 Šibenik, Croatia, June 2014 Digital CMOS - 18 Šibenik, Croatia, June 2014 Vt and Vdd effect on leakage DC - Leakage current V DD • Vt, Vdd combination for low power, given a target clock frequency Power [arb. Unit] V V in V V out Leakage Dynamic Drain Junction Total leakage Subthreshold current V DD [V] V DD [V] DD [ ] Problem in deep submicron (below 45 nm) Problem in deep submicron (below 45 nm) Depends strongly on “threshold voltage” Vt 10x more switching • Vt is set by processing • “High Vt” “low Vt” Standard cell library High performance microprocessor Memory → dynamic power dominance • Low power FPGAs vs High performance FPGAs → Leakage dominance [slide credit: Wim Dehaene] KU Leuven - COSIC Digital CMOS - 19 Šibenik, Croatia, June 2014 KU Leuven - COSIC Digital CMOS - 20 Šibenik, Croatia, June 2014 Ingrid Verbauwhede, KU Leuven COSIC Page 5

Šibenik, Croatia, June 2014 DC – leakage of NAND gate Outline Transistor • CMOS circuits: operation • Power consumption – “sources of leakage” • Circuit styles and link to Power models • Circuit styles and link to “Power models” Vdd Vdd Vdd Invertor – Static CMOS – Dynamic, pre-charged CMOS A=0 A=0 A=Vdd – Differential CMOS I3 I2 I1 – Dynamic – differential CMOS B=Vdd B=0 B=0 Gate Gate – Link to Hamming Weight – Hamming Distance • Side effects of gates • Side channel attack resistance Nand gate: out = 1 , but I1 ≠ I2 ≠ I3 Nand gate: out = ‘1’ but I1 ≠ I2 ≠ I3 • Conclusions and reflections • New source of information, If you are looking for a nice research topic. • Available even when device is at ‘rest’ • Time window to attack larger • Less a problem for memory because differential structure KU Leuven - COSIC KU Leuven - COSIC Digital CMOS - 21 Šibenik, Croatia, June 2014 Digital CMOS - 22 Šibenik, Croatia, June 2014 Standard cell automated design flow Design Capture Behavioral Behavioral HDL HDL Pre-Layout Pre-Layout Design Iteration Design Iteration Structural Structural Simulation Simulation Static CMOS Logic Synthesis Logic Synthesis Floorplanning Floorplanning Basics and construction rules Post-Layout Post-Layout Simulation Simulation Placement Placement Physical Physical y Circuit Extraction Circuit Extraction Routing Routing Tape-out Timing closure! Technology/library/manufacturer input KU Leuven - COSIC Digital CMOS - 23 Šibenik, Croatia, June 2014 KU Leuven - COSIC Digital CMOS - 24 Šibenik, Croatia, June 2014 Ingrid Verbauwhede, KU Leuven COSIC Page 6

Šibenik, Croatia, June 2014 Standard Cell Zoom In vdd vss layout y More levels of metal: top levels not shown KU Leuven - COSIC KU Leuven - COSIC Digital CMOS - 25 Šibenik, Croatia, June 2014 Digital CMOS - 26 Šibenik, Croatia, June 2014 Glitches in static CMOS networks Most famous example: RippleCarry Adder A X B Z C C Add0 Add0 Add1 Add1 Add2 Add2 Add14 Add14 Add15 Add15 C C in [MJI] S0 S1 S2 S14 S15 ABC 101 000 Voltage, Volts C X X 4.0 4 S15 Glitch Z 6 Sum Output 2.0 3 S10 Cin 5 Unit Delay S1 2 Glitch = Useless transition = Waste of energy 0.0 0 5 10 [Low Power community has addressed this] From Rabaey From Rabaey, , 1995 1995 Time, ns Design for low power Design for low power KU Leuven - COSIC Digital CMOS - 27 Šibenik, Croatia, June 2014 KU Leuven - COSIC Digital CMOS - 28 Šibenik, Croatia, June 2014 Ingrid Verbauwhede, KU Leuven COSIC Page 7

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.