Overview: TPG and RC Motivation and economics ECE 553: TESTING AND - PDF document

11/20/2014 Overview: TPG and RC Motivation and economics ECE 553: TESTING AND Definitions TESTABLE DESIGN OF Built-in self-testing (BIST) process BIST pattern generation (PG) BIST pattern generation (PG) DIGITAL SYSTEMS

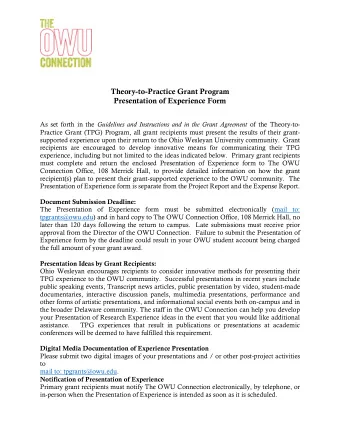

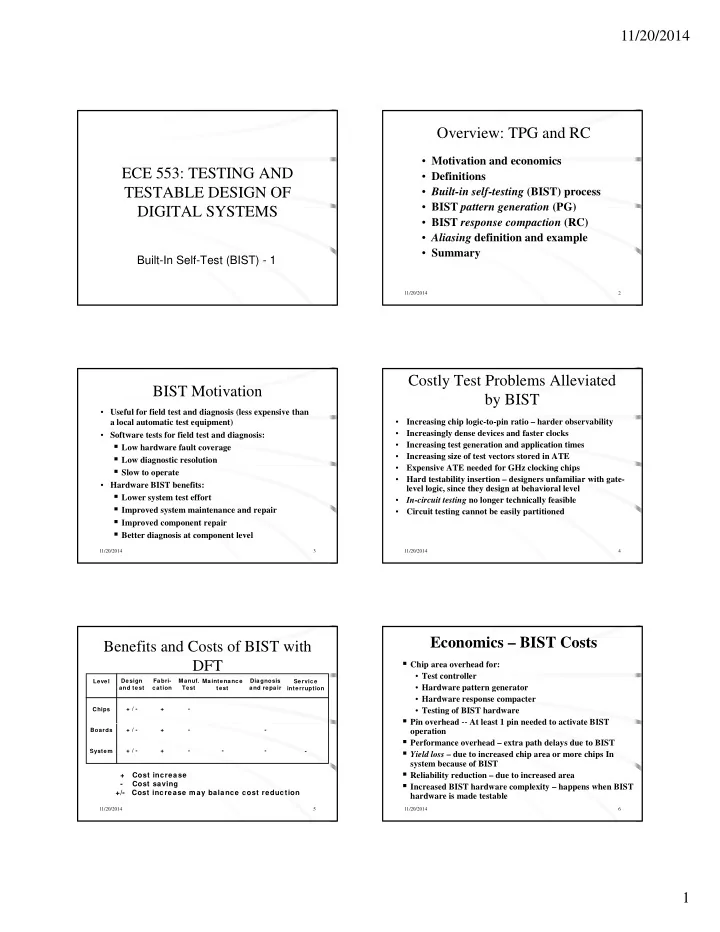

11/20/2014 Overview: TPG and RC • Motivation and economics ECE 553: TESTING AND • Definitions TESTABLE DESIGN OF • Built-in self-testing (BIST) process • BIST pattern generation (PG) • BIST pattern generation (PG) DIGITAL SYSTEMS DIGITAL SYSTEMS • BIST response compaction (RC) • Aliasing definition and example • Summary Built-In Self-Test (BIST) - 1 11/20/2014 2 Costly Test Problems Alleviated BIST Motivation by BIST • Useful for field test and diagnosis (less expensive than a local automatic test equipment) • Increasing chip logic-to-pin ratio – harder observability • Increasingly dense devices and faster clocks • Software tests for field test and diagnosis: Low hardware fault coverage Increasing test generation and application times • Low diagnostic resolution Increasing size of test vectors stored in ATE • • Expensive ATE needed for GHz clocking chips E i ATE d d f GH l ki hi Slow to operate • Hard testability insertion – designers unfamiliar with gate- • Hardware BIST benefits: level logic, since they design at behavioral level Lower system test effort In-circuit testing no longer technically feasible • Improved system maintenance and repair Circuit testing cannot be easily partitioned • Improved component repair Better diagnosis at component level 11/20/2014 3 11/20/2014 4 Economics – BIST Costs Benefits and Costs of BIST with Chip area overhead for: DFT • Test controller Design Fabri- Manuf. Maintenance Diagnosis Level Service • Hardware pattern generator and test cation Test test and repair interruption • Hardware response compacter Chips + / - + - • Testing of BIST hardware Pin overhead -- At least 1 pin needed to activate BIST Pin overhead At least 1 pin needed to activate BIST Boards + / - + - - operation Performance overhead – extra path delays due to BIST Yield loss – due to increased chip area or more chips In System + / - + - - - - system because of BIST Reliability reduction – due to increased area + Cost increase Increased BIST hardware complexity – happens when BIST - Cost saving +/- Cost increase may balance cost reduction hardware is made testable 11/20/2014 5 11/20/2014 6 1

11/20/2014 Definitions BIST Benefits • Faults tested: • BILBO – Built-in logic block observer , extra hardware added Single combinational / sequential stuck-at faults to flip-flops so they can be reconfigured as an LFSR pattern Delay faults generator or response compacter, a scan chain, or as flip-flops Single stuck-at faults in BIST hardware • Concurrent testing – Testing process that detects faults during • BIST benefits normal system operation Reduced testing and maintenance cost R d d t ti d i t t • CUT – Circuit-under-test CUT Ci i d Lower test generation cost • Exhaustive testing – Apply all possible 2 n patterns to a circuit Reduced storage / maintenance of test patterns with n inputs Simpler and less expensive ATE • Irreducible polynomial – Boolean polynomial that cannot be Can test many units in parallel factored Shorter test application times • LFSR – Linear feedback shift register, hardware that generates Can test at functional system speed pseudo-random pattern sequence 11/20/2014 7 11/20/2014 8 More Definitions BIST Process • Primitive polynomial – Boolean polynomial p (x) that can be used to compute increasing powers n of x n modulo p (x) to obtain all possible non-zero polynomials of degree less than p (x) • Pseudo-exhaustive testing – Break circuit into small, overlapping blocks and test each exhaustively • Pseudo-random testing – Algorithmic pattern generator that produces a subset of all possible tests with most of the properties of randomly-generated patterns • Test controller – Hardware that activates self-test • Signature – Any statistical circuit property distinguishing simultaneously on all PCBs between bad and good circuits • Each board controller activates parallel chip BIST Diagnosis • TPG – Hardware test pattern generator effective only if very high fault coverage 11/20/2014 9 11/20/2014 10 BIST Architecture BILBO – Works as Both a TPG and a RC • Built-in Logic Block Observer (BILBO) -- 4 modes: • Note: BIST cannot test wires and transistors: 1. Flip-flop From PI pins to Input MUX 2. LFSR pattern generator From POs to output pins 3. LFSR response compacter 4. Scan chain for flip-flops 11/20/2014 11 11/20/2014 12 2

11/20/2014 Bus-Based BIST Architecture Complex BIST Architecture • Testing epoch I: LFSR1 generates tests for CUT1 and CUT2 BILBO2 (LFSR3) compacts CUT1 (CUT2) • Self-test control broadcasts patterns to each CUT over • Testing epoch II: bus – parallel pattern generation BILBO2 generates test patterns for CUT3 • Awaits bus transactions showing CUT’s responses to LFSR3 compacts CUT3 response the patterns: serialized compaction 11/20/2014 13 11/20/2014 14 Exhaustive Pattern Generation (A Counter) Pattern Generation • Store in ROM – too expensive • Exhaustive • Pseudo-exhaustive • Pseudo-random (LFSR) – Preferred method ( ) • Binary counters – use more hardware than LFSR • Modified counters • Test pattern augmentation • Shows that every state and transition works LFSR combined with a few patterns in ROM • For n -input circuits, requires all 2 n vectors Hardware diffracter – generates pattern cluster in • Impractical for large n ( > 20 ) neighborhood of pattern stored in ROM 11/20/2014 15 11/20/2014 16 Pseudo-Exhaustive Pattern Random Pattern Testing Generation Bottom: Random- Pattern Pattern Resistant circuit 11/20/2014 17 11/20/2014 18 3

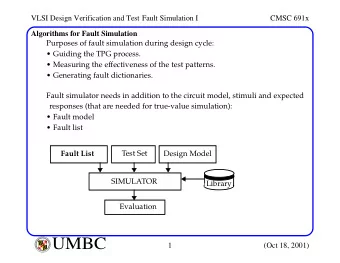

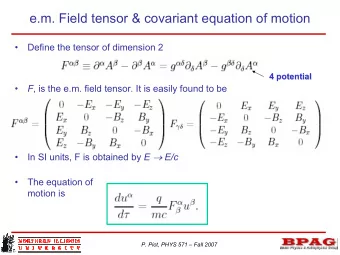

11/20/2014 Pseudo-Random Pattern Generation Theory: LFSRs Galois field (mathematical system): Multiplication by x same as right shift of LFSR Addition operator is XOR ( ) ⊕ T s companion matrix for a standard (external EOR type) LFSR: 1 st column 0, except n th element which is always 1 ( X 0 , p y ( 0 always feeds X n -1 ) Rest of row n – feedback coefficients h i Rest is identity matrix I – means a right shift • Standard Linear Feedback Shift Register (LFSR) Normally known as External XOR type LFSR • Near-exhaustive (maximal length) LFSR Produces patterns algorithmically – repeatable Cycles through 2 n – 1 states (excluding all-0) Has most of desirable random # properties 1 pattern of n 1’s, one of n -1 consecutive 0’s • Need not cover all 2 n input combinations • Long sequences needed for good fault coverage 11/20/2014 19 11/20/2014 20 Standard n -Stage LFSR Matrix Equation for Standard LFSR 0 X 0 ( t + 1) 1 0 … 0 0 X 0 ( t ) 0 X 1 ( t + 1) 0 1 … 0 0 X 1 ( t ) . . . . . . . . . . . . . . . . . . . . . . . . . . . . = = 0 X n -3 ( t + 1) 0 0 … 1 0 X n -3 ( t ) 0 X n -2 ( t + 1) 0 0 … 0 1 X n -2 ( t ) X n -1 ( t + 1) 1 h 1 h 2 … h n -2 h n -1 X n -1 ( t ) X ( t + 1) = T s X ( t ) ( T s is companion matrix ) • If h i = 0, that XOR gate is deleted 11/20/2014 21 11/20/2014 22 Example External XOR LFSR LFSR Theory (contd.) • Cannot initialize to all 0’s – hangs • If X is initial state, progresses through states X , 2 X , T s 3 X , … T s X , T s • Matrix period : • Matrix period : k = I Smallest k such that T s ≡ k LFSR cycle length • Described by characteristic polynomial: f ( x ) = | T s – I X | = 1 + h 1 x + h 2 x 2 + … + h n -1 x n -1 + x n 11/20/2014 23 11/20/2014 24 4

11/20/2014 Example: External XOR LFSR (contd.) External XOR LFSR • Matrix equation: • Pattern sequence for example LFSR (earlier): X 0 ( t + 1) 0 1 0 X 0 ( t ) X 1 ( t + 1) = 0 0 1 X 1 ( t ) X 2 ( t + 1) 1 1 0 X 2 ( t ) X 0 1 0 0 1 0 1 1 1 0 X 1 0 0 1 0 1 1 1 0 0 • Companion matrix: p … 1 X 2 0 1 0 1 1 1 0 0 1 0 1 0 T S 0 0 1 = • Never repeat an LFSR pattern more than 1 1 1 0 time –Repeats same error vector, cancels fault • Characteristic polynomial: – f ( x ) = 1 + x + x 3 effect (read taps from right to left) • Always have 1 and x n terms in polynomial 11/20/2014 25 11/20/2014 26 Modular Internal XOR LFSR Generic Modular (Internal XOR) LFSR • Described by companion matrix T m = T s T • Internal XOR LFSR – XOR gates in between D flip-flops • Equivalent to standard External XOR LFSR With a different state assignment Faster – usually does not matter Same amount of hardware • X ( t + 1) = T m x X (t) • f ( x ) = | T m – I X | = 1 + h 1 x + h 2 x 2 + … + h n -1 x n -1 + x n • Right shift – equivalent to multiplying by x , and then dividing by characteristic polynomial and storing the remainder 11/20/2014 27 11/20/2014 28 Example Modular LFSR Modular LFSR Matrix X 0 ( t + 1) 0 0 … 0 0 1 X 0 ( t ) 0 X 1 ( t + 1) 1 0 0 … 0 0 h 1 X 1 ( t ) 0 0 X 2 ( t + 1) X 2 ( t + 1) 1 1 0 0 … 0 0 0 0 h 2 h 2 X 2 ( t ) X 2 ( t ) . . . . . . . . . . . . . . . . = . . . . . . . . 0 X n -3 ( t + 1) 0 0 … 0 0 X n -3 ( t ) h n -3 0 X n -2 ( t + 1) 0 0 … 1 0 X n -2 ( t ) h n -2 0 X n -1 ( t + 1) 0 0 … 0 1 h n -1 X n -1 ( t ) • f ( x ) = 1 + x 2 + x 7 + x 8 • Read LFSR tap coefficients from left to right 11/20/2014 29 11/20/2014 30 5

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.