Overview Recap Operator Sharing Introduction to Structured VLSI - PowerPoint PPT Presentation

Overview Recap Operator Sharing Introduction to Structured VLSI Design FSMD VHDL V Counters Joachim Rodrigues Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V Joachim Rodrigues, EIT, LTH,

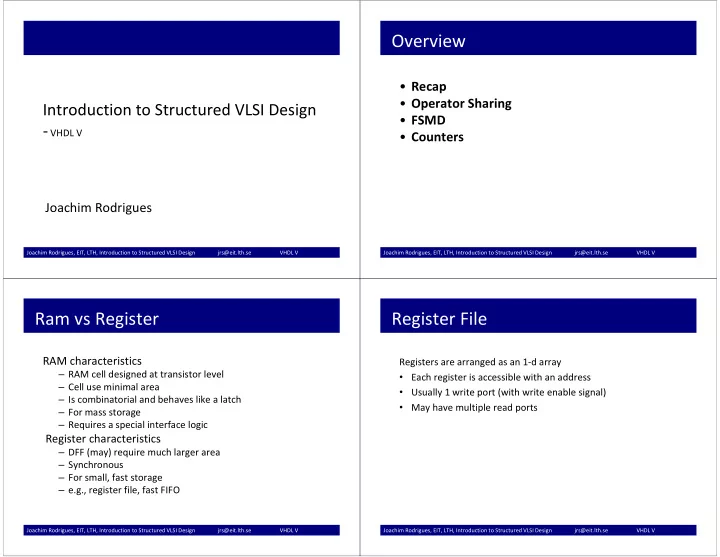

Overview • Recap • Operator Sharing Introduction to Structured VLSI Design • FSMD ‐ VHDL V • Counters Joachim Rodrigues Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V Ram vs Register Register File RAM characteristics Registers are arranged as an 1 ‐ d array – RAM cell designed at transistor level • Each register is accessible with an address – Cell use minimal area • Usually 1 write port (with write enable signal) – Is combinatorial and behaves like a latch • May have multiple read ports – For mass storage – Requires a special interface logic Register characteristics – DFF (may) require much larger area – Synchronous – For small, fast storage – e.g., register file, fast FIFO Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V

Strictly Structured VHDL Strictly Structured VHDL ‐ Advantages • How is it done? Adding a signal in traditional style • Add port in entity declaration – Local signals (r, rin) are stored in records and contain all • Add signal to sensitivity list DUT registered values. • Add port in component declaration – All outputs are stored in a entity specific record type • Add port in component instantiation declared in a global interface package – enables re ‐ use. – Use a local variable (v) of the same type as the registered values. Adding a signal in Strictly Structured VHDL – reset handling moves to combinatorial part. methodology DUT • Add element in record declaration Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V Structured VHDL ‐ Stored signals Configuration • Testbench is reused by declaring a different configuration • A configuration may realize different architectures, memories, etc. Adding a stored signal in traditional style • Add two signals (current, next) Comb • Examples: • Add signal to sensitivity list – A synthesizable model / behavorial model • Add reset value – A synthesizable model / gate ‐ level model • Update on clock edge Current Next Syntax: configuration configuration_name of entity_name is Adding a signal in Structured VHDL methodology for architecture_name • for label |others|all: comp_name Add element in declaration record use entity [ lib_name .] comp_entity_name ( comp_arch_name ) | use configuration [ lib_name .] comp_configuration_name Comb [generic map (...)] [port map (...)] ; r rin end for; ... end for; end configuration_name ; Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V

Operator sharing Operator sharing cont’d Multiplexing network are mutually exclusively: Circuit complexity of VHDL operators varies – Only one result is routed to output – Selected sig assignment (case statement) • Arithmetic operators with select_expression select – Large implementation sig_name <= value_expr_1 when choice_1, value_expr_2 when choice_2, – Limited optimization by synthesis software value_expr_3 when choice_3, • Manual optimization may be forced by operator . . . value_expr_n when choice_n; sharing in RTL – Operator sharing – Functionality sharing Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V Example I Example II Original code: process (a,b,c,d,...) begin Original code: if boolean_exp_1 then r <= a+b; elsif boolean_exp_2 then r <= a+c; r <= a+b when boolean_exp else else r <= d+1; a+c; end if end process; Revised code: process (a,b,c,d,...) begin if boolean_exp_1 then src0 <= a; src1 <= b; elsif boolean_exp_2 then Revised code: src0 <= a; src1 <= c; src0 <= b when boolean_exp else else c; src0 <= d; src1 <= "00000001"; r <= a + src0; end if ; end process ; r <= src0 + src1; Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V

FSMD Example VHDL code • Combination of controller and datapth • Usefule to realize an algortihm in hardware • Example Add 4 numbers Divide the sum by 8 Round the result Task: Convert the algorithm into a combinational circuit Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V Example Register Transfer Methodology Problems with dataflow implementation: Recipe – Can only be applied to trivial algorithm – Use register to store intermediate data and imitate variable – Not flexible – Use a datapath to realize all register operations – Can we just share one adder in a time ‐ multiplexing – Use a control path (FSM) to specify the order of fashion to save hardware resources? register operation – The system is specified as sequence of data manipulation/transfer among registers – Realized by FSM with a datapath (FSMD) Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V

Basic RT operation Example Basic form: Interpretation: – At the rising edge of the clock, the output of registers r src1 r src2 etc. are available. – The output are passed to a combinational circuit that performs f( ). – At the next rising edge of the clock, the result is stored into r dest Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V Multiple Operations Controller FSM is sufficient to control RT operation – State transition is on clock ‐ by ‐ clock basis – FSM can enforce order of execution – FSM allows branches on execution sequence Normally represented in an extended algorithmic state machine chart, known as ASMD (ASM with datapath) chart Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V

ASM chart Example • Used for larger state diagrams, often are easier to interpret. • Conditions for a proper state diagram are automatically satisfied. • Easily converted to other forms. ASM charts do not enumerate all the possible inputs same operations and outputs. Only the inputs that matter and the outputs that are asserted are indicated. New value of r1 is only available when the FSM exits s1 state Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V Registers in Decision Box Basic FSMD Architecture FSM New value of r1 is only available when the FSM exits s1 state Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V

Design Example Design Example cont’d • Sequential Multiplier Input: – 7*5 = 7+7+7+7+7 – a_in, b_in: 8 ‐ bit unsigned Pseudo code: ASMD code – clk, reset – start: command Output: – r: 16 ‐ bit unsigned – ready: status ASMD chart Default RT operation: – keep the previous value – Parallel execution in op state Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V Design Example cont’d Design Example cont’d Recipe to build a data path – List all RT operations RT operation with the r register – Group RT operation according to the r ← r (idle state) destination register r ← 0 (load/op state) r ← r+b (op state) – Add combinational circuit/mux – Add status circuits RT operation with the n register n ← n (idle state) n ← b_in (load/ab0 state) n ← n ‐ 1 (op state) RT operation with the a register a ← a (idle state) a ← a_in (load/ab0 state) Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V

Design Example cont’d Example Operator Sharing s1 • Continue with remaining case d1 ← a*b registers s1 when d1 <= a*b; ... Synthesis tool may infere 3 multipliers s2 when s2 d1 <= b*c; d1 ← a*b ... Expensive in hardware s3 when d1 <= a*c; ... s3 end case ; FSM d1 ← a*b Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V Example Operator Sharing Counters case How can the number of s1 • Binary when case multipers be reduced? in1 <= a; s1 when • Gray counter in2 <= b; d1 <= a*b; ... • Ring counter ... s2 s2 when when in1 <= b; d1 <= b*c; in2 <= c; ... ... s3 when s3 d1 <= a*c; when in1 <= a; ... in2 <= c; end case ; ... end case ; m_out <= in1*in2; Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V Joachim Rodrigues, EIT, LTH, Introduction to Structured VLSI Design jrs@eit.lth.se VHDL V

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.