Overview Motivation Sequential circuit ATPG ECE 553: TESTING AND - PDF document

10/10/2014 Overview Motivation Sequential circuit ATPG ECE 553: TESTING AND An example test generation Time-frame expansion TESTABLE DESIGN OF Nine-valued logic ATPG implementation p DIGITAL SYSTES DIGITAL SYSTES

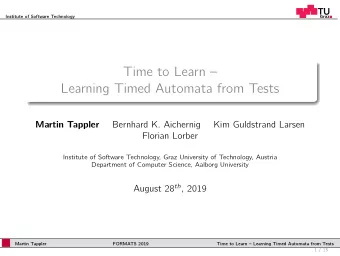

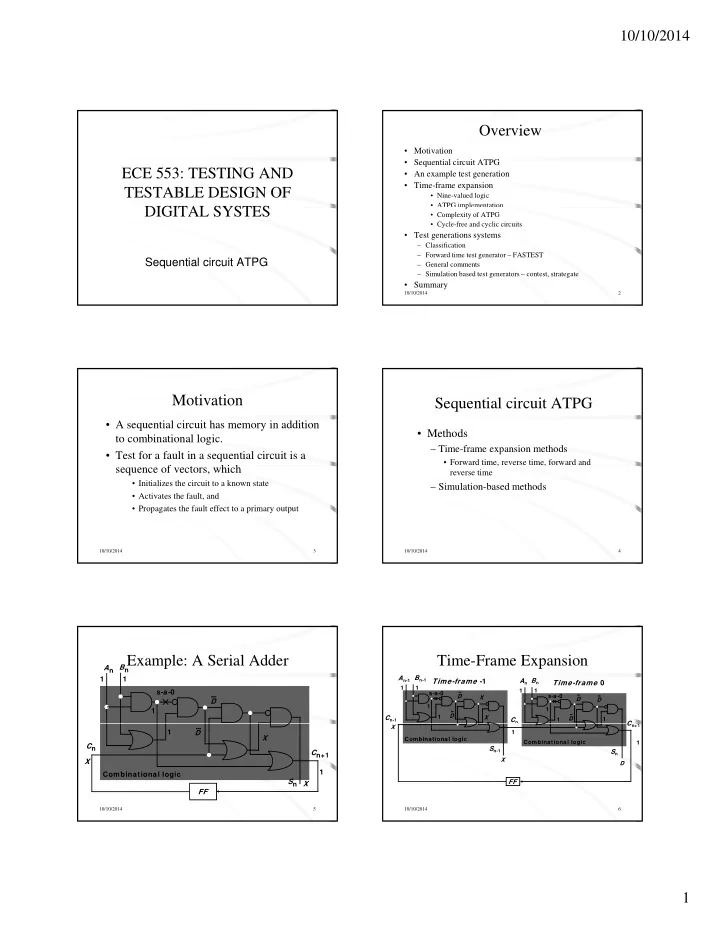

10/10/2014 Overview • Motivation • Sequential circuit ATPG ECE 553: TESTING AND • An example test generation • Time-frame expansion TESTABLE DESIGN OF • Nine-valued logic • ATPG implementation p DIGITAL SYSTES DIGITAL SYSTES • Complexity of ATPG • Cycle-free and cyclic circuits • Test generations systems – Classification – Forward time test generator – FASTEST Sequential circuit ATPG – General comments – Simulation based test generators – contest, strategate • Summary 10/10/2014 2 Motivation Sequential circuit ATPG • A sequential circuit has memory in addition • Methods to combinational logic. – Time-frame expansion methods • Test for a fault in a sequential circuit is a • Forward time, reverse time, forward and , , sequence of vectors, which f hi h reverse time • Initializes the circuit to a known state – Simulation-based methods • Activates the fault, and • Propagates the fault effect to a primary output 10/10/2014 3 10/10/2014 4 Example: A Serial Adder Time-Frame Expansion A n B n A n-1 B n-1 1 1 Time-frame -1 A n B n Time-frame 0 1 1 1 s-a-0 1 s-a-0 D s-a-0 X D D D 1 1 1 D C n-1 1 X D C n 1 1 C n+1 C X 1 D 1 X Combinational logic Combinational logic 1 C n S n-1 S n C n+1 X X D 1 Combinational logic S n FF X FF 10/10/2014 5 10/10/2014 6 1

10/10/2014 Example for Logic Systems Concept of Time-Frames • If the test sequence for a single stuck-at fault contains n vectors, • Replicate combinational logic block n times FF1 • Place fault in each block B • Generate a test for the multiple stuck-at fault using combinational ATPG with 9-valued logic bi i l ATPG i h 9 l d l i Vector - n +1 Vector -1 Vector 0 Fault Unknow n A FF2 Next State Time- Time- Time- or given s-a-1 state variables frame frame frame Init. state - n +1 -1 0 Comb. block PO - n +1 PO -1 PO 0 10/10/2014 7 10/10/2014 8 Five-Valued Logic (Roth) Nine-Valued Logic (Muth) 0,1, D , D , X 0,1, 1/0, 0/1, 1/ X, 0/ X , X/ 0, X/ 1, X A 0 A 0 A 0 A X s-a-1 s-a-1 s-a-1 s-a-1 X /1 D D 0/1 X X X X 0/ X 0/ X FF1 FF1 FF1 FF1 FF1 FF1 X D D X 0/1 X /1 FF2 FF2 FF2 FF2 B X B X B X B 0/1 Time-frame -1 Time-frame 0 Time-frame -1 Time-frame 0 10/10/2014 9 10/10/2014 10 An implementation of ATPG Complexity of ATPG • Select a PO for fault detection. Synchronous circuit -- All flip-flops controlled by clocks; • Place a logic value, 1/0 or 0/1, depending on fault PI and PO synchronized with clock: type and number of inversions. Cycle-free circuit – No feedback among flip-flops: Test • Justify the output value from PIs, considering all generation for a fault needs no more than dseq + 1 time- frames, where dseq is the sequential depth. necessary paths and adding backward time-frames. Cyclic circuit – Contains feedback among flip-flops: May Cyclic circuit Contains feedback among flip flops: May • If justification is impossible, then select another need 9 Nff time-frames, where Nff is the number of flip-flops. PO and repeat justification. Asynchronous circuit – Higher complexity! • If the procedure fails for all reachable POs, then the fault is untestable. Smax Time- Time- Time- S2 Time- Time- S3 S1 S0 • If 1/0 or 0/1 cannot be justified at any PO, but 1/X Frame Frame Frame Frame Frame max-1 max-2 -2 -1 0 or 0/X can be justified, the the fault is potentially max = Number of distinct vectors w ith 9-valued elements = 9 Nff detectable. 10/10/2014 11 10/10/2014 12 2

10/10/2014 Cycle-Free Circuits Cycle-Free Example Circuit • Characterized by absence of cycles among flip- F2 flops and a sequential depth, dseq . 2 • dseq is the maximum number of flip-flops on any q p p y F3 F3 F1 path between PI and PO. 3 Level = 1 F2 • Both good and faulty circuits are initializable. 2 • Test sequence length for a fault is bounded by dseq s - graph + 1. F1 F3 dseq = 3 Level = 1 3 All faults are testable. See Example 8.6. 10/10/2014 13 10/10/2014 14 Cyclic Circuit Example Modulo-3 Counter Modulo-3 counter • Cyclic structure – Sequential depth is undefined. Z CNT • Circuit is not initializable. No tests can be F2 F1 generated for any stuck-at fault. • After expanding the circuit to 9 Nff = 81, or fewer, 9 Nff Af di h i i 81 f time-frames ATPG program calls any given target fault untestable. s - graph • Circuit can only be functionally tested by multiple observations. F2 F1 • Functional tests, when simulated, give no fault coverage. 10/10/2014 15 10/10/2014 16 Adding Initializing Hardware Benchmark Circuits Initializable modulo-3 counter Circuit s1196 s1238 s1488 s1494 PI 14 14 8 8 Z PO 14 14 19 19 CNT F2 FF 18 18 6 6 F1 Gates 529 508 653 647 s-a-0 Structure Cycle-free Cycle-free Cyclic Cyclic Seq. depth Seq depth 4 4 4 4 -- -- Total faults 1242 1355 1486 1506 s-a-1 Detected faults 1239 1283 1384 1379 CLR Potentially detected faults 0 0 2 2 s-a-1 s-a-1 Untestable faults 30 3 72 26 Untestable fault Abandoned faults 0 0 76 97 Potentially detectable fault Fault coverage (%) 99.8 94.7 93.1 91.6 Fault efficiency (%) 100.0 100.0 94.8 93.4 s - graph Max. sequence length 3 3 24 28 F2 Total test vectors 313 308 525 559 F1 Gentest CPU s (normalized) 1.0 1.5 2000 1900 10/10/2014 17 10/10/2014 18 3

10/10/2014 Test Generations Systems Test Generations Systems • Classification • Reverse-time processing – Target a fault – Determine a PO where the fault-effect will appear • Reverse-time processing • Forward-time processing – Backtrace within the time frame to excite and or • Forward and reverse-time processing propagate a fault/fault-effect – Target no specific fault – If not possible go add a timeframe (previous • Simulation based algorithms timeframe) and continue 10/10/2014 19 10/10/2014 20 Test Generations Systems Test Generations Systems Reverse-time processing • Forward-time processing Positives and Negatives – Excite a fault in the present timeframe Low memory usages Hard to determine the PO where – If excited, propagate to an output, else add a fault will be detected Timeframe added when timeframe and then excite – continue till fault timeframe and then excite continue till fault needed During backward motion, often the excited timeframe is assumed to be fault- Ability to determine if a – Try to propagate the fault, if not successful, add free, this can generate invalid fault is untestable tests timeframe and continue the process till fault detected at a PO Test application is in the order opposite to test generation 10/10/2014 21 10/10/2014 22 Test generations systems Test generations systems Forward-time processing FASTEST approach • Forward and reverse-time processing – Use controllability values to determine the timeframe – Perform the fault effect propagation in forward where the fault can be excited time – Use observability values to determine the timeframe where the fault will be observed – Perform excitation (justification) in reverse time – Together these will determine the number of timeframes using fault-free circuit need to detect the fault of interest – Work with that many timeframes in combinational mode to generate a test sequence in forward time – See example circuit – (in class example) 10/10/2014 23 10/10/2014 24 4

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.