Noise Margin and Gate Delay Debdeep Mukhpadhyay IIT Madras Logic - PowerPoint PPT Presentation

Noise Margin and Gate Delay Debdeep Mukhpadhyay IIT Madras Logic levels Solid logic 0/1 defined by V SS /V DD . Inner bounds of logic values V L /V H are not directly determined by circuit properties, as in some other logic families. V

Noise Margin and Gate Delay Debdeep Mukhpadhyay IIT Madras

Logic levels • Solid logic 0/1 defined by V SS /V DD . • Inner bounds of logic values V L /V H are not directly determined by circuit properties, as in some other logic families. V DD logic 1 V H unknown V L logic 0 V SS

Logic level matching • Levels at output of one gate must be sufficient to drive next gate.

Transfer characteristics • Transfer curve shows static input/output relationship—hold input voltage, measure output voltage.

Noise Margins • How much noise can a gate input see before it does not recognize the input? Output Characteristics Input Characteristics V DD Logical High Logical High V OH Output Range Input Range NM H V IH Indeterminate Region V IL NM L Logical Low Logical Low V OL Input Range Output Range GND

Logic Levels • To maximize noise margins, select logic levels at V out V DD β p / β n > 1 V in V out V in 0 V DD

Logic Levels • To maximize noise margins, select logic levels at – unity gain point of DC transfer characteristic V out Unity Gain Points V DD Slope = -1 V OH β p / β n > 1 V in V out V OL V in 0 V DD - V tn V IL V IH V DD |V tp |

Noise margin • Noise margin = voltage difference between output of one gate and input of next. Noise must exceed noise margin to make second gate produce wrong output.

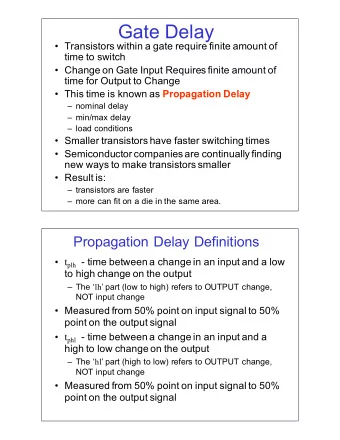

Delay Definitions • t pdr : • t pdf : • t pd : • t r : • t f : fall time

Delay Definitions • t pdr : rising propagation delay – From input to rising output crossing V DD /2 • t pdf : falling propagation delay – From input to falling output crossing V DD /2 • t pd : average propagation delay – t pd = (t pdr + t pdf )/2 • t r : rise time – From output crossing 0.2 V DD to 0.8 V DD • t f : fall time – From output crossing 0.8 V DD to 0.2 V DD

Delay Definitions • t cdr : rising contamination delay – From input to rising output crossing V DD /2 • t cdf : falling contamination delay – From input to falling output crossing V DD /2 • t cd : average contamination delay – t pd = (t cdr + t cdf )/2

Simulated Inverter Delay • Solving differential equations by hand is too hard • SPICE simulator solves the equations numerically – Uses more accurate I-V models too! • But simulations take time to write 2.0 1.5 1.0 (V) t pdf = 66ps t pdr = 83ps V in V out 0.5 0.0 0.0 200p 400p 600p 800p 1n t(s)

Delay Estimation • We would like to be able to easily estimate delay – Not as accurate as simulation – But can we give estimates? • The step response usually looks like a 1 st order RC response with a decaying exponential. • Use RC delay models to estimate delay – C = total capacitance on output node – Use effective resistance R – So that t pd = RC • Characterize transistors by finding their effective R – Depends on average current as gate switches

RC delay • Load is resistor + capacitor, driver is resistor. � tf = 0.69 R CL � For rise time replace by the PMOS resistance.

RC Delay Models • Use equivalent circuits for MOS transistors – Ideal switch + capacitance and ON resistance – Unit nMOS has resistance R, capacitance C – Unit pMOS has resistance 2R, capacitance C • Capacitance proportional to width • Resistance inversely proportional to width d s kC kC R/k 2R/k d d kC g k g g k g s kC kC s kC s d

Example: 3-input NAND • Sketch a 3-input NAND with transistor widths chosen to achieve effective rise and fall resistances equal to a unit inverter (R).

Example: 3-input NAND • Sketch a 3-input NAND with transistor widths chosen to achieve effective rise and fall resistances equal to a unit inverter (R). 2 2 2 3 3 3

3-input NAND Caps • Annotate the 3-input NAND gate with gate and diffusion capacitance. 2 2 2 3 3 3

3-input NAND Capacitors • Annotate the 3-input NAND gate with gate and diffusion capacitance. 2C 2C 2C 2C 2C 2C 2 2 2 2C 2C 2C 3C 3 3C 3C 3 3C 3C 3 3C 3C

3-input NAND Capacitors • Annotate the 3-input NAND gate with gate and diffusion capacitance. 2 2 2 9C 3 5C 3C 3 5C 3C 3 5C

Elmore Delay • ON transistors look like resistors • Pullup or pulldown network modeled as RC ladder • Elmore delay of RC ladder ∑ ≈ t R C − − pd i to source i nodes i ( ) ( ) = + + + + + + + R C R R C ... R R ... R C 1 1 1 2 2 1 2 N N R 1 R 2 R 3 R N C 1 C 2 C 3 C N

Example: 2-input NAND • Estimate worst-case rising and falling delay of 2-input NAND driving h identical gates. 2 2 Y A 2 h copies x 2 B

Example: 2-input NAND • Estimate rising and falling propagation delays of a 2-input NAND driving h identical gates. 2 2 Y 4hC 6C A 2 x 2C 2 h copies B

Example: 2-input NAND • Estimate rising and falling propagation delays of a 2-input NAND driving h identical gates. 2 2 Y 4hC 6C A 2 x 2C 2 B h copies = t pdr R Y (6+4h)C

Example: 2-input NAND • Estimate rising and falling propagation delays of a 2-input NAND driving h identical gates. 2 2 Y 4hC 6C A 2 x 2C 2 B h copies R Y ( ) = + (6+4h)C t 6 4 h RC pdr

Example: 2-input NAND • Estimate rising and falling propagation delays of a 2-input NAND driving h identical gates. 2 2 Y 4hC 6C A 2 x 2C h copies 2 B

Example: 2-input NAND • Estimate rising and falling propagation delays of a 2-input NAND driving h identical gates. 2 2 Y 4hC 6C A 2 x 2C 2 B h copies = t R/2 x pdf Y 2C (6+4h)C R/2

Example: 2-input NAND • Estimate rising and falling propagation delays of a 2-input NAND driving h identical gates. 2 2 Y 4hC 6C A 2 h copies x 2C 2 B ) ( ) ( ) ( ( ) = + + + ⎡ ⎤ R R R t 2 C ⎣ 6 4 h C ⎦ pdf 2 2 2 R/2 x Y ( ) = + 2C (6+4h)C R/2 7 4 h RC

Delay Components • Delay has two parts – Parasitic delay • 6 or 7 RC • Independent of load – Effort delay • 4h RC • Proportional to load capacitance

CMOS inverter delay • An approximate method: – Assume constant I avg – The NMOS and the PMOS I 1 are in saturated region and V 1 =Vcc provide a constant current. V 2 =½Vcc C V = load CC t ( ) PHL − 2 k V V n CC Tn C V = t 1 t 2 load CC t ( ) PLH − 2 k V V p CC TP I avg = I 1

Some Points • The delay of a gate, be it the rise or the fall time is inversely proportional to VDD. • Point to ponder: Effect of sizing on the inverter gate delay.

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.