Nanostructures for Tera Tera- -bit Level bit Level Nanostructures - PowerPoint PPT Presentation

Nanostructures for Tera Tera- -bit Level bit Level Nanostructures for Charge Trap Flash Memories Charge Trap Flash Memories Byung-Gook Park, Il Han Park, Jung-Hoon Lee, Gil Sung Lee, Jang-Gn Yun Inter-University Semiconductor Research

Nanostructures for Tera Tera- -bit Level bit Level Nanostructures for Charge Trap Flash Memories Charge Trap Flash Memories Byung-Gook Park, Il Han Park, Jung-Hoon Lee, Gil Sung Lee, Jang-Gn Yun Inter-University Semiconductor Research Center School of Electrical Eng. and Computer Sci. Seoul National University N a n o F o r u m' 0 9

Outline I. I. Introduction Introduction II. NAND Cell Structure III. NOR Cell and Array Structure IV. AND Cell and Array Structure V. STAR NAND Flash Structure VI. Conclusions NanoForum'09 SNU SoEECS SNU SoEECS & ISRC & ISRC

Flash Memory and Mobile Equipments 32 NanoForum'09 SNU SoEECS SNU SoEECS & ISRC & ISRC

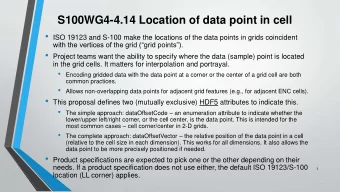

Expedited Growth Theory - Expedited Growth Theory - NAND Flash NAND Flash 100 1000 ITRS (2008) Hwang’s law Capacity (Giga Bit) Technology Node (nm) 100 10 10 2002 2004 2006 2008 2010 2012 2014 2016 2018 Year of Development � Expedited growth theory of NAND flash memories � Year 2011 1Tb capacity with 20nm feature size NanoForum'09 SNU SoEECS SNU SoEECS & ISRC & ISRC

Hard Disk Drive and Flash Memory Hard Disk Drive and Flash Memory NanoForum'09 SNU SoEECS SNU SoEECS & ISRC & ISRC

Growth of Storage Capacity Growth of Storage Capacity HDD ODD 10T FGF 1T CTF FeRAM 100G MRAM Capacity (bit) 10G PRAM 1G 100M 10M 1M 100k 10k 1k 1988 1990 1992 1994 1996 1998 2000 2002 2004 2006 2008 2010 Year NanoForum'09 SNU SoEECS SNU SoEECS & ISRC & ISRC

Floating Gate vs. Charge Traps Floating Gate vs. Charge Traps Floating Gate Floating Gate SONOS SONOS ONO ONO � No floating gate structure structure structure structure Composite Composite Dielectrics Dielectrics - FG-FG space Gate Gate - FG-active space Gate Gate - Single gate structure n+ n+ n+ n+ n+ n+ n+ n+ P P - - Si Si P P - - Si Si � Defect immunity - Non-conductive trap layer Tunnel Tunnel Blocking Blocking Poly Si Poly Si - Discrete trap storage Si SiO2 Si SiO2 Si3N4 Si3N4 SiO2 SiO2 1.05 1.05 3.1 3.1 3.1 3.1 � 3D structure compatibility e e e e e e 8.0 8.0 h h h h h h - Insulating storage node - Simple fabrication 3.8 3.8 3.8 3.8 1.85 1.85 NanoForum'09 SNU SoEECS SNU SoEECS & ISRC & ISRC

Outline I. Introduction II. NAND Cell Structure II. NAND Cell Structure III. NOR Cell and Array Structure IV. AND Cell and Array Structure V. STAR NAND Flash Structure VI. Conclusions NanoForum'09 SNU SoEECS SNU SoEECS & ISRC & ISRC

Arch Structure (1) Arch Structure (1) � Utilization of curved surfaces for field enhancement - fast “program” and “erase” - increased effective area r r 2 2 r r 1 1 Poly Arch type ONO Planar type 12.0M Electric Field (V/cm) 10.0M SiO 2 8.0M 6.0M 4.0M Bottom 2.0M Top Oxide Silicon Nitride Oxide Si 0.0 0 2 4 6 8 10 12 14 Position (nm) NanoForum'09 SNU SoEECS SNU SoEECS & ISRC & ISRC

Arch Structure (2) Arch Structure (2) � Fabrication procedure Hard mask Si SiO Si 2 Si NanoForum'09 SNU SoEECS SNU SoEECS & ISRC & ISRC

Arch Structure (3) Arch Structure (3) � Utilization of HSQ mask characteristic � Planarization by TEOS, HSQ and etch back NanoForum'09 SNU SoEECS SNU SoEECS & ISRC & ISRC

Arch Structure (4) Arch Structure (4) <Programming characteristics> <Erase characteristics> 0.5 5.5 0.0 5.0 -0.5 4.5 -1.0 4.0 -1.5 3.5 -2.0 3.0 -2.5 ∆ V th (V) ∆ V th (V) -18V 2.5 -3.0 -20V 2.0 -3.5 20V -22V 1.5 -4.0 22V -4.5 -24V 1.0 24V -5.0 0.5 -5.5 0.0 -6.0 -0.5 -7 10 -6 10 -5 10 -4 10 -3 10 -2 10 -1 10 0 10 -7 10 -6 10 -5 10 -4 10 -3 10 -2 10 -1 10 0 10 1 Initial 1 10 Initial 10 Time(s) Time(s) � Radius of Si channel = 15 nm NanoForum'09 SNU SoEECS SNU SoEECS & ISRC & ISRC

Outline I. Introduction II. NAND Cell Structure III. NOR Cell and Array Structure NOR Cell and Array Structure III. IV. AND Cell and Array Structure V. STAR NAND Flash Structure VI. Conclusions NanoForum'09 SNU SoEECS SNU SoEECS & ISRC & ISRC

Cone Structure (1) Cone Structure (1) � Utilization of field and current concentration - field concentration in the horizontal direction - current concentration in the vertical direction Cut line Drain junction Drain junction Cut line ONO layer Gate Gate ONO layer Electric field high flux density high flux density r 2 Si flux r 1 O O Drain E R N E r Gate Source low flux density low flux density NanoForum'09 SNU SoEECS SNU SoEECS & ISRC & ISRC

Cone Structure (2) Cone Structure (2) � Simple array structure - common source architecture - word line connection through small spacing of cones NanoForum'09 SNU SoEECS SNU SoEECS & ISRC & ISRC

Cone Structure (3) Cone Structure (3) <Plan view> <Cross-sectional view> NanoForum'09 SNU SoEECS SNU SoEECS & ISRC & ISRC

Cone Structure (4) Cone Structure (4) � Electrical characteristics <Program/erase characteristics> <Retention characteristic> 4.0 4.0 o C) Retention Characteristics(150 CHEI Program( V G : 6 V, V D :4 V) program state 3.5 3.5 3.0 3.0 2.5 CHEI Program( V G : 6 V, V D :3 V) 2.5 V TH (V) V TH ( V) 2.363 V 2.0 2.160 V 2.0 1.5 1.5 1.0 1.0 0.5 FN Erase ( V B : 11 V) Erase state 0.5 0.0 0 1 2 3 4 5 6 7 8 1E-8 1E-7 1E-6 1E-5 1E-4 1E-3 0.01 0.1 1 10 10 10 10 10 10 10 10 10 10 Time (s) Time (s) NanoForum'09 SNU SoEECS SNU SoEECS & ISRC & ISRC

Outline I. Introduction II. NAND Cell and Array Structure III. NOR Cell and Array Structure IV. AND Cell and Array Structure AND Cell and Array Structure IV. V. STAR NAND Flash Structure VI. Conclusions NanoForum'09 SNU SoEECS SNU SoEECS & ISRC & ISRC

Conventional Flash Memory Structures Conventional Flash Memory Structures < NAND > < NOR > < AND > Active LSL LBL W/L F-Poly Schematic Top View NAND NOR AND program efficiency high Low high sensing speed low high high density high low low NanoForum'09 SNU SoEECS SNU SoEECS & ISRC & ISRC

Vertical AND Structure (1) Vertical AND Structure (1) � Memory cell device with vertical and double gate structures - vertical structure, S/D junctions connected by diffusion layer � High integration density. - double gate structure. � High device performance, high sensing speed. N N N N N N N N N P P P P P P P P P N N N N N N N N N P P P NanoForum'09 SNU SoEECS SNU SoEECS & ISRC & ISRC

Vertical AND Structure (2) Vertical AND Structure (2) � Fabrication procedure N N N N N N P P P P N N N N P P N N P P N N N N N N N N N N N N P P P P P P P P P P N N N N N N N N N N P P P P (a) (b) (c) (d) N N N N N N P P P P N N N N P P P P N N N N N N N N N N N N N N N N P P P P P P P P P P P P N N N N N N N N N N N N P P P P (h) (g) (f) (e) NanoForum'09 SNU SoEECS SNU SoEECS & ISRC & ISRC

Vertical AND Structure (3) Vertical AND Structure (3) � Program/erase characteristics <Program characteristics> <Erase characteristics> 7 7 V G = 13 V 6 Threshold Voltage [V] Threshold Voltage [V] 6 V G = 15 V V G = 17 V 5 5 4 4 V G = 13 V V G = 15 V 3 V G = 17 V 3 2 2 -5 -4 -3 -2 -1 0 -7 -6 -5 -4 -3 -2 -1 10 10 10 10 10 10 10 10 10 10 10 10 10 Erasing Time (sec) Programming Time (sec) NanoForum'09 SNU SoEECS SNU SoEECS & ISRC & ISRC

Outline I. Introduction II. NAND Cell Structure III. NOR Cell and Array Structure IV. AND Cell and Array Structure V. STAR NAND Flash Structure STAR NAND Flash Structure V. VI. Conclusions NanoForum'09 SNU SoEECS SNU SoEECS & ISRC & ISRC

STAR NAND Flash Structure (1) WL direction � Stacked bit-lines gate � high density oxide � Cylindrical channel and gate gate-all-around cell ONO dielectrics Si structure cylindrical channel � high performance Si body � Single-crystal Si channel oxide � high performance, uniformity, reliability Si substrate NanoForum'09 SNU SoEECS SNU SoEECS & ISRC & ISRC 24

STAR NAND Flash Structure (2) � Fabrication procedure mask a > b nitride nitride nitride SiGe SiGe SiGe Si Si Si SiGe SiGe SiGe Si Si Si SiGe SiGe SiGe Si substrate Si substrate Si substrate SiGe SiGe nitride nitride nitride a > b SiGe Si Si Si SiGe Si Si Si SiGe Si substrate Si substrate Si substrate NanoForum'09 SNU SoEECS SNU SoEECS & ISRC & ISRC

STAR NAND Flash Structure (3) � Fabrication procedure (continued) WL direction gate gate SiGe ONO nitride oxide gate ONO dielectrics Si Si Si Si cylindrical channel Si Si body Si ONO oxide Si substrate Si substrate Si substrate NanoForum'09 SNU SoEECS SNU SoEECS & ISRC & ISRC

STAR NAND Flash Structure (4) � Components of stack and nanowire implementation <Selectively etched SiGe> <Rounded Si nanowire> NanoForum'09 SNU SoEECS SNU SoEECS & ISRC & ISRC 27

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.