MULTI-OPERAND ADDITION Bit-arrays for unsigned and signed operands - PowerPoint PPT Presentation

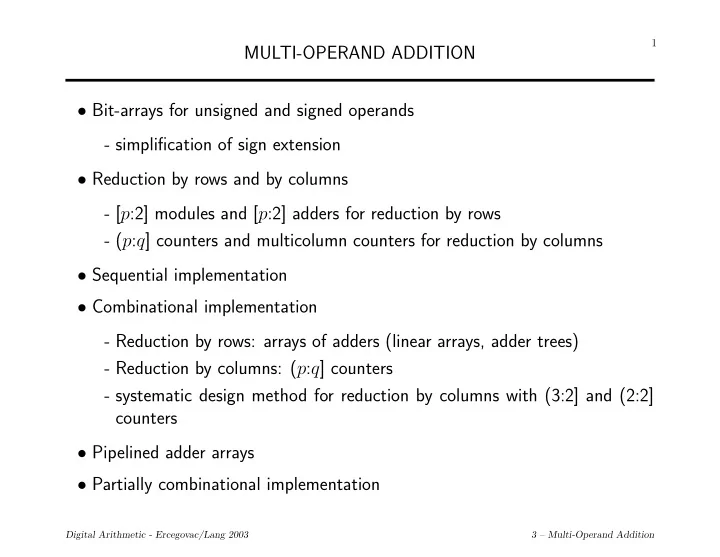

1 MULTI-OPERAND ADDITION Bit-arrays for unsigned and signed operands - simplification of sign extension Reduction by rows and by columns - [ p :2] modules and [ p :2] adders for reduction by rows - ( p : q ] counters and multicolumn

1 MULTI-OPERAND ADDITION • Bit-arrays for unsigned and signed operands - simplification of sign extension • Reduction by rows and by columns - [ p :2] modules and [ p :2] adders for reduction by rows - ( p : q ] counters and multicolumn counters for reduction by columns • Sequential implementation • Combinational implementation - Reduction by rows: arrays of adders (linear arrays, adder trees) - Reduction by columns: ( p : q ] counters - systematic design method for reduction by columns with (3:2] and (2:2] counters • Pipelined adder arrays • Partially combinational implementation Digital Arithmetic - Ercegovac/Lang 2003 3 – Multi-Operand Addition

2 BIT ARRAYS FOR UNSIGNED AND SIGNED OPERANDS a 0 a 0 a 0 a 0 a 1 a 2 a n . . . . b 0 b 0 b 0 b 0 b 1 b 2 b n . . . . c 0 c 0 c 0 c 0 c 1 c 2 c n . . . . d 1 d 2 d n d 0 d 0 d 0 d 0 . . . . e 0 e 0 e 0 e 0 e 1 e 2 e n . . . . sign extension Figure 3.1: SIGN-EXTENDED ARRAY FOR m = 5 . Digital Arithmetic - Ercegovac/Lang 2003 3 – Multi-Operand Addition

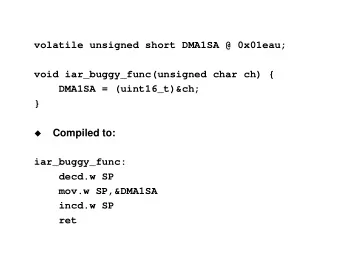

3 s’ a’ 0 . a 1 a 2 ... a n . x x x x . . . x -1 -1 b’ 0 . b 1 b 2 ... b n s’ . x x x x . . . x -1 -1 c’ 0 . c 1 c 2 ... c n -1 d’ 0 . d 1 d 2 ... d n s’ . x x x x . . . x -1 e’ 0 . e 1 e 2 ... e n -1 -1 s’ . x x x x . . . x -1 Reduced to Reduced to a’ 0 . a 1 a 2 ... a n s’ . x x x x . . . x b’ 0 . b 1 b 2 ... b n s’ . x x x x . . . x c’ 0 . c 1 c 2 ... c n s’ . x x x x . . . x d’ 0 . d 1 d 2 ... d n s’ . x x x x . . . x e’ 0 . e 1 e 2 ... e n y y y y . . . y 1 0 1 1 Transformed to (a) a’ 0 . a 1 a 2 ... a n b’ 0 . b 1 b 2 ... b n c’ 0 . c 1 c 2 ... c n (b) d’ 0 . d 1 d 2 ... d n 1e’ 0 e 0 e 0 . e 1 e 2 ... e n Figure 3.2: SIMPLIFYING SIGN-EXTENSION: (a) GENERAL CASE. (b) EXAMPLE OF SIMPLIFYING ARRAY WITH m = 5 . Digital Arithmetic - Ercegovac/Lang 2003 3 – Multi-Operand Addition

4 REDUCTION • By rows • By columns Digital Arithmetic - Ercegovac/Lang 2003 3 – Multi-Operand Addition

5 [ p :2] ADDERS FOR REDUCTION BY ROWS k [p:2] adder [p:2] module ... ... ... ... ... p . . . ... . . . ... ... ... ... ... ... ... ... ... ... ... ... ... ... 2 input carries output carries (a) [p:2] module k p p k k p p p p h out h in H Z 2 2 k z (b) Figure 3.3: A [ p :2] adder: (a) Input-output bit-matrix. (b) k -column [ p :2] module decomposition. Digital Arithmetic - Ercegovac/Lang 2003 3 – Multi-Operand Addition

6 MODEL OF [p:2] MODULE k - 1) k max value p(2 p p HW w max value W h in h out max value H log 2 W k H max value 2 Z 2 2 k z k - 1) max value 2(2 Figure 3.4: A model of a [ p :2] module. Digital Arithmetic - Ercegovac/Lang 2003 3 – Multi-Operand Addition

7 inputs of weight 2 i inputs of weight 2 i-1 x i,3 x i,2 x i,1 x i,0 x i-1,3 x i-1,1 x i-1,0 x i-1,2 x i,3 x i,1 x i-1,3 x i-1,1 0 1 0 1 MUX MUX h i+1, 1 x i-1,0 a x i,0 h i-1, 1 0 1 0 1 MUX MUX to next column previous column carries from carries c Z h i+1, 2 h i-1, 2 x i-1,0 denotes the bits representing w h i-1, 1 such that w = 2c + 2b + a a Note that w < 4 since ab = 0 b MUX Figure 3.5: Gate network implementation of [4:2] module. Digital Arithmetic - Ercegovac/Lang 2003 3 – Multi-Operand Addition

8 inputs of weight 2 i inputs of weight 2 i-1 FA FA c s c s FA FA c s c s to next column previous column carries from carries FA FA c s c s denotes the bits representing w (a) inputs of weight 2 i inputs of weight 2 i-1 inputs of weight 2 i-2 FA FA FA FA FA FA c s c s c s c s c s c s FA FA FA c s c s c s previous column to next column carries from FA FA FA carries c s c s c s FA FA FA c s c s c s (b) denotes the bits representing w Figure 3.6: (a) [5:2] module. (b) [7:2] module. Digital Arithmetic - Ercegovac/Lang 2003 3 – Multi-Operand Addition

9 ( p : q ] COUNTERS FOR REDUCTION BY COLUMNS p − 1 q − 1 j =0 y j 2 j i =0 x i = � � 2 q − 1 ≥ p, i . e ., q = ⌈ log 2 ( p + 1) ⌉ x 0 x 1 . p inputs (same weight) . . . . . + x p-1 . . . y q-1 ... y 0 q outputs (a) (b) Figure 3.7: (a) ( p : q ] reduction. (b) Counter representation. Digital Arithmetic - Ercegovac/Lang 2003 3 – Multi-Operand Addition

10 IMPLEMENTATION OF ( p : q ] COUNTERS all inputs of weight (1) FA FA c s c s (1) (1) (1) FA c s (2) (2) (2) FA (4) (2) (1) Figure 3.8: Implementation of (7:3] counter by an array of full adders. Digital Arithmetic - Ercegovac/Lang 2003 3 – Multi-Operand Addition

11 x 5 x 3 x 5 x 3 x 5 x 3 x 5 x 3 x 1 x 0 x 0 x 2 x 1 x 0 x 4 x 6 x 4 x 6 x 4 x 2 x 2 x 1 x 6 x 4 x 6 a (q B2 )’ q A1 q B0 q A0 (q B1 )’ q 2 q 0 q 1 Figure 3.9: Gate network of a (7:3] counter. Digital Arithmetic - Ercegovac/Lang 2003 3 – Multi-Operand Addition

12 MULTICOLUMN COUNTER ( p k − 1 , p k − 2 , . . . , p 0 : q ] p i k − 1 j =1 a ij 2 i ≤ 2 q − 1 v = � � i =0 (a) (b) Figure 3.10: (a) (5,5:4] counter. (b) (1,2,3:4] counter. Digital Arithmetic - Ercegovac/Lang 2003 3 – Multi-Operand Addition

13 cycle time dependent on precision X[i] Carry Propagate Adder S[i] clk Register S S[i-1] (a) cycle time not dependent on precision X[(i-1)(p-2)+1] X[i] X[i(p-2)] [p:2] Adder [3:2] Adder C[i] PS[i] C[i] PS[i] clk clk Reg. C Reg. PS Reg. C Reg. PS PS[i-1] C[i-1] PS[i-1] C[i-1] To CPA to get S To CPA to get S (c) (b) Figure 3.11: SEQUENTIAL MULTIOPERAND ADDITION: a) WITH CONVENTIONAL ADDER. b) WITH [p:2] ADDER. c) WITH [3:2] ADDER. Digital Arithmetic - Ercegovac/Lang 2003 3 – Multi-Operand Addition

14 COMBINATIONAL IMPLEMENTATION • Reduction by rows: array of adders – Linear array – Adder tree • Reduction by columns with (p:q] counters Digital Arithmetic - Ercegovac/Lang 2003 3 – Multi-Operand Addition

15 p operands [p:2] ADDER p-2 operands [p:2] ADDER p-2 operands [p:2] ADDER p-2 operands [p:2] ADDER to CPA Figure 3.12: LINEAR ARRAY OF [p:2] ADDERS FOR MULTIOPERAND ADDITION. Digital Arithmetic - Ercegovac/Lang 2003 3 – Multi-Operand Addition

16 ADDER TREE • k - the number of [p:2] CS adders for m operands: pk = m + 2( k − 1) m − 2 k = [p:2] carry-save adders p − 2 • The number of adder levels m l [p:2] tree of l levels [p:2] [p:2] m l-1 [p:2] tree of l-1 levels 2 Figure 3.13: Construction of a [p:2] carry-save adder tree. m l − 1 + m l − 1 mod 2 m l = p 2 Digital Arithmetic - Ercegovac/Lang 2003 3 – Multi-Operand Addition

17 NUMBER OF LEVELS (cont.) Table 3.1: [3:2] Reduction sequence. l 1 2 3 4 5 6 7 8 9 m l 3 4 6 9 13 19 28 42 63 m l ≈ p l 2 l − 1 l ≈ log p/ 2 ( m l / 2) Digital Arithmetic - Ercegovac/Lang 2003 3 – Multi-Operand Addition

18 m = 9 a a a a a a a a a a x x x x x x x x x CSA CSA CSA a x x x x x x x x x Level 4 CSAs b a b a b a a x x x x x x x x x a x x x x x x x x x b x x x x x x x x x b x x x a x x x CSA CSA a x x x b x x x d c b c Level 3CSAs b x x x a x x x Bit-vector types c x x x x c x x x x L= 4 a: (n-1,..., 0) d x x x b x x x b: (n ,..., 1) b x x x CSA c: (n ,..., 0) c x x x x Level 2 CSA d e d: (n+1,...,2) d x x x x e: (n+1 ,..., 0) e x x x x x c x x x x f: (n+2 ,..., 1) d x x x e x x x x x d x x x Level 1 CSA CSA e x x x x x f e f x x x x x Figure 3.14: [3:2] adder tree for 9 operands (magnitudes with n = 3 ) . Digital Arithmetic - Ercegovac/Lang 2003 3 – Multi-Operand Addition

19 [4:2] ADDER [4:2] ADDER [4:2] ADDER [4:2] ADDER [4:2] ADDER [4:2] ADDER [4:2] ADDER Figure 3.15: Tree of [4:2] adders for m = 16 . Digital Arithmetic - Ercegovac/Lang 2003 3 – Multi-Operand Addition

20 REDUCTION BY COLUMNS WITH (p:q] COUNTERS 1 0 1 1 0 0 1 0 1 0 0 1 0 1 1 0 1 0 1 0 1 1 1 1 0 1 1 0 0 1 0 1 0 1 1 1 1 0 1 0 Figure 3.16: Example of reduction using (7:3] counters. Digital Arithmetic - Ercegovac/Lang 2003 3 – Multi-Operand Addition

21 NUMBER OF COUNTER LEVELS m 1 = p � m l − 1 � m l = p + m l − 1 mod q q l ≈ log p/q ( m l /q ) m l (p:q] tree of p p l levels (p:q] (p:q] q q mod q ml-1 m l-1 (p:q] tree of l-1 levels q Figure 3.17: Construction of (p:q] reduction tree. Digital Arithmetic - Ercegovac/Lang 2003 3 – Multi-Operand Addition

22 Table 3.2: Sequence for (7:3] counters Number of levels 1 2 3 4 ... Max. number of rows 7 15 35 79 ... Digital Arithmetic - Ercegovac/Lang 2003 3 – Multi-Operand Addition

23 15 7 3 Figure 3.18: Multilevel reduction with (7:3] counters Digital Arithmetic - Ercegovac/Lang 2003 3 – Multi-Operand Addition

24 SYSTEMATIC DESIGN METHOD Full adder Half adder (3-2) (2-2) 2 i+1 2 i 2 i+1 2 i denotes 0 or 1 diagonal outputs when representing separately sum and carry bit-vectors or or is preferrable horizontal outputs when interleaving sum and carry bits is acceptable Figure 3.19: Full adder and half adder as (3:2] and (2:2] counters. Digital Arithmetic - Ercegovac/Lang 2003 3 – Multi-Operand Addition

25 column: 1 0 # of rows 6 reduce transfer 4 Figure 3.20: Reduction process. Digital Arithmetic - Ercegovac/Lang 2003 3 – Multi-Operand Addition

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.