Model-based engineering of high-performance embedded applications on - PowerPoint PPT Presentation

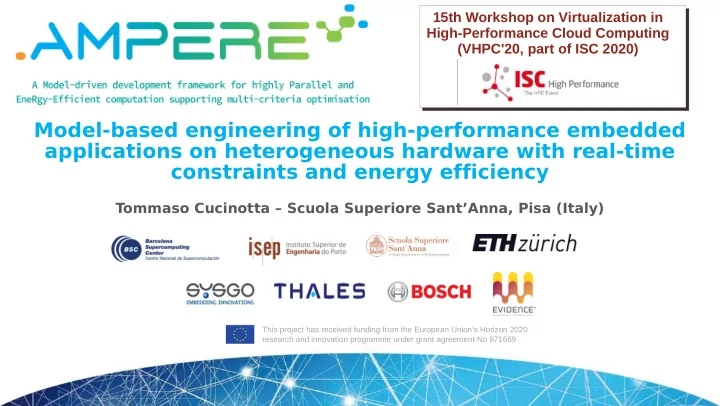

15th Workshop on Virtualization in 15th Workshop on Virtualization in High-Performance Cloud Computing High-Performance Cloud Computing (VHPC'20, part of ISC 2020) (VHPC'20, part of ISC 2020) Model-based engineering of high-performance

15th Workshop on Virtualization in 15th Workshop on Virtualization in High-Performance Cloud Computing High-Performance Cloud Computing (VHPC'20, part of ISC 2020) (VHPC'20, part of ISC 2020) Model-based engineering of high-performance embedded applications on heterogeneous hardware with real-time constraints and energy efficiency Tommaso Cucinotta – Scuola Superiore Sant’Anna, Pisa (Italy) This project has received funding from the European Union’s Horizon 2020 research and innovation programme under grant agreement No 871669

Introduction & Motivations ● CPSs have high gher and high gher comput utatjo tjonal performance & reli liability requi uirements ● Use of incr creasingl gly heterogeneous us & interconnect cted, batu tuery-operated pla latg tgorms – non-SMP multj-core – GP-GPU/TPU acceleratjon – FPGA ● Heterogeneous pla latg tgorms needed in sofu fu and hard real-tjm tjme use-ca cases Non-SMP multi-core GP-GPU TPU FPGA – automotjve, railways, aerospace, Heterogeneous Hardware Heterogeneous Hardware robotjcs, gaming, multjmedia, ... Tommaso Cucinotta – Real-Time Systems Laboratory - Scuola Superiore Sant’Anna - VHPC 2020 2

Problems & Challenges ● Develo elopme ment of so sofu fuware e App 1 App n App 1 App n for CP CPSs s is is cumbe mberso some me! Operating System Services & Middleware Operating System Services & Middleware – Optjmum usage of underlying hardware Power Power CPU Scheduler I/O Scheduler Management Drivers... CPU Scheduler I/O Scheduler Management Drivers... parallelism & acceleratjon Operating System Kernel / Hypervisor Operating System Kernel / Hypervisor – Performance vs energy consumptjon trade-ofgs – Real-tjme constraints Non-SMP multi-core GP-GPU TPU FPGA – Safety & certjfjcatjon Heterogeneous Hardware Heterogeneous Hardware Tommaso Cucinotta – Real-Time Systems Laboratory - Scuola Superiore Sant’Anna - VHPC 2020 3

MDE & Formalisms in Embedded System Design ● Model-D -Driv iven n Engi ngine neering ring (MD MDE) Functional & Non-functional Requirements Functional & Non-functional Requirements gap – Fill the gap between System Specification System Specification high-level specifjcatjons and actual system gap behavior Architecture Definition Architecture Definition ● MD gap MDE E emb mbraces Implemented Software Implemented Software – Formal specifjcatjon language(s) – Model transformatjon engine(s) Logic – Model refjnements & composability MD E Sensors Actuators Controller (e.g. CAPELLA, – Automatjc code generator(s) AMALTHEA, AUTOSAR) – Model verifjability ● => Corr rrect ctne ness-b s-by-c -const nstructj ructjon Tommaso Cucinotta – Real-Time Systems Laboratory - Scuola Superiore Sant’Anna - VHPC 2020 4

MDE & Formalisms in Embedded System Design ● Model-D -Driv iven n Engi ngine neering ring (MD MDE) Functional & Non-functional Requirements Functional & Non-functional Requirements gap – Fill the gap between System Specification System Specification high-level specifjcatjons and actual system Trad aditj itjonal M al MDE l limit mitatjo tjons gap Trad aditjo itjonal M al MDE l limit mitatjo tjons behavior Architecture Definition Architecture Definition ● Single-processor systems or very limited ● Single-processor systems or very limited ● MD gap MDE E emb mbraces Implemented Software support for multj-core systems Implemented Software support for multj-core systems – Formal specifjcatjon language(s) ● Struggles at coping with nowadays ● Struggles at coping with nowadays – Model transformatjon engine(s) Logic complex heterogeneous embedded boards – Model refjnements & composability complex heterogeneous embedded boards MD E Sensors Actuators Controller (e.g. CAPELLA, – Automatjc code generator(s) AMALTHEA, AUTOSAR) – Model verifjability ● => Corr rrect ctne ness-b s-by-c -const nstructj ructjon Tommaso Cucinotta – Real-Time Systems Laboratory - Scuola Superiore Sant’Anna - VHPC 2020 5

AMPERE Project Goal Logic MD E Sensors Actuators Controller ● Fill ll the gap p bet etween en (e.g. CAPELLA, AMALTHEA, AUTOSAR) – MDE techniques with no/limited parallelism support Parallel Parallel Units – Parallel-programming models with effjcient Programming Models Parallel Units HW offmoading (e.g. OpenMP, P a ra lle l OpenCL, Parallel Untits (OpenMP, CUDA, ...) E x e c u tion CUDA, COMPSs) Mo d e l – Heterogeneity in hardware Run-time parallel frameworks ● In pr pres esen ence e of non-functj tjonal l req equirements – High-Performance – Real-Time Constraints – Energy Effjciency Non-SMP multi-core GP-GPU TPU FPGA – Fault Tolerance Heterogeneous Hardware Heterogeneous Hardware Tommaso Cucinotta – Real-Time Systems Laboratory - Scuola Superiore Sant’Anna - VHPC 2020 6

AMPERE Vision Logic MD E Sensors Actuators Controller (e.g. CAPELLA, 1. Synthesis methods for an effjcient generatjon of AMALTHEA, AUTOSAR) parallel source code, while keeping non- functjonal and composability guarantees Bridge 2. Run-tjme parallel frameworks that guarantee the gap system correctness and exploit the performance capabilitjes of parallel architectures Parallel Parallel Units 3. Integratjon of parallel frameworks into MDE Programming Models Parallel Units (e.g. OpenMP, P a r a lle l frameworks OpenCL, Parallel Untits E x e c u tion CUDA, COMPSs) Mo d e l Run-time parallel frameworks Tommaso Cucinotta – Real-Time Systems Laboratory - Scuola Superiore Sant’Anna - VHPC 2020 7

AMPERE Vision CAPELLA CAPELLA AMALTHEA Functional components AUTOSAR AMALTHEA Functional components AUTOSAR Performance Allocation of resources SW-C Allocation of resources Performance SW-C Tasks Data models Runnables Data models Runnables Tasks Scheduling View points Client-server View points Logic Client-server Scheduling MD E Platform validation rules Sensors ASIL validation rules Actuators ASIL Platform Controller (e.g. CAPELLA, AMALTHEA, AUTOSAR) Meta-model Driven Abstractions Meta-model Driven Abstractions Components, Communications, Timing Characteristics, IntegrityAassurance, ... Components, Communications, Timing Characteristics, IntegrityAassurance, ... Model Transformation Engine Model Transformation Engine Bridge the gap Meta-parallel Programming Abstraction Meta-parallel Programming Abstraction Parallelism, Synchronization, Data Dependencies, Data Attributes, ... Parallelism, Synchronization, Data Dependencies, Data Attributes, ... Parallel Parallel Units Programming OpenMP OpenCL COMPSs Models OpenMP OpenCL COMPSs Parallel Units Task construct clgetDeviceId Compute resource Task construct clgetDeviceId Compute resource (e.g. OpenMP, P a r a lle l Dependencies clCreateBuffer Data movements Dependencies clCreateBuffer Data movements OpenCL, Parallel Untits Parallel construct __kernel_exec Task annotations E x e c u tion CUDA, COMPSs) Parallel construct __kernel_exec Task annotations Mo d e l Run-time parallel Parallel Run-Time Frameworks Parallel Run-Time Frameworks frameworks AMPERE MDE Framework Tommaso Cucinotta – Real-Time Systems Laboratory - Scuola Superiore Sant’Anna - VHPC 2020 8

AMPERE Software Architecture Sofuware Layer Tool Owner (License) AUTOSAR AUTOSAR (Proprietary) DSMLs AMALTHEA BOSCH (Open-source) CAPELLA TRT (Open-source) OpenMP OpenMP ARB (Proprietary) CUDA NVIDIA (Proprietary) Parallel programming models OpenCL Khronos (Proprietary) COMPSs BSC (Open-source) Artjfjcial Intelligence TensorFlow Google (Open-source) Code synthesis tools Synthesis tools AMPERE (Open-source) Analysis and testjng tools NFP analysis AMPERE (Open-source) Mercurium BSC (Open-source) Compilers and hardware GCC/LLVM GNU/LLVM (Open-source) synthesis tools Vivado Xilinx (Proprietary) GOMP GNU-GCC (Open-source) Run-tjme libraries KMP LLVM (Open-source) Vivado Xilinx (Proprietary) Linux Linux-Foundatjon (Open-source) Operatjng systems ERIKA Enterp. EVI (Open-source/commercial) Hypervisors PikeOS SYSGO (Proprietary) Tommaso Cucinotta – Real-Time Systems Laboratory - Scuola Superiore Sant’Anna - VHPC 2020 9

AMPERE Software Development Workflow Overview S y s te md e s c rip tion • Components/communication • Functional/NFP • Etc. Parallel code(e.g. OpenMP , C UD A graphs) Meta PPM R e s ou rc eA lloc a tion P la tfo rm Me ta MD E abstraction abs traction d e s c rip tio n (i.e., mapping/scheduling) Model • Accel. devices • Cores/clusters • Monitoring C od eS y n th e s is+ C om p ile r • Memory model • Dynamic Mu lti-c rite ria • Etc. (Correctness + resource O p tim iz a tion Refined Parallel allocation • Performance Structure) • Time-predictability • Energy-efficiency R u n -tim e fr a m e w ork + • Resiliency O S + H y p e rv is or Ex ecutionProfile Tommaso Cucinotta – Real-Time Systems Laboratory - Scuola Superiore Sant’Anna - VHPC 2020 10

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.