Memory Management Chester Rebeiro IIT Madras Memory map of process - PowerPoint PPT Presentation

Memory Management Chester Rebeiro IIT Madras Memory map of process 1 Process 1 Memory map of process 2 Process 2 Sharing RAM Memory map of process 3 Process 3 Memory map of process 4 Process 4 2 x86 address translation Physical Address

Memory Management Chester Rebeiro IIT Madras

Memory map of process 1 Process 1 Memory map of process 2 Process 2 Sharing RAM Memory map of process 3 Process 3 Memory map of process 4 Process 4 2

x86 address translation Physical Address Segmentation Paging CPU Unit Unit Logical Linear Address Address (segment Physical + Memory offset) 3

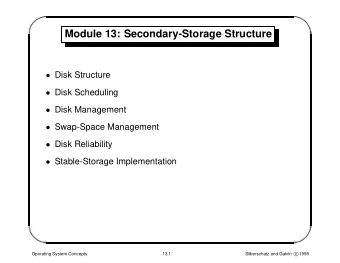

x86 Memory Management 4

Segmentation 5

Executing Programs (Process) • Process – A program in execution – Present in the RAM – Comprises of $gcc hello.c • Executable instructions • Stack Executable • Heap Process (a.out) • State in the OS (in kernel) $./a.out – State contains : registers, list of open files, related Stored on Executes from processes, etc. hard disk RAM 6

Segments (an example) stack segment Stack heap segment Heap data segment Data text segment Text 7

Segmentation ( logical to linear address) Stack Logical address Heap Data Text 8

Example 0x3000 (descriptor table) 0x3000 Segment Base Limit pointer to descriptor table 0 - - 1 1000 1000 2 4000 500 3 8000 1000 4 9000 1000 (logical address) 1 + 1100 segment register (eg %CS) (linear address) 100 offset register (eg %eip) 9

Pointer to Descriptor Table • Global Descriptor Table (GDT) – Stored in memory • Pointed to by GDTR (GDT Register) – lgdt (instruction used to load the GDT register) 0 Segment Descriptor GDTR Segment Descriptor base size Segment Descriptor 47 16 0 Segment Descriptor Segment Descriptor Size : size of GDT GDT Base : pointer to GDT 10

Segment Descriptor Segment base (32 bit) 0 to 3 : privilege level (DPL_USER : 3, Kernel : 0) Segment limit (20 bit) Segment type : STA_X : executable segment STA_R : readable segment STA_W : writeable segment 11

Segment Descriptor in xv6 SEG(STA_W, 0, 0xFFFFFFFF, DPL_USER) ref : mmu.h ([7], 0752, 0769) 12

Segments in xv6 Segment Base Limit Type DPL Kernel Code 0 4 GB X, R 0 Kernel Data 0 4 GB W 0 User Code 0 4 GB X, R 3 User Data 0 4 GB W 3 13

Loading the GDT 1724 2308 struct segdesc gdt[NSEGS]; 0512 14

Virtual Memory 15

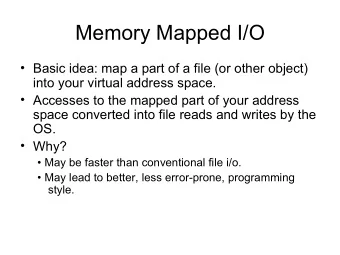

Paging Unit Linear address Physical address Segmentation Paging Unit Unit Linear Address Space of a process RAM 16

Virtual Memory Linear address space of process1 RAM 1 1 1 2 2 2 Because of the page table, 3 3 3 blocks need not be in contiguous 4 4 4 page frames 5 5 5 6 6 6 process page table 7 Every time a memory location block block page frame page frame 8 is accessed, the processor looks 1 1 14 1 9 into the page table to identify the 2 2 2 2 10 corresponding page frame number. 3 3 13 3 11 4 4 4 4 12 5 5 5 1 13 6 6 6 8 14 17

Virtual Memory process3 process1 process2 RAM 1 1 5 1 1 Blocks from 2 2 2 2 2 Several processes 3 3 3 3 can share pages in 3 4 4 4 4 RAM 4 simultaneously 5 4 5 6 2 6 2 process page table process page table process page table 7 6 block page frame block page frame block page frame 8 4 1 11 1 14 1 10 9 1 2 6 2 2 2 7 10 1 3 3 3 13 3 12 11 3 4 5 4 4 4 9 12 3 5 1 13 1 6 8 14 18

Virtual Memory process1 RAM Do we really need to load all blocks into 1 memory before the process starts 5 1 executing? 2 2 2 3 3 3 No. 4 4 4 5 4 Not all parts of the program are accessed 5 6 simultaneously. 2 6 Infact, some code may not even be 2 process page table 7 executed. 6 block page frame 8 4 Virtual memory takes advantage of this by 1 14 9 using a concept called demand paging. 1 2 2 10 1 3 13 11 3 4 4 12 3 5 1 13 1 6 8 14 19

Demand Paging Pages are loaded from disk to RAM, only Swap space when needed. RAM (on disk) 1 A ‘present bit’ in the page table indicates if 2 1 2 3 the block is in RAM or not. 3 3 5 4 4 5 6 If (present bit = 1){ block in RAM} 4 5 else {block not in RAM} 2 6 2 process page table in RAM 7 6 present bit block page frame P 8 4 1 14 1 9 If a page is accessed that is not present in 1 2 0 10 RAM, the processor issues a page fault 1 3 0 11 interrupt, triggering the OS to load the page 3 4 0 12 into RAM and mark the present bit to 1 6 5 1 0 1 13 1 6 8 1 14 20

Demand Paging Swap space RAM (on disk) If there are no pages free 5 for a new block to be loaded, 1 2 the OS makes a decision to 2 1 2 3 3 remove another block from RAM. 3 3 4 4 4 5 6 4 This is based on a replacement 5 2 policy, implemented in the OS. 6 2 process page table in RAM 7 Some replacement policies are 6 block page frame P 8 * First in first out 4 1 14 0 1 9 * Least recently used 1 2 2 1 10 * Least frequently used 1 3 14 1 0 11 3 4 4 1 12 The replaced block may need to 6 5 1 1 13 be written back to the swap 1 6 8 1 1 14 (swap out) 21

Demand Paging Swap space RAM (on disk) The dirty bit , in the page table 5 indicates if a page needs to be 1 2 written back to disk 2 1 2 3 3 3 4 If the dirty bit is 1, indicates 4 4 5 6 4 the page needs to be written 5 2 back to disk. 6 2 process page table in RAM 7 6 block page frame P D 8 4 1 14 1 0 1 1 9 1 2 2 1 1 10 1 3 14 1 0 0 0 11 3 4 4 1 1 12 6 5 1 1 0 13 3 6 8 1 1 14 22

Demand Paging Swap space RAM (on disk) Protection bits, in the page table 5 determine if 1 2 the page is executable, readonly, 2 1 2 3 3 and accessible by a user process. 3 4 4 4 5 6 4 5 2 6 protection bits 2 process page table in RAM 7 6 block page frame P D 8 4 1 14 0 1 1 1 11 1 9 1 2 2 1 1 10 10 1 3 14 1 0 0 0 00 0 11 3 4 4 1 1 11 12 6 5 1 1 0 01 13 3 6 8 1 1 1 10 1 14 23

2 Level Page Translation Dir Table Offset linear address Dir : 10 bits Table : 10 bits Offset : 12 bits Physical (CR3) Address (p) Number of Page tables is 2 10 = 1024. Total size of page tables is 4MB. But not contiguous! 24

Linear to Physical Address • 2 level page translation • How many page tables are present? • What is the maximum size of the process’ address space? ref : mmu.h (PGADDR, NPDENTRIES, NPTENTRIES, PGSIZE) – 4G 25

back to booting … 26

so far … Power on Reset • executes on reset. BIOS • does POST, initializes devices • loads boot loader to 0x07c00 and jump to it (all in real mode) bootloader • disable interrupts • Setup GDT (8941) • switch real mode to protected mode • setup an initial stack (8967) • load kernel from second sector of disk to 0x100000 • executes kernel (_start) 27

Memory when kernel is invoked (just after the bootloader) • Segmentation enabled but no paging Segmentation physical CPU logical Unit physical memory address address • Memory map kernel stack code logical data memory physical memory 0x100000 bootloader Slide taken from Anton Burtsev, Univ. of Utah 28

Memory Management Analysis Segmentation physical CPU Unit logical physical memory address address • Advantages – Got the kernel into protected mode (32 bit code) with minimum trouble • Disadvantages – Protection of kernel memory from user writes – Protection between user processes – User space restricted by physical memory • The plan ahead – Need to get paging up and running 29

entry The kernel executes from here 30

OS code Linker address • kernel.asm (xv6) • The linker sets the executable so that the kernel starts from 0x80100000 • 0x80100000 is a virtual address and not a physical address 31

Virtual Address Space Virtual 0xffffffff • Kernel memory mapped into every process - easy to switch between kernel and user modes Device memory • VA(KERNBASE:+PHYSTOP) à PA(0:PHYSTOP ) - convert from VA to PA just by +/- KERNBASE - easily write to physical page Kernel Memory - limits size of physical memory to 2GB +0x100000 Physical KERNBASE 0x80000000 PHYSTOP 0x100000 0 0 ref : memlayout.h (0200) 32

Virtual Address Space Virtual 0xffffffff • Linking address not the same as the loading address Device memory • Linking address 0x80100000 • Loading address 0x100000 Kernel Memory +0x100000 Physical KERNBASE 0x80000000 PHYSTOP 0x100000 0 0 ref : memlayout.h (0200) 33

Converting virtual to physical in kernel space 34

Enable Paging 1. Start of with a quick solution Aim is get the kernel running with paging enabled -- create a minimal paging environment ---- two pages of 4MB size (just sufficient to hold the OS) 2. Have an elaborate paging mechanism Create pages for each 4KB RAM block Allocate and manage free memory 35

Enable Paging Aim is to create two 4MB pages Turn on Page size extension 1 36

4MB Pages 37

Enable Paging Set Page Directory 2 38

Kernel memory setup • First setup two 4MB pages – Entry 0: Virtual addresses 0 to 0x04000000 à Physical addresses 0 to 4MB – Entry 512: Virtual addresses 0x80000000 to 0x84000000 à Physical addresses 0 to 4MB What would be the address generated before and immediately after paging is enabled? before : 0x001000xx Immediately after : 0x8001000xx So the OS needs to be present at two memory ranges 39

Enable Paging Turn on Paging 1 2 3 40

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.