Low Power Design Prof. Dr. J. Henkel CES - Chair for Embedded - PowerPoint PPT Presentation

Low Power Design Prof. Dr. J. Henkel CES - Chair for Embedded Systems KIT, Germany I. Introduction and Energy/Power Sources Prof. Jrg Henkel, Low Power Design, SS2014 ces.itec.kit.edu 2 Overview Reason

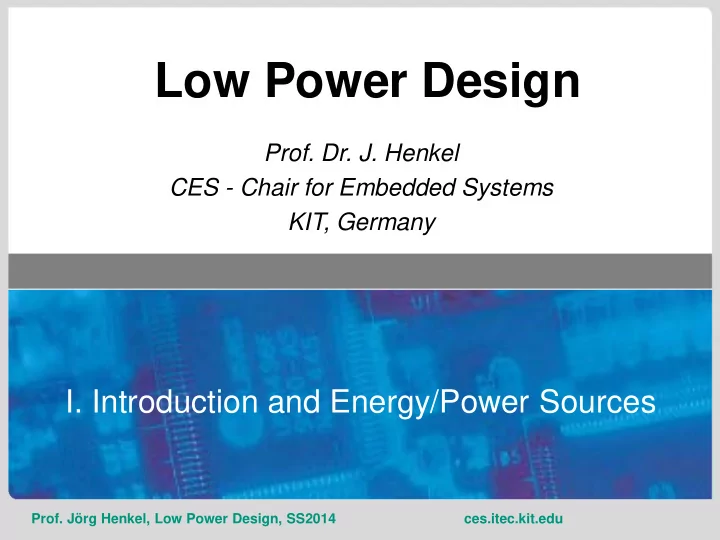

Low Power Design Prof. Dr. J. Henkel CES - Chair for Embedded Systems KIT, Germany I. Introduction and Energy/Power Sources Prof. Jörg Henkel, Low Power Design, SS2014 ces.itec.kit.edu

2 Overview Reason for Low Power Design: motivation Specific need for low power in embedded systems: examples Battery issues (re-chargeable batteries) Power/energy sources Prof. Jörg Henkel, Low Power Design, SS2014 ces.itec.kit.edu

3 Why design for low power/energy? Portable Systems n Thermal Considerations n Notebooks, smartphones, ä 10 o C increase in operating ä tablets, cameras, etc. temperature => component 32% of PC market, and growing l failure rate doubles Battery-driven - long battery life ä Packaging: ceramic vs . plastic ä crucial Cooling requirements ä System cost, weight limited by ä batteries Increasing levels of n 40W, 10 hrs @ 20-35 W- integration / clock l hr/pound = 7-20 pounds (Src: A. Raghunathan, NEC) frequencies make the Slow growth in battery l technology problem worse Must reduce energy drain LOW n 10cm 2 , 500 MHz => 315Watts ä from batteries POWER Reliability Issues n Environmental Concerns Electro-migration n ä EPA estimate: 80% of office IR drops on supply lines ä ä equipment electricity is used Inductive effects ä in computers Tied to peak/average n “Energy Star” program to ä power consumption recognize power efficient PCs Power management standard ä for desktops and laptops Drive towards “Green PC” n Prof. Jörg Henkel, Low Power Design, SS2014 ces.itec.kit.edu

4 (Src: F. Pollack, Intel Prof. Jörg Henkel, Low Power Design, SS2014 ces.itec.kit.edu

5 Power consumption: motivation Pentium Crusoe Pentium 4 Crusoe Processor (source: www.transmeta.com) Prof. Jörg Henkel, Low Power Design, SS2014 ces.itec.kit.edu

6 Exploring different FPGA chips (The worst stress-scenario) Temp max: 125.0°C Temp min: 81.5 °C Thermal variation: 43.5 Spatial thermal gradient: ~1.81 °C/mm Properties of the tested region Src: Henkel, Amrouch, Ebi resources LUTs 2000 FFs 2000 DSPs 12 BRAMs 0 DCM 1 Frequency 550 MHz Area 13% of chip Xilinx Virtex-5 FX100t, package ff1136, speed -3 (65nm) Prof. Jörg Henkel, Low Power Design, SS2014 ces.itec.kit.edu

Dennard Scaling, Circuit Heat “Circuit heat generation is the main limiting factor for scaling of device speed and switch circuit density” By Jeff Welser, Director SRC Nanoelectronics Research Initiative, IBM, Folgerung? Opening Keynote Address ICCAD 2007 Classical scaling Leakage limited scaling S 2 Device count S 2 Device count Device frequency S Device frequency S Device power (cap) 1/S Device power (cap) 1/S Device power (V dd ) 1/S 2 Device power ( V dd ) ~1 Utilization 1 1/S 2 Utilization (Src: “Dennard Scaling”)

Power Wall: 8 Is Multi-Core Scaling Promising? Assumption: Scaling Factor S=2 45nm 32nm 22nm 65nm 2 Cores 4 Core 8 Core 16 Core @ < 2GHz @ >= 2GHz @ > 2GHz @ >= 2GHz 8 Dark Cores Tradeoff 22nm between #Cores and 16 Core Frequency @ >= 4GHz 12 Dark Cores Prof. Jörg Henkel, Low Power Design, SS2014 ces.itec.kit.edu

9 Power Wall The Dark Silicon Problem emerged due to the utilization wall as a result of Memory wall Parallelism wall Power Wall => Chips cannot be driven with a power greater than their power budgets given as TDP (thermal design power) Power dissipation, peak power, and power density are the ultimate limiting factors , thus determining the amount of Dark Silicon Power is more expensive than area Regardless of available parallelism, chip organization & topology, multicore scaling is power limited @22 nm: Dark Silicon≈20% -50% J. Allred, S. Roy, K. Chakraborty, “Designing for Dark Silicon: A Methodological Perspective on Energy Efficient Systems”, in ISLPED, 2012 @8 nm: Dark Silicon > 50%-70% H. Esmaeilzadeh, E. Blem, R. St. Amant, K. Sankaralingam, D. Burger, “Dark Dark Silicon is must be kept powered-OFF Silicon and the End of Multicore Scaling”, in International Symposium on Computer Architecture (ISCA), 2011 Prof. Jörg Henkel, Low Power Design, SS2014 ces.itec.kit.edu

10 Power Wall: Trends Even if there is unlimited Parallelism, The Speedup is limited by the Power Constraint Scaling Limits when Dark Silicon Dominates H. Esmaeilzadeh, E. Blem, R. St. Amant, K. Sankaralingam, D. Burger, “Dark Silicon and the End of Multicore Scaling”, in International Symposium on Computer Architecture (ISCA), 2011 Prof. Jörg Henkel, Low Power Design, SS2014 ces.itec.kit.edu 10

11 Power and Heat in FPGAs Scr: Amrouch, Ebi, Henkel Thermal Camera Virtex-5 FPGA without packaging Activity migration between two cores at the interval of 154 MCycle Temperature [°C] Core1 Core2 63 60 57 54 51 48 45 1 67 133 199 265 331 397 463 529 595 661 727 793 859 925 991 1057 1123 1189 1255 1321 1387 1453 1519 1585 1651 1717 1783 1849 Time [sec] Prof. Jörg Henkel, Low Power Design, SS2014 ces.itec.kit.edu

Temperature in 3D Problem: vertical heat flow Only one layer directly interfaces with the heat sink Heat needs to dissipate through multiple layers The heat sink is located on top of the chip Hot cores distant to the heat sink dissipate their heat through other layers Silicon has a low thermal conductivity! 150 W/(m*K) (Silicon) 401 W/(m*K) (Copper)

13 Energy vs . Programmability Large (100X – 1000X) gap in energy efficiency between fully programmable and fully custom implementations Ample scope for tradeoffs Source: Rabaey et. al ., IEEE Computer, July 2000 Prof. Jörg Henkel, Low Power Design, SS2014 ces.itec.kit.edu

14 Power consumption by processing type Operations/Watt [MOPS/mW] Ambient Intelligence 10 DSP-ASIPs 1 µPs 0.1 poor design generation 0.01 techniques Technology 1.0µ 0.5µ 0.25µ 0.13µ 0.07µ (Src:[Marw03]) Prof. Jörg Henkel, Low Power Design, SS2014 ces.itec.kit.edu

Relationship between Power and 15 Energy P E t ∫ = E P dt Energy: 1 Ws = 1 VAs = 1 Joule = 1 Nm Prof. Jörg Henkel, Low Power Design, SS2014 ces.itec.kit.edu

16 Power vs. Energy Minimizing the power consumption is important for the design of the power supply the design of voltage regulators the dimensioning of interconnect short term cooling Minimizing the energy consumption: Limited availability of energy (mobile systems, try to maximize the amount of computation that can be accomplished with a given amount of energy) through: limited battery capacities (only slowly improving) very high costs of energy (solar panels, in space) cooling high costs limited space dependability long lifetimes, low temperatures (Src:[Marw03]) Prof. Jörg Henkel, Low Power Design, SS2014 ces.itec.kit.edu

17 HW Power Consumption 1 2 ) ( Power Cap = . _ Switching _Power 2 C V . . . A f L dd + Leakage/Static Power + … Power analysis High-level synthesis, RTL optimizations iteration times Decreasing design iteration times Architecture-level Power models power analysis for macroblocks, seconds - minutes Behavior level control logic Logic synthesis Register-transfer level minutes - hours Power models Logic-level for gates, cells, power analysis nets Transistor-level/ Logic level Layout synthesis hours - days Transistor level Transistor-level power analysis (src: A. Raghunathan, NEC) Prof. Jörg Henkel, Low Power Design, SS2014 ces.itec.kit.edu

18 Power/Energy-Conscious Applications -Some examples- Prof. Jörg Henkel, Low Power Design, SS2014 ces.itec.kit.edu

19 Example 1: E-Textiles - Smart Shirt - Source: [Marc03] Prof. Jörg Henkel, Low Power Design, SS2014 ces.itec.kit.edu

20 Example 2: Medical Diagnostics (source: Jan Madsen DTU) Prof. Jörg Henkel, Low Power Design, SS2014 ces.itec.kit.edu

21 Example 3: Sensor Networks Disaster Prevention & Energy-efficient Manufacturing plants & Power distribution Emergency buildings • Improve reliability, operating efficiency Response • $55 B / year opportunity in the US Health care • Unwired operating “ Smart ” environments Traffic control rooms • Homes, Offices, Schools, … • Reduce commute time • Early detection of • Convenience, Productivity, Security cardiac attacks by 15 min => $15B/year in California alone (source: A. Raghunathan, NEC) Prof. Jörg Henkel, Low Power Design, SS2014 ces.itec.kit.edu

22 More examples Banking & Money transfer smart cards, … Consumer cell phone, MP3 player, PDA, … Clothing electronic textiles Environment sensor networks Healthcare hearings aids, pace maker, … Telecom Systems satellite, … … Prof. Jörg Henkel, Low Power Design, SS2014 ces.itec.kit.edu

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.