Low Power and Reliable Interconnection with Low Power and Reliable - PowerPoint PPT Presentation

Network-on-Chip Symposium, April 2008 Low Power and Reliable Interconnection with Low Power and Reliable Interconnection with Self-Corrected Green Coding Scheme Self-Corrected Green Coding Scheme for Network-on-Chip for Network-on-Chip

Network-on-Chip Symposium, April 2008 Low Power and Reliable Interconnection with Low Power and Reliable Interconnection with Self-Corrected Green Coding Scheme Self-Corrected Green Coding Scheme for Network-on-Chip for Network-on-Chip Po-Tsang Huang, Wei-Li Fang, Yin-Ling Wang and Wei Hwang Department of Electronics Engineering & Institute of Electronics, and Microelectronics and Information Systems Research Center, National Chiao-Tung University, HsinChu 300, Taiwan

Outline � Introduction � Low power joint bus/error correction coding concept � Self-corrected green coding scheme � Triplication error correction coding stage � Green bus coding stage � Simulation Results � Conclusions � National Chiao-Tung University 2 NoCS 2008

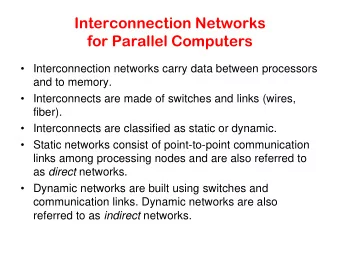

Motivation � Network-on-chip : an effective Physical design of NoC solution to integrate multi-core switch system and a process independent Link wires network interconnection architecture. interface � National Chiao-Tung University 3 NoCS 2008

Introduction � Three critical issues for on-chip communication � Delay – coupling capacitances � Power – parasitic and coupling capacitances � Reliability – degrading due to noises � Novel design techniques are proposed to overcome the crosstalk effect and further provides a reliability bound for on-chip interconnection. � Joint bus and error correction coding schemes � National Chiao-Tung University 4 NoCS 2008

Outline � Introduction � Low power joint bus/error correction coding concept � Self-corrected green coding scheme � Triplication error correction coding stage � Green bus coding stage � Simulation Results � Conclusions � National Chiao-Tung University 5 NoCS 2008

A unified framework of coding in SoC k l Crosstalk Avoidance Code(CAC) Error Control Linear Crosstalk Code (ECC) Code(LXC) m m c � Crosstalk avoidance codes (CAC) � Avoid specific code patterns or code transitions to reduce delay and power dissipation. � Error control codes (ECC) � Detect and correct the error bits � Linear crosstalk code (LXC) � Shielding link wires, duplicated bits � National Chiao-Tung University 6 NoCS 2008

Serialization technique for link wires K-to-N serialization K/N bits K bits physical transfer unit (phit) the data which is divided and transmitted through micro-network Area Cost (1/N 2 ) Switch delay Area Cost (1/N 2 ) Switch delay Crosstalk , signal-to signal skew Signaling Rate -> predefined well-structured link � National Chiao-Tung University 7 NoCS 2008

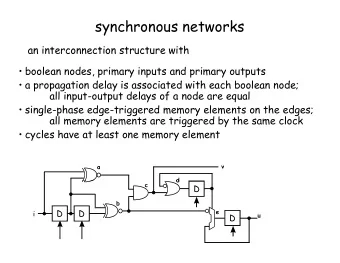

Self-corrected green coding scheme � Self-corrected green coding scheme � triplication error correction coding stage, green bus coding stage � Shorter delay for ECC, more energy reduction and smaller area Switch Fabric Processor Element decoder ECC Bus ECC interface Serializer Encoder encoder ECC encoder Joint bus and error correction Channels through coding with serializer/deserializer Multi switch fabrics ECC Processor decoder Element interface Bus ECC encoder ECC Deserializer decoder Decoder � National Chiao-Tung University 8 NoCS 2008

Outline � Introduction � Low power joint bus/error correction coding concept � Self-corrected green coding scheme � Triplication error correction coding stage � Green bus coding stage � Simulation Results � Conclusions � National Chiao-Tung University 9 NoCS 2008

Triplication error correction coding stage triplication set � The hamming distance of each set is equal to 3. � A constant delay of a majority gate and much smaller than others � Rapid correction ability by self-corrected mechanism in bit-level. � National Chiao-Tung University 10 NoCS 2008

Word error probability of triplication � Error correction mechanisms � Reducing supply voltage of channels without compromising the reliability of system. σ 2 � A Gaussian distributed noise voltage V N with variance N is added to the signal waveform. ∞ 2 ⎛ ⎞ y − 1 V ( ) ∫ ε = = ⎜ dd ⎟ Q 2 Q x e dy σ , π ⎝ ⎠ 2 2 n x ≈ ε − ε 2 3 P 3 k 2 k Word-error probability : triplication where k : the size of bit-width ε : bit-error probability � National Chiao-Tung University 11 NoCS 2008

Green Bus Coding Stage � Green bus coding stage Establish triplication Design Flow capacitance matrix Ct by � Reducing coupling effect RLC cyclic model Approximate Cyclic model Derive power formula Transition C C C with the coefficient α definition 1 , 2 2 , 3 3 , 4 C C C C Find the codeword to 4 , 4 3 , 3 1 , 1 2 , 2 minimize the value, α Triplication capacitance matrix Map the codeword to + λ − λ ⎡ ⎤ 3 0 0 data-word ⎢ ⎥ − λ + λ − λ C 3 0 λ = ⎢ ⎥ X = ⎢ t C C , ⎥ − λ + λ − λ L C 0 3 Circuit Implementation L ⎢ ⎥ − λ + λ ⎣ ⎦ 0 0 3 � National Chiao-Tung University 12 NoCS 2008

Five types of signal transitions � Static transitions Type2 H Type3 Type1 L L L Cx Cx Cx L L H L H Type3 (no switching or � Dynamic transitions switching in the same direction) H Type4 Type5 L H L Cx Cx L H L H signal aliasing � National Chiao-Tung University 13 NoCS 2008

Triplication Power formula � The power consumption can be derived as follow. = ∗ ∗ ∗ α 2 P f C V Type 2,5 Type 1 L DD ( ) α = + + + + + λ ⊕ + ⊕ + ⊕ + ⊕ 3( r r r r r ) r r r r r r r r 1 2 3 4 5 1 2 2 3 3 4 4 5 ( ) + λ + + + 4 d d d d 12 23 34 45 α is a modified switching activity with considering coupling capacitances. ( ) ⊕ � The meaning of is that only one line is r r i j changing between two lines as type 1. ( ) � For the term of , it is about the two lines change in d ij the opposite direction as type2 and type5 transitions. � National Chiao-Tung University 14 NoCS 2008

Codeword of green bus coding � National Chiao-Tung University 15 NoCS 2008

Encoder/decoder for green bus coding � More simple and effective � Avoid forbidden overlap condition (FOC) and forbidden pattern condition (FPC) and reduce forbidden transition condition (FTC) 0 0 1 1 2 2 3 3 4 Encoder Decoder � National Chiao-Tung University 16 NoCS 2008

Outline � Introduction � Low power joint bus/error correction coding concept � Self-corrected green coding scheme � Triplication error correction coding stage � Green bus coding stage � Simulation Results � Conclusions � National Chiao-Tung University 17 NoCS 2008

Energy reduction to un-coded code Simulation Condition : � UMC 90nm CMOS technology � The length of wires is set as 0.8mm of metal-4 with minimum width and spacing of 0.2um. Energy Reduction to uncoded bus (%) ⎛ ⎞ C λ = ⎜ X ⎟ ⎝ ⎠ C L � National Chiao-Tung University 18 NoCS 2008

Voltage of specific error correction coding (k=8) ≈ ε − ε 2 3 P 3 k 2 k triplication Voltage (V) � National Chiao-Tung University 19 NoCS 2008

Voltage of specific error correction coding (k=32) ≈ ε − ε 2 3 P 3 k 2 k triplication Voltage (V) � National Chiao-Tung University 20 NoCS 2008

Summaries of different joint coding codec � The proposed self-corrected green coding scheme has the smallest area overhead of codec. � For the smallest delay, it is more suitable for the network- on-chip architecture. � National Chiao-Tung University 21 NoCS 2008

Summaries of different joint coding schemes � Except for s-c green coding, DAP and DSAP, the critical delay of codec depends on the decoder, others are not appropriate for integrating into switch fabrics because of long critical delay . � National Chiao-Tung University 22 NoCS 2008

Outline � Introduction � Low power joint bus/error correction coding concept � Self-corrected green coding scheme � Triplication error correction coding stage � Green bus coding stage � Simulation Results � Conclusions � National Chiao-Tung University 23 NoCS 2008

Conclusions � Self-corrected green coding scheme is presented to construct reliable and low power interconnection for NoC. � Triplication error correction stage � Rapid correction ability to reduce the physical transfer unit size � Self-corrected in bit level � Green bus coding stage � More energy reduction by a joint triplication bus power model � Based on UMC 90um CMOS technology, compared to un- coded code, self-corrected green coding can achieve 34.4% and 67.3% energy saving at voltage 1.2v and 0.84v, respectively. � National Chiao-Tung University 24 NoCS 2008

Network-on-Chip Symposium, April 2008 Thanks for your Thanks for your attention!! attention!!

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.