Lecture 7 Adders and Multipliers 1 11/22/2019 Ripple Carry Adder - PowerPoint PPT Presentation

Lecture 7 Adders and Multipliers 1 11/22/2019 Ripple Carry Adder b3 a3 b2 a2 b1 a1 a0 cin (c0) b0 cout FA3 FA2 FA1 FA0 (c4) M4 M3 M2 M1 c1 c2 c3 s3 s2 s1 s0 Key observations, the value of the A B cin cout 0

Lecture 7 – Adders and Multipliers 1 11/22/2019

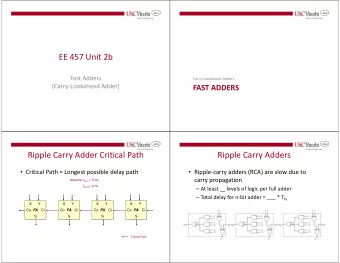

Ripple Carry Adder b3 a3 b2 a2 b1 a1 a0 cin (c0) b0 cout FA3 FA2 FA1 FA0 (c4) M4 M3 M2 M1 c1 c2 c3 s3 s2 s1 s0 Key observations, the value of the A B cin cout 0 0 0 0 carry into any stage of a multi-cell Kill 0 0 1 0 adder depends only on 0 1 0 0 The data bit of previous stage The carry into the 1 st stage 1 0 0 0 Propagate 0 1 1 1 When both inputs 0, no carry 1 0 1 1 When one is 0, the other is 1, propagate 1 1 0 1 carry input Generate When both are 1, then generate a carry 1 1 1 1 2 11/22/2019

Carry-lookahead adder Generate Gi = ai * bi Propagate Pi = ai xor bi; or Pi = ai + bi Pi and Gi are mutually exclusive Because Pi is asserted when (ai,bi)={(1,0), (0,1)}; Gi is asserted when (ai,bi)=(1,1) Si = ai xor bi xor ci = Pi xor ci c(i+1) = (ai+bi)*ci + a*b = (ai xor bi) * ci + a*b = Pi* ci + Gi Write carry out as function of preceding G, P, and cout c1 = G0 + P0*c0 c2 = G1 + P1*c1 c3 = G2 + P2*c2 c4 = G3 + P3*c3

Reducing the complexity c1 = G0 + (P0 * c0) c2 = G1 + (P1 * [G0 + P0 * c0]) = G1 + (P1 * G0) + (P1 * P0 * c0) c3 = G2 + (P2 * G1) + (P2 * P1 * G0) + (P2 * P1 * P0 * c0) That is ci can only use c0 and P(i-1) ... P0 and G(i-1) ... G0 Increase speed at what cost ? Can you illustrate how to build a 32-bit adder with carry look ahead?

Carry Look Ahead Adder c0 = Cin A B Cout 0 0 0 “kill” S A0 0 1 Cin “propagate” G 1 0 Cin “propagate” B0 P 1 1 1 “generate” c1 = G0 + c0 • P0 S G = A and B A1 G P = A xor B B1 P c2 = G1 + G0 • P1 + c0 • P0 • P1 S A2 G B2 P c3 = G2 + G1 • P2 + G0 • P1 • P2 + c0 • P0 • P1 • P2 S A3 G G B3 P P c4 = . . .

Multiply Overview Binary multiplication is just a bunch of left shifts and adds n multiplicand multiplier partial can be formed in parallel product n and added in parallel for array faster multiplication double precision product 2n

Division Overview Division is just a bunch of quotient digit guesses and right shifts and subtracts n n quotient 0 0 0 dividend divisor 0 partial 0 remainder array 0 remainder n

Multiplication: design and implementation More complicated than addition • accomplished via shifting and addition More time and more area • m bits x n bits = m+n bit product Let's look at 3 (unsigned) versions of multiplication designs in the next few slides

Unisigned shift-add multiplier (version 1) 64-bit Multiplicand reg, 64-bit Adder, 64-bit Product reg, 32-bit multiplier reg Shift Left Multiplicand 64 bits Multiplier Shift Right 64-bit Adder 32 bits Write Product Control 64 bits Multiplier = datapath + control

Multiply Algorithm Version 1 Start Multiplier0 = 1 Multiplier0 = 0 1. Test Multiplier0 1a. Add multiplicand to product & place the result in Product register Product Multiplier Multiplicand 2. Shift the Multiplicand register left 1 bit. 0000 0000 0011 0000 0010 1: 0000 0010 0011 0000 0010 2: 0000 0010 0011 0000 0100 3. Shift the Multiplier register right 1 bit. 3: 0000 0010 0001 0000 0100 1: 0000 0110 0001 0000 0100 2: 0000 0110 0001 0000 1000 32nd 3: 0000 0110 0000 0000 1000 No: < 32 repetitions repetition? 0000 0110 0000 0000 1000 Yes: 32 repetitions Done

Observations on Multiply Version 1 1 clock per cycle => ≈ 100 clocks per multiply because of 32 repetitions, 3 steps in one repetition • Ratio of add/sub to multiply is from 5:1 to 100:1 • Slow 0’s inserted in the rightmost bit of multiplicand as shifting left => least significant bits of product never changed once formed 1/2 bits in multiplicand always 0 • MSB are 0s at the beginning • 0 is inserted in LSB as multiplicand shifting left => 64-bit multiplicand register is wasted => 64-bit adder is wasted Instead of shifting multiplicand to left, let’s shift product to right

MULTIPLY HARDWARE Version 2 32 -bit Multiplicand reg, 32 -bit ALU, 64-bit Product reg, 32-bit Multiplier reg Multiplicand 32 bits Multiplier Shift Right 32-bit Adder 32 bits Shift Right Product Control Write 64 bits

Start Multiply Algorithm Version 2 Multiplier0 = 1 Multiplier0 = 0 1.Test Multiplier0 1a. Add multiplicand to the left half of product & place the result in the left half of Product register Product Multiplier Multiplicand 0000 0000 0011 0010 1: 0010 0000 0011 0010 2. Shift the Product register right 1 bit 2: 0001 0000 0011 0010 3: 0001 0000 0001 0010 1: 0011 0000 0001 0010 2: 0001 1000 0001 0010 3. Shift the Multiplier register right 1 bit 3: 0001 1000 0000 0010 1: 0001 1000 0000 0010 2: 0000 1100 0000 0010 32nd 3: 0000 1100 0000 0010 No: < 32 repetition 1: 0000 1100 0000 0010 repetition? 2: 0000 0110 0000 0010 3: 0000 0110 0000 0010 Yes: 32 repetitions Done 0000 0110 0000 0010

Start Still more wasted space in Version 2 Multiplier0 = 1 Multiplier0 = 0 1.Test Multiplier0 1a. Add multiplicand to the left half of product & place the result in the left half of Product register Product Multiplier Multiplicand 0000 0000 0011 0010 1: 0010 0000 0011 0010 2. Shift the Product register right 1 bit 2: 0001 0000 0011 0010 3: 0001 0000 0001 0010 1: 0011 0000 0001 0010 2: 0001 1000 0001 0010 3. Shift the Multiplier register right 1 bit 3: 0001 1000 0000 0010 1: 0001 1000 0000 0010 2: 0000 1100 0000 0010 32nd No: < 32 repetition 3: 0000 1100 0000 0010 repetition? 1: 0000 1100 0000 0010 2: 0000 0110 0000 0010 3: 0000 0110 0000 0010 Yes: 32 repetitions Done 0000 0110 0000 0010

Observations on Multiply Version 2 Product register wastes space that exactly matches size of multiplier => combine Multiplier register and Product register

MULTIPLY HARDWARE Version 3 32-bit Multiplicand reg, 32 -bit ALU, 64-bit Product reg, ( 0- bit Multiplier reg) Multiplicand 32 bits 32-bit ALU Shift Right Product (Mult iplier) Control Write 64 bits

Start Multiply Algorithm Version 3 Product0 = 1 Product0 = 0 1.Test Product0 1a. Add multiplicand to the left half of product & place the result in the left half of Product register Product Multiplicand 2. Shift the Product register right 1 bit 0000 0011 0010 1: 0010 0011 0010 2: 0001 0001 0010 1: 0011 0000 0010 2: 0001 1000 0010 1: 0001 1000 0010 2: 0000 1100 0010 32nd 1: 0000 1100 0010 No: < 32 repetition 2: 0000 0110 0010 repetition? 0000 0110 0010 Yes: 32 repetitions Done

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.