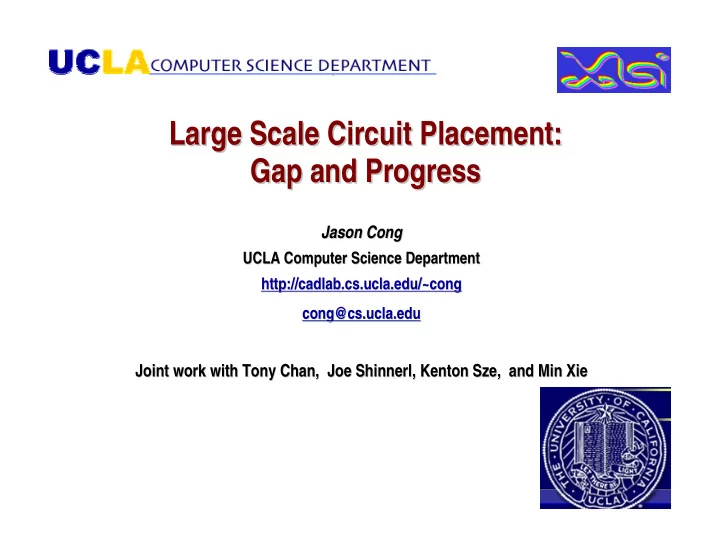

Large Scale Circuit Placement: Large Scale Circuit Placement: Gap - PowerPoint PPT Presentation

Large Scale Circuit Placement: Large Scale Circuit Placement: Gap and Progress Gap and Progress Jason Cong Jason Cong UCLA Computer Science Department UCLA Computer Science Department http://cadlab.cs.ucla.edu cadlab.cs.ucla.edu/~cong

Large Scale Circuit Placement: Large Scale Circuit Placement: Gap and Progress Gap and Progress Jason Cong Jason Cong UCLA Computer Science Department UCLA Computer Science Department http://cadlab.cs.ucla.edu cadlab.cs.ucla.edu/~cong /~cong http:// cong@cs.ucla.edu cong@cs.ucla.edu Joint work with Tony Chan, Joe Shinnerl Shinnerl, Kenton , Kenton Sze Sze, and Min , and Min Xie Xie Joint work with Tony Chan, Joe

Outline Outline Introduction � Introduction � � Problem Description � Problem Description � Popular Methods � Popular Methods Gap Analysis of Existing Placement Algorithms � Gap Analysis of Existing Placement Algorithms � � PEKO Benchmark Construction � PEKO Benchmark Construction � Experiment Results � Experiment Results UCLA mPL5 � UCLA mPL5 � � Multiscale Optimization Framework � Multiscale Optimization Framework � Generic Force � Generic Force- -Directed Formulation Directed Formulation � Multiscale Nonlinear � Multiscale Nonlinear- -Programming Solution Programming Solution 3/29/2005 UCLA VLSICAD LAB 2

Complex IC Design Example Complex IC Design Example High- -end Automotive A/V application end Automotive A/V application � High � � 10M Gates � 10M Gates � 70 clocks (320 MHz) � 70 clocks (320 MHz) � Technology: 0.13u, 6LM � Technology: 0.13u, 6LM Courtesy of Magma Design Automation Courtesy of Magma Design Automation 3/29/2005 UCLA VLSICAD LAB 3

VLSI CAD VLSI CAD � Computer Computer- -aided design (CAD) of very large aided design (CAD) of very large- -scale integrated (VLSI) circuits scale integrated (VLSI) circuits � � Electronic design automation (EDA) Electronic design automation (EDA) � 3/29/2005 UCLA VLSICAD LAB 4

ITRS 2004 (Int ’ l Tech. Roadmap for Semiconductors) ITRS 2004 (Int ’ l Tech. Roadmap for Semiconductors) Year of Year of 2003 2004 2005 2006 2007 2008 2009 2003 2004 2005 2006 2007 2008 2009 production production DRAM ½ DRAM ½ pitch pitch 100 90 80 70 65 57 50 100 90 80 70 65 57 50 (nm) (nm) Functions/Chip at Functions/Chip at production production 307 307 386 386 487 487 614 614 773 773 974 974 1227 1227 (M transistors) (M transistors) Chip size at Chip size at 280 28 80 0 28 80 0 28 80 0 280 28 80 0 28 80 0 280 2 2 2 280 2 2 production (mm 2 2 ) ) production (mm On chip local On chip local 2976 4171 5204 6783 9285 10972 12369 2976 4171 5204 6783 9285 10972 12369 clock (MHz) clock (MHz) Maximum wiring Maximum wiring 13 14 15 15 15 16 16 13 14 15 15 15 16 16 level level 3/29/2005 UCLA VLSICAD LAB 5

Outline Outline Introduction � Introduction � � Problem Description � Problem Description � Popular Methods � Popular Methods Gap Analysis of Existing Placement Algorithms � Gap Analysis of Existing Placement Algorithms � UCLA mPL5 � UCLA mPL5 � 3/29/2005 UCLA VLSICAD LAB 6

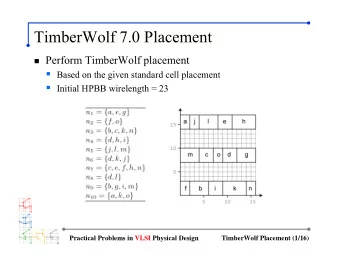

Circuit Placement Problem Statement Circuit Placement Problem Statement A B A netlist D C E F A cell A net G H I � Given Given � � A set of cells ( modules ) of fixed dimensions and the � A set of cells ( modules ) of fixed dimensions and the Bad placement interconnections interconnections between them between them – – a a netlist netlist � Find Find � � The position of each cell, such that � The position of each cell, such that • no overlap ( and enough routing space ) • no overlap ( and enough routing space ) • minimize total length of all interconnections • minimize total length of all interconnections • minimize routing congestion, delay, • minimize routing congestion, delay, … … � An NP An NP- -hard problem hard problem � Good placement 3/29/2005 UCLA VLSICAD LAB 7

Popular Placement Methods Popular Placement Methods Placement problem has been studied extensively for over 30 years Placement problem has been studied extensively for over 30 years � Iterative improvement Iterative improvement � � Repeatedly rearrange small subsets of modules � Repeatedly rearrange small subsets of modules � E.g. Simulated annealing � E.g. Simulated annealing � Min Min- -cut based placement cut based placement � � Recursively bi � Recursively bi- -partition modules in a way that minimize partition modules in a way that minimize connections between partition blocks connections between partition blocks � Quadratic placement with recursive legalization Quadratic placement with recursive legalization � � Initial solution by unconstrained quadratic wirelength � Initial solution by unconstrained quadratic wirelength minimization minimization � Gradually spread cells out to remove overlap � Gradually spread cells out to remove overlap 3/29/2005 UCLA VLSICAD LAB 8

Simulated Annealing Based Placement Simulated Annealing Based Placement E.g. VPR [Betz and Rose, 1997 ] E.g. VPR [Betz and Rose, 1997 ] Overview Overview ? 1. Select a module. 2. Select one of its neighbors. 3. Evaluate the wirelength change due to swapping them. 4. If the swap decreases wirelength, accept it. Otherwise, accept the swap with probability 5. Repeat for reduced T until T approaches to 0 3/29/2005 UCLA VLSICAD LAB 9

Cutsize- -Driven Driven Recursive Top Recursive Top- -Down Partitioning Down Partitioning Cutsize After two stages, each cell has been assigned to one of four After three stages, each cell has been assigned to one of eight Initially, there is only netlist connectivity; no spatial possible subregions. As few nets as possible have been cut. possible subregions. As few nets as possible have been cut. information is available. Apply a standard partitioning algorithm to the given netlist. Iterative improvement by repartitioning with terminal 3/29/2005 UCLA VLSICAD LAB 10 propagation is essential. Multilevel partitioning algorithms are the most effective.

Cutsize- -Driven Driven Partitioning Partitioning- -Based Placement Based Placement Cutsize Cutsize = the number of nets not contained in just one � Cutsize = the number of nets not contained in just one � side of the partition side of the partition � Rent � Rent’ ’s rule shows that wirelength and cutsize correlate to s rule shows that wirelength and cutsize correlate to within about X 2 log N N [Wang et al, 2000]. [Wang et al, 2000]. within about X 2 log � Fast FM � Fast FM- -style iterations with terminal propagation style iterations with terminal propagation � Careful � Careful cutline cutline selection and selection and multiway multiway partitions can help partitions can help e.g. Capo, Feng- -Shui, Dragon Shui, Dragon � e.g. Capo, Feng � 3/29/2005 UCLA VLSICAD LAB 11

Quadratic Placement Quadratic Placement Optimality Condition: Q is the graph Laplacian Matrix: Example. Q = D – G 5 1 2 where D is the degree matrix and G is the graph adjacency matrix 4 3 2 5 4 3 3/29/2005 UCLA VLSICAD LAB 12

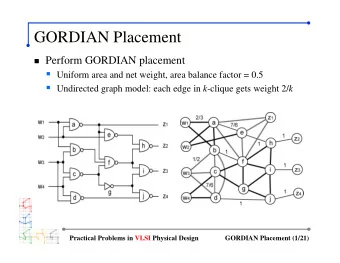

Quadratic Placement with Iterative Legalization Quadratic Placement with Iterative Legalization � Unconstrained Optimality Condition: Unconstrained Optimality Condition: � � Solve one large symmetric positive Solve one large symmetric positive- -definite linear system. definite linear system. � � Pads prevent cells from collapsing to a single point. Pads prevent cells from collapsing to a single point. � � Example: Gordian Example: Gordian- -L. L. � � Minimize cutsize, but use the given placement to form initial pa � Minimize cutsize, but use the given placement to form initial partitions rtitions (e.g., using x x- - or or y y- - coordinate median for coordinate median for cutline cutline) ) (e.g., using � New subregions generate new center � New subregions generate new center- -of mass constraints for subsequent of mass constraints for subsequent iterations iterations 3/29/2005 UCLA VLSICAD LAB 13

Example: Gordian- -L L- -style Placement style Placement Example: Gordian 3/29/2005 UCLA VLSICAD LAB 14

Outline Outline Introduction � Introduction � Gap Analysis of Existing Placement Algorithms � Gap Analysis of Existing Placement Algorithms � � PEKO Benchmark Construction � PEKO Benchmark Construction � Experiment Results � Experiment Results Highlights from UCLA mPL5 � Highlights from UCLA mPL5 � 3/29/2005 UCLA VLSICAD LAB 15

Why Is Placement Still a Problem? Why Is Placement Still a Problem? True, it has been studied over 30 years, but … … � True, it has been studied over 30 years, but � We need good solutions more then ever � We need good solutions more then ever � � One of most important steps in IC implementation flow � One of most important steps in IC implementation flow • Directly defines interconnects • Directly defines interconnects Difficult � Difficult � � Problem size grows 2X every 18 � Problem size grows 2X every 18- -24 months 24 months • Moore • Moore’ ’s Law s Law � Cannot place hierarchically without quality degradation � Cannot place hierarchically without quality degradation 3/29/2005 UCLA VLSICAD LAB 16

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.