Keep It Straight: Teaching Placement how to Better Handle Designs - PowerPoint PPT Presentation

Keep It Straight: Teaching Placement how to Better Handle Designs w ith Datapaths Samuel I. Ward, Myung-Chul Kim*, Natarajan Viswanathan*, Zhuo Li*, Charles Alpert*, Earl E. Swartzlander, Jr., David Z. Pan ECE Dept. The University of Texas at

Keep It Straight: Teaching Placement how to Better Handle Designs w ith Datapaths Samuel I. Ward, Myung-Chul Kim*, Natarajan Viswanathan*, Zhuo Li*, Charles Alpert*, Earl E. Swartzlander, Jr., David Z. Pan ECE Dept. The University of Texas at Austin, Austin, TX 78712 * IBM Austin Research Laboratory, 11501 Burnet Road, Austin, TX, 78758 {wardsi}@utexas.edu, {mckima}@umich.edu, {nviswan, lizhuo, alpert}@us.ibm.com,{eswartzla}@aol.com, {dpan}@cerc.utexas.edu Dept. of Electrical and Computer Engineering The University of Texas at Austin 1

Outline General Placement Overview and Motivation › Why is the current formulation a problem? › Key Contributions Structure Aware Placement Techniques (SAPT) › Global Placement Techniques » Skewed net weighting with step size scheduling » Fixed ‐ point and pseudo net alignment constraint › Detailed Placement Techniques » Bit ‐ stack aligned cell swapping » Datapath group repartitioning Experimental Results Future Work › Placement › Congestion

Why is There A Big Difference? Datapath Needs to Increase › Circuit Performance: Timing, congestion, and power › Manpower Performance: Design time, controllability › Stability: Drives design closure ASIC/Random needs to Lower › Congestion Number of Placable Instances ASIC 1M › Power › Design time 500k Microprocessor Where does this lead? Random Logic Datapath 250k Days Weeks Months Manual Design Effort per Transistor

Two Worlds: Samuel’s Hierarchy of Design Needs Modern industrial designs have two flows…why? › Different needs ‐ > primary objective is different › Different styles ‐ > tools tuned differently With different objectives can we unify the placement flow? › Which flow should we use? Datapath Random Logic/ASIC Design Style Primary Objective Performance Design Time Stability Major Challenge Congestion Secondary Needs Congestion Power Power Performance Performance Per Transistor High Low Development Cost High Low Design Time High Low

How Do We Unify the Placement Flow? Should we: › Develop a datapath placer able to place random logic? › Enhance current placers to place datapath logic? Wide industry acceptance of the random placer › Speed is impressive › Quality is impressive BUT, can we enhance placers for datapath?

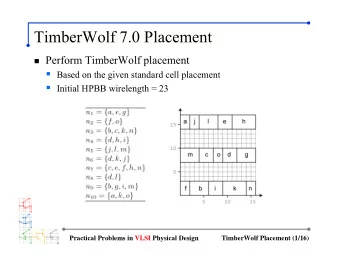

HPWL: Does the Model Hold for Datapath? Modified ISPD 2011 Datapath Benchmark spba01u Dragon FastPlace3 Major observations: NTUPlace3 › HPWL Accuracy Wirelength mPL6 › HPWL Fidelity SimPL Best StWL CAPO Manual Best HPWL 0.00E+00 1.00E+07 2.00E+07 3.00E+07 HPWL StWL Placer Modified ISPD 2011 Datapath Benchmark spbb01u mPL6 Surprising questions: FastPlace3 Wirelength › Is HPWL the right model for Dragon dp placement evaluation? SimPL Best StWL › Are there specific structures NTUPlace3 causing this issue? CAPO Manual Best HPWL 0.00E+00 2.00E+07 4.00E+07 Placer

Datapath HPWL Fidelity Example (a) Why exactly are the placement out<0> solutions bad? out<1> net1 HPWL model is: Fixed out<8> pins out<9> › exact for 2 ‐ pin and 3 ‐ pin nets › underestimate for > 3 ‐ pin nets (b) (c) Manual Placement: Automated Placement: StWL more accurately represents Total HPWL: 1442 Total HPWL: 1415 Total StWL: 1443 Total StWL: 1582 routed wirelength (RWL) Manually placed circuit: › HPWL: 2% worse › StWL: 9% better Based on this, can we: net1 net1 › Integrate alignment constraint instead of optimizing StWL directly?

Key Contributions of this Work Goals: › Integrate alignment constraint into force ‐ directed placement › Simultaneously place datapath and random logic Key Contributions › Study of obstacles to current academic placers: Inadequacies of the HPWL model for datapath logic › Key insight to StWL improvement through bit ‐ stack alignment: Alignment of the bitstack guides indirect StWL optimization Significantly improves total StWL and routing congestion Causes other cells to align › Novel placement techniques: Skewed Weighting with Step Size Scheduling Fixed ‐ Point Alignment Constraint Bit ‐ Stack Aligned Cell Swapping Datapath Group Repartitioning

Overall Flow Start Initial HPWL Optimization and Fixed Point Generation Datapath Aware Detailed Placement Pseudo Net Insertion Skewed Weighting with Step Size Bit-Stack Aligned Scheduling Cell Swapping Linear System Solver Datapath Group and Fixed Point Generation Repartitioning Fixed Point and Pseudo Net Alignment Constraint Legalization Convergence Done Global Placement Detailed Placement and Legalization

Alignment Net Example of an alignment net A weighted multi ‐ pin connection Connects between cells in a datapath group Modeled using the Bound2Bound model Datapath Cell Datapath Cells Aligned Horizontally Alignment Net

Skewed Weighting with Step Size Scheduling Start Initial HPWL Optimization and Fixed Point Generation Datapath Aware Detailed Placement Pseudo Net Insertion Skewed Weighting with Step Size Bit-Stack Aligned Scheduling Cell Swapping Linear System Solver Datapath Group and Fixed Point Generation Repartitioning Fixed Point and Pseudo Net Alignment Constraint Legalization Convergence Done Global Placement Detailed Placement and Legalization

Skewed Weighting with Step Size Scheduling Method for creating an alignment constraint during global placement › Skew net weighting along datapath direction › Cells align that are connected to the alignment net › Gradually increase the weighting Manipulate the skewed weighting › n Global placement iteration number › d k Datapath Direction › Scaling factor › δ i,j , γ i,j Horizontal and vertical alignment net weight › p(n) Step function › σ 2 (n) Cell position variance › w ij User Net weighting

Step Size Scheduling p(n) 0 M M/3 M/2 3M/4 Weighting Step Function 1.2 1 0.8 p(n) 0.6 0.4 0.2 0 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 Global Placement Iteration

Skewed Weighting Results σ 2 x (n) Variance 1200 1000 Low initial weight allows 800 movement of the bit ‐ stack Variance 600 Weigh tapers off near the end of 400 global placement 200 0 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 Global Placement Iteration n Weight 90 80 70 Scalar Weight 60 50 40 30 20 10 0 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 Global Placement Iteration (n)

Fixed ‐ Point Alignment Constraint Anchor Point Aligned Pseudonet (weight= /Length) cell g k (1) k d k = 0 cell g k (0) cell g k (2) Datapath cell shown in grey Directional weighting alone does not force alignment Modify fixed ‐ point location for alignment nets During the next global placement iteration: › Cells are “pulled” into alignment my modifying fixed ‐ point locations › Use the geometric mean to identify the position

Fixed ‐ Point Alignment Results Fixed ‐ Point alignment causes cells to be aligned almost perfectly Bit ‐ stack cells are aligned horizontally Nets are aligned vertically

Bit ‐ Stack Aligned Cell Swapping Start Initial HPWL Optimization and Fixed Point Generation Datapath Aware Detailed Placement Pseudo Net Insertion Skewed Weighting with Step Size Bit-Stack Aligned Scheduling Cell Swapping Linear System Solver Datapath Group and Fixed Point Generation Repartitioning Fixed Point and Pseudo Net Alignment Constraint Legalization Convergence Done Global Placement Detailed Placement and Legalization

Bit ‐ Stack Aligned Cell Swapping Existing Unaligned Region Proposed Aligned Region (x r , y u ) opt Swap region for cell j (x r , max y (g k ) + var(g k ) ) opt (x l , y l ) opt i i j j Maintain alignment during (x r , min y (g k ) - var(gk) ) opt detailed placement (DP) Minimize wrong direction “global moves” j i i j (a) (b)

Datapath Group Repartitioning Row(j+1) Use greedy moves to improve (a) bitstack alignment Row(j) Bipartition each alignment net s i Swap cells along the median if cut a i-1 a i b i b i-1 m i count improves Row(j+1) Discard move if HPWL degrades (b) Median point m i is the median of Row(j) the cells connected to the s i a i-1 b i a i b i-1 alignment net m i

Outline General Placement Overview and Motivation › Why is the current formulation a problem? Key Contributions Global Placement Techniques Detailed Placement Techniques Experimental Results Future Work › Placement › Congestion

SAPT Experimental Results: GP Plots of the vertical and horizontal alignments Base run shows the significant misalignment Skewed weighting allows for improved alignment: some jogging Fixed ‐ point constraint forces almost exact alignment LEGAL HPWL = 2385800 Base Run Skewed Weighting Fixed-Point Alignment LEGAL HPWL = 2461745 LEGAL HPWL = 2513500

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.