Chapter 2 <140>

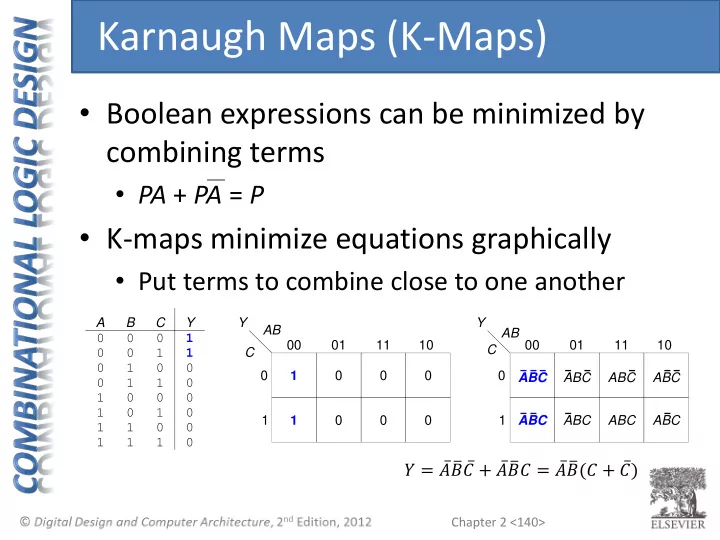

- Boolean expressions can be minimized by

combining terms

- PA + PA = P

- K-maps minimize equations graphically

- Put terms to combine close to one another

C 00 01 1 Y 11 10 AB 1 1 C 00 01 1 Y 11 10 AB ABC ABC ABC ABC ABC ABC ABC ABC B C 1 1 1 1 A 1 1 1 1 1 1 1 1 1 1 Y

Karnaugh Maps (K-Maps)

𝑍 = 𝐵 𝐶 𝐷 + 𝐵 𝐶 𝐷 = 𝐵 𝐶 (𝐷 + 𝐷 )