Introduction to 8085 Introduction to 8085 PIN DIAGRAM OF PIN - PDF document

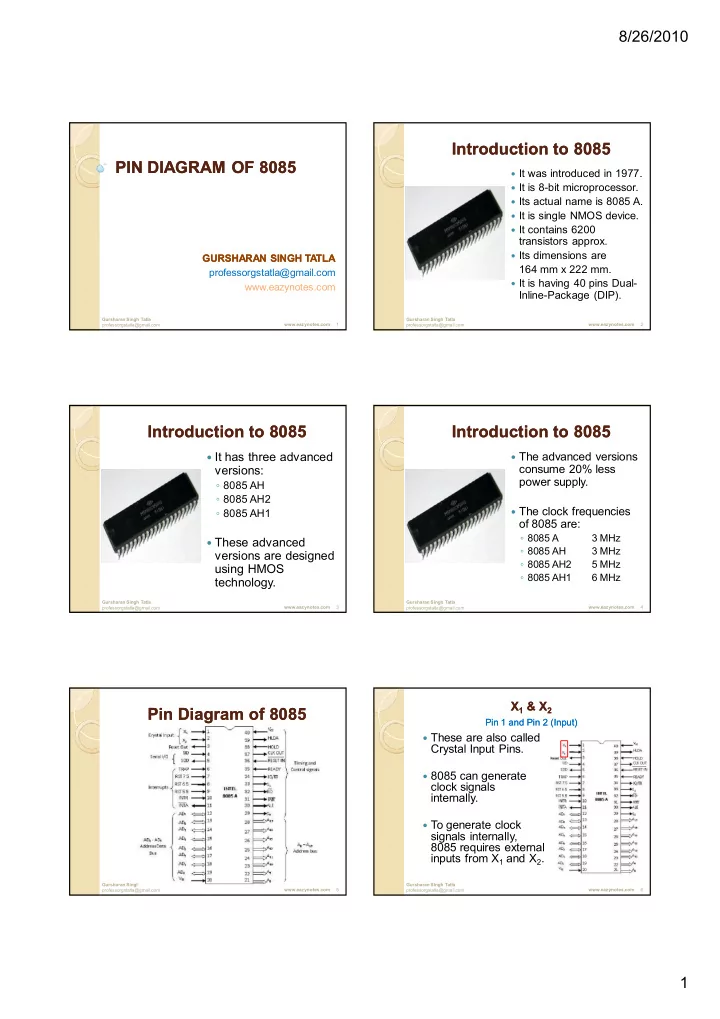

8/26/2010 Introduction to 8085 Introduction to 8085 PIN DIAGRAM OF PIN DIAGRAM OF 8085 8085 It was introduced in 1977. It is 8-bit microprocessor. Its actual name is 8085 A. It is single NMOS device. It contains 6200

8/26/2010 Introduction to 8085 Introduction to 8085 PIN DIAGRAM OF PIN DIAGRAM OF 8085 8085 It was introduced in 1977. It is 8-bit microprocessor. Its actual name is 8085 A. It is single NMOS device. It contains 6200 transistors approx. Its dimensions are GURSHARAN SINGH TA GURSHARAN SINGH TA TLA TLA 164 mm x 222 mm. professorgstatla@gmail.com It is having 40 pins Dual- www.eazynotes.com Inline-Package (DIP). Gursharan Singh Tatla Gursharan Singh Tatla professorgstatla@gmail.com www.eazynotes.com 1 professorgstatla@gmail.com www.eazynotes.com 2 Introduction to 8085 Introduction to 8085 Introduction to 8085 Introduction to 8085 It has three advanced The advanced versions consume 20% less versions: power supply. ◦ 8085 AH ◦ 8085 AH2 The clock frequencies ◦ 8085 AH1 of 8085 are: ◦ 8085 A 3 MHz These advanced ◦ 8085 AH 3 MHz versions are designed ◦ 8085 AH2 5 MHz using HMOS ◦ 8085 AH1 6 MHz technology. Gursharan Singh Tatla Gursharan Singh Tatla www.eazynotes.com 3 www.eazynotes.com 4 professorgstatla@gmail.com professorgstatla@gmail.com X X 1 & X & X 2 Pin Diagram of 8085 Pin Diagram of 8085 Pin 1 and Pin 2 (Input) Pin 1 and Pin 2 (Input) These are also called Crystal Input Pins. 8085 can generate clock signals internally. To generate clock signals internally, 8085 requires external inputs from X 1 and X 2 . Gursharan Singh Tatla Gursharan Singh Tatla professorgstatla@gmail.com www.eazynotes.com 5 professorgstatla@gmail.com www.eazynotes.com 6 1

8/26/2010 RESET IN and RESET OUT RESET IN and RESET OUT RESET IN and RESET OUT RESET IN and RESET OUT Pin 36 (Input) and Pin 3 (Output) Pin 36 (Input) and Pin 3 (Output) Pin 36 (Input) and Pin 3 (Output) Pin 36 (Input) and Pin 3 (Output) RESET IN : Resetting the microprocessor means: ◦ It is used to reset the microprocessor. ◦ Clearing the PC and IR. ◦ Disabling all interrupts ◦ It is active low signal. (except TRAP). ◦ Disabling the SOD pin. ◦ When the signal on this ◦ All the buses (data, pin is low for at least 3 address, control) are tri- clocking cycles, it stated . forces the ◦ Gives HIGH output to microprocessor to reset RESET OUT pin. itself. Gursharan Singh Tatla Gursharan Singh Tatla professorgstatla@gmail.com www.eazynotes.com 7 professorgstatla@gmail.com www.eazynotes.com 8 RESET IN and RESET OUT RESET IN and RESET OUT SID and SOD SID and SOD Pin 36 (Input) and Pin 3 (Output) Pin 36 (Input) and Pin 3 (Output) Pin 4 (Input) and Pin 5 (Output) Pin 4 (Input) and Pin 5 (Output) SID (Serial Input RESET OUT: Data): ◦ It is used to reset the peripheral devices and other ICs on the circuit. o It takes 1 bit input from serial port of 8085. ◦ It is an output signal. o Stores the bit at the 8 th ◦ It is an active high signal. position (MSB) of the Accumulator. ◦ The output on this pin goes high whenever RESET IN is given low signal. o RIM (Read Interrupt Mask) instruction is ◦ The output remains high as used to transfer the bit. long as RESET IN is kept low. Gursharan Singh Tatla Gursharan Singh Tatla www.eazynotes.com 9 www.eazynotes.com 10 professorgstatla@gmail.com professorgstatla@gmail.com SID and SOD SID and SOD Interrupt Pins Interrupt Pins Pin 4 (Input) and Pin 5 (Output) Pin 4 (Input) and Pin 5 (Output) SOD (Serial Output Interrupt: Data): • It means interrupting the normal execution of the microprocessor. o It takes 1 bit from Accumulator to serial port • When microprocessor receives interrupt signal, it of 8085. discontinues whatever it was executing. o Takes the bit from the 8 th • It starts executing new program indicated by the interrupt signal. position (MSB) of the Accumulator. • Interrupt signals are generated by external peripheral devices. o SIM (Set Interrupt Mask) instruction is used to • After execution of the new program, microprocessor goes transfer the bit. back to the previous program. Gursharan Singh Tatla Gursharan Singh Tatla professorgstatla@gmail.com www.eazynotes.com 11 professorgstatla@gmail.com www.eazynotes.com 12 2

8/26/2010 Sequence of Steps Whenever There Sequence of Steps Whenever There Five Hardware Interrupts in 8085 Five Hardware Interrupts in 8085 is an Interrupt is an Interrupt Microprocessor completes execution of current TRAP instruction of the program. PC contents are stored in stack. RST 7.5 PC is loaded with address of the new program. RST 6.5 After executing the new program, the microprocessor returns back to the previous RST 5.5 program. It goes to the previous program by reading the INTR top value of stack. Gursharan Singh Tatla Gursharan Singh Tatla professorgstatla@gmail.com www.eazynotes.com 13 professorgstatla@gmail.com www.eazynotes.com 14 Classification of Interrupts Classification of Interrupts Maskable Interrupts Maskable Interrupts Maskable and Non-Maskable Maskable interrupts are those interrupts which can be enabled or disabled . Vectored and Non-Vectored Enabling and Disabling is done by Edge Triggered and Level Triggered software instructions. Priority Based Interrupts Gursharan Singh Tatla Gursharan Singh Tatla www.eazynotes.com 15 www.eazynotes.com 16 professorgstatla@gmail.com professorgstatla@gmail.com Maskable Interrupts Maskable Interrupts Non Non- -Maskable Interrupts Maskable Interrupts List of Maskable Interrupts: The interrupts which are always in enabled mode are called non- maskable interrupts. • RST 7.5 • RST 6.5 These interrupts can never be disabled by any software instruction. • RST 5.5 TRAP is a non-maskable interrupt. • INTR Gursharan Singh Tatla Gursharan Singh Tatla professorgstatla@gmail.com www.eazynotes.com 17 professorgstatla@gmail.com www.eazynotes.com 18 3

8/26/2010 Vectored Interrupts Vectored Interrupts Vectored Interrupts Vectored Interrupts The interrupts which have fixed List of vectored interrupts: memory location for transfer of control from normal execution. • RST 7.5 • RST 6.5 Each vectored interrupt points to the particular location in memory. • RST 5.5 • TRAP Gursharan Singh Tatla Gursharan Singh Tatla professorgstatla@gmail.com www.eazynotes.com 19 professorgstatla@gmail.com www.eazynotes.com 20 Vectored Interrupts Vectored Interrupts Non Non- -Vectored Interrupts Vectored Interrupts The addresses to which program The interrupts which don't have fixed control goes: memory location for transfer of control from normal execution. Name Vectored Address RST 7.5 003C H (7.5 x 0008 H) RST 6.5 0034 H (6.5 x 0008 H) The address of the memory location RST 5.5 002C H (5.5 x 0008 H) is sent along with the interrupt. TRAP 0024 H (4.5 x 0008 H) Absolute address is calculated by INTR is a non-vectored interrupt. multiplying the RST value with 0008 H. Gursharan Singh Tatla Gursharan Singh Tatla www.eazynotes.com 21 www.eazynotes.com 22 professorgstatla@gmail.com professorgstatla@gmail.com Edge Triggered Interrupts Edge Triggered Interrupts Level Triggered Interrupts Level Triggered Interrupts The interrupts which are triggered at The interrupts which are triggered at high or low level are called level leading or trailing edge are called triggered interrupts. edge triggered interrupts. RST 6.5 RST 7.5 is an edge triggered RST 5.5 interrupt. INTR It is triggered during the leading TRAP is edge and level triggered interrupt. (positive) edge. Gursharan Singh Tatla Gursharan Singh Tatla professorgstatla@gmail.com www.eazynotes.com 23 professorgstatla@gmail.com www.eazynotes.com 24 4

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.