If you cannot read the line above, consider moving closer to the - PDF document

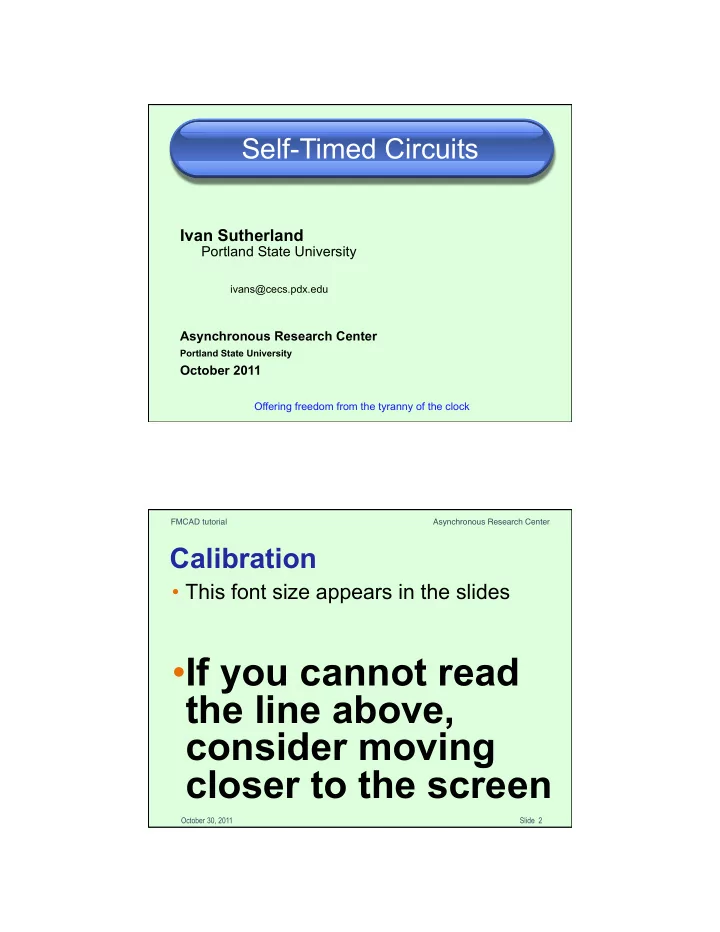

10/28/11 Self-Timed Circuits Ivan Sutherland Portland State University ivans@cecs.pdx.edu Asynchronous Research Center Portland State University October 2011 Offering freedom from the tyranny of the clock FMCAD tutorial Asynchronous Research

10/28/11 Self-Timed Circuits Ivan Sutherland Portland State University ivans@cecs.pdx.edu Asynchronous Research Center Portland State University October 2011 Offering freedom from the tyranny of the clock FMCAD tutorial Asynchronous Research Center Calibration • This font size appears in the slides • If you cannot read the line above, consider moving closer to the screen October 30, 2011 Slide 2 Fleet, Infinity & Marina 1

10/28/11 FMCAD tutorial Asynchronous Research Center About the ARC at Portland State • People > Marly Roncken (ex Philips & Intel) now PSU – CS Dept. > Ivan Sutherland (ex Sun) now PSU – ECE Dept. > Willem Mallon (ex Philips & NXP) now PSU – CS Dept. • Sponsorship > College of Engineering, PSU > Oracle > DARPA > Seeking additional sponsors October 30, 2011 Slide 3 FMCAD tutorial Asynchronous Research Center Outline • Kinetic Learning Activity (KLA) • Pipelines • Control protocols • Performance & Logical Effort • Data formats • Gate models > semi modular versus inertial delay October 30, 2011 Slide 4 Fleet, Infinity & Marina 2

10/28/11 FMCAD tutorial Asynchronous Research Center KLA rules • Predecessor and successor • Use only one hand • Pred has object AND you don’t • Take from predecessor • NEVER PUT to successor October 30, 2011 Slide 5 FMCAD tutorial Asynchronous Research Center Pipeline action • Conditions for action > predecessor proffers data > successor has space • Three part atomic action: > copy data > make successor FULL > make predecessor EMPTY October 30, 2011 Slide 6 Fleet, Infinity & Marina 3

10/28/11 FMCAD tutorial Asynchronous Research Center Pipeline is: • Logic stage “L” • Wires “w” • w L w L w L w L w L w L w • Wires may hold data (or not) October 30, 2011 Slide 7 FMCAD tutorial Asynchronous Research Center Control protocols • Single wire (GasP) > HI = data valid = FULL • Two wires – four phase > request HI = data valid > acknowledge HI = data accepted • Two wires – two phase NRZ > differ = data valid = FULL > double data rate (DDR) October 30, 2011 Slide 8 Fleet, Infinity & Marina 4

10/28/11 FMCAD tutorial Asynchronous Research Center 6-4 GasP circuit • Single control wire plus data > HI is FULL convention > bundled data > control wire is bidirectional • Least logical effort => fastest > forward latency = 6 > reverse latency = 4 • Normally opaque data latches October 30, 2011 Slide 9 FMCAD tutorial Asynchronous Research Center GasP circuit diagram October 30, 2011 Slide 10 Fleet, Infinity & Marina 5

10/28/11 FMCAD tutorial Asynchronous Research Center Charlie box • Two wires between stages > differ = FULL > bundled data > acknowledge after capture • Fast in forward direction > forward = 2 via one latch > reverse = 4 via XOR + latch • Normally transparent data latches October 30, 2011 Slide 11 FMCAD tutorial Asynchronous Research Center Charlie box circuit diagram October 30, 2011 Slide 12 Fleet, Infinity & Marina 6

10/28/11 FMCAD tutorial Asynchronous Research Center Pipeline essentials • One AND function > pred FULL and succ EMPTY • Data captured in latches or flip flops • Some relative timing assumptions • Compare with source clocking October 30, 2011 Slide 13 FMCAD tutorial Asynchronous Research Center Source and sink clocking • Source clocking > clock moves forward with data • Sink clocking > clock moves back with space October 30, 2011 Slide 14 Fleet, Infinity & Marina 7

10/28/11 FMCAD tutorial Asynchronous Research Center Canopy graph • Throughput versus occupancy > throughput in items/time: GDI/s > occupancy in items/length • Maximum throughput • Elastic = variable occupancy > can insert if not full > can withdraw if not empty October 30, 2011 Slide 15 FMCAD tutorial Asynchronous Research Center Throughput vs Occupancy for ring of 11 stages October 30, 2011 Slide 16 Fleet, Infinity & Marina 8

10/28/11 FMCAD tutorial Asynchronous Research Center Infinity test Demand Merge M in0 out M F F F in1 I I I F F F O O O Data-directed Branch out0 in B B out1 October 30, 2011 Slide 17 FMCAD tutorial Asynchronous Research Center Infinity: Throughput vs Occupancy October 30, 2011 Slide 18 Fleet, Infinity & Marina 9

10/28/11 FMCAD tutorial Asynchronous Research Center Mutual exclusion • Two events at “same” time > which choice doesn’t matter > but choice must be clean • Flip flop can hang metastable > exit is Poisson distributed > may take a long time, but rarely will • Asynchronous system can wait October 30, 2011 Slide 19 FMCAD tutorial Asynchronous Research Center Continental divide October 30, 2011 Slide 20 Fleet, Infinity & Marina 10

10/28/11 FMCAD tutorial Asynchronous Research Center Mutual exclusion (Seitz) October 30, 2011 Slide 21 FMCAD tutorial Asynchronous Research Center Blend control with data • Two wires per bit (like domino) > LO + LO = invalid > LO + HI = one > HI + LO = zero • Plus one acknowledge wire > four-phase, NRZ, or single track > Fulcrum – four phase 18 FO4 cycle October 30, 2011 Slide 22 Fleet, Infinity & Marina 11

10/28/11 FMCAD tutorial Asynchronous Research Center Validation issues • Loops in each pipeline stage > interlocked with AND functions > may not have latches or flip flops > hard to verify with conventional tools • Slope and delay model > slope converges quickly > delay converges if slope is known > not available in conventional tools October 30, 2011 Slide 23 FMCAD tutorial Asynchronous Research Center Global state • Is an unnecessary fiction • Handshakes isolate local actions • Transactions are what matters • Pipelines are easy to think about > local transactions tell all > avoid state explosion > painless concurrency October 30, 2011 Slide 24 Fleet, Infinity & Marina 12

10/28/11 FMCAD tutorial Asynchronous Research Center Fork and join pipes • Fork sends same data both ways • Join combines two data inputs • Fork and joint parallel pipelines > storage capacity of the shorter > latency of the slower > slack matching avoids • excess storage • excess latency October 30, 2011 Slide 25 FMCAD tutorial Asynchronous Research Center Unique verification tasks • Combinational Loops • Slack matching • Working with local state • Deadlock > wormhole networks OK if no loops > other cases? October 30, 2011 Slide 26 Fleet, Infinity & Marina 13

10/28/11 FMCAD tutorial Asynchronous Research Center Discussion October 30, 2011 Slide 27 Fleet, Infinity & Marina 14

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.