HARDROC 3 for SDHCAL 02 / 02 / 2014 - HGC4ILD Workshop OMEGA - PowerPoint PPT Presentation

HARDROC 3 for SDHCAL 02 / 02 / 2014 - HGC4ILD Workshop OMEGA microelectronics group Ecole Polytechnique CNRS/IN2P3 , Palaiseau (France) Organization for Micro-Electronics desiGn and Applications ROC chips for ILC prototypes SPIROC2 ROC

HARDROC 3 for SDHCAL 02 / 02 / 2014 - HGC4ILD Workshop OMEGA microelectronics group Ecole Polytechnique CNRS/IN2P3 , Palaiseau (France) Organization for Micro-Electronics desiGn and Applications

ROC chips for ILC prototypes SPIROC2 ROC chips for technological prototypes : to Analog HCAL (AHCAL) study the feasibility of large scale, (SiPM) industrializable modules (Eudet/Aida funded) 36 ch. 32mm² June 07, June 08, March 10, Sept 11 Requirements for electronics Large dynamic range (15 bits) Auto-trigger on ½ MIP HARDROC2 and MICROROC On chip zero suppress Semi Digital HCAL (sDHCAL) 10 8 channels (RPC, µmegas or GEMs) 64 ch. 16mm² Front-end embedded in detector Sept 06, June 08, March 10 Ultra-low power : 25µW/ch SKIROC2 ECAL (Si PIN diode) 64 ch. 70mm² March 10 2

From 2 nd generation… 2 nd generation chips for ILD Auto-trigger, analog storage and/or digitization Token-ring readout (one data line activated by each chip sequentially) Time between two bunch crossing: 337 ns Time between two bunch crossing: 337 ns Common DAQ Time between two trains: 200ms (5 Hz) Time between two trains: 200ms (5 Hz) Power pulsing : <1 % duty cycle time time Train length 2820 bunch X (950 µ s) Train length 2820 bunch X (950 µ s) 5 events 3 events 1 event 0 event 0 event Chip 0 Chip 1 Chip 2 Chip 3 Chip 4 A/D conv. A/D conv. DAQ DAQ IDLE MODE IDLE MODE Acquisition Acquisition Data bus 1ms (.5%) 1ms (.5%) .5ms (.25%) .5ms (.25%) .5ms (.25%) .5ms (.25%) 198ms (99%) 198ms (99%) 99% idle cycle 99% idle cycle 1% duty cycle 1% duty cycle Chip 0 Chip 0 A/D conv. A/D conv. DAQ DAQ IDLE MODE IDLE MODE Acquisition Acquisition Chip 1 Chip 1 A/D conv. A/D conv. IDLE IDLE DAQ DAQ IDLE MODE IDLE MODE Acquisition Acquisition Chip 2 Chip 2 A/D conv. A/D conv. IDLE IDLE IDLE MODE IDLE MODE Acquisition Acquisition Chip 3 Chip 3 A/D conv. A/D conv. IDLE IDLE IDLE MODE IDLE MODE Acquisition Acquisition Chip 4 Chip 4 A/D conv. A/D conv. IDLE IDLE DAQ DAQ IDLE MODE IDLE MODE Acquisition Acquisition 3

…To 3 rd generation 3 rd generation chips for ILD Independent channels (zero suppress) I2C link (@IPNL) for Slow Control parameters and triple voting - configuration broadcasting - geographical addressing HARDROC3: 1 st of the 3 rd generation chip to be submitted – Received in June 2013 (SiGe 0.35µm) (AIDA funded) – Die size ~30 mm 2 (6.3 x 4.7 mm 2 ) - Packaged in a QFP208 RPC cross section 1m 2 RPC [IPNL] 4

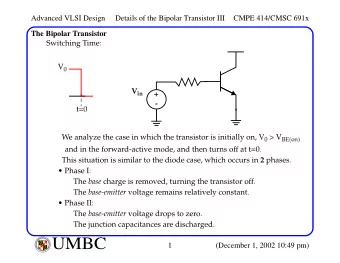

HR3: Simplified schematics 64 channels H old Read M ultiple x 64 channels with current preamplifiers Gain correction Charge output SLO W Shaper 8 b its/ch an n el + Variable Trigger less mode (auto trigger 15fC up Chj Read Gain PA Bipo lar FAST Chj_trig0 Latch D 0 to 10pC) Shaper 0 Vth 0 RS nor6 4 _0 _<j> Ctest ch<j> Discri. 2 pF Vth0: 10fC to 100fC Slow Ctrl m ask0 trigger0<j> Gain correction (max factor 2) Read Chj_trig1 Ctest_Chj Bipo lar FAST Latch D 1 Vth1 RS Shaper 1 nor6 4 _1 _<j> Discri m ask1 trigger1<j> Vth1: 100fC to 1pC 3 shapers + 3 discriminators (encoded in Read Bipo lar FAST 2 bits for readout) Chj_trig2 Latch D 2 Vth2 Shaper 2 RS nor6 4 _2 _<j> m ask2 Vth2: 1pC to10pC trigger2<j> I2C link for Slow Control trigger0 e ncod0 <j> trigger1 trigger2 ENCOD ER R AM e ncod1 <i> 8 e ve nts 1 2 B it counte r B CID Independent channels with zero trigger0<j> trigr0<j> x valid _trig0 W R_M EM <j> (1 2 + 2 ) bits suppress trigger1<j> trigr1<j> valid _trig1 1 Digital M em ory/ch trigger2<j> trigr2<j> Max 8 events / channel with 12-b time valid _trig2 stamping DIGITA L PA RT Common to the 64 channels Vth2 D AC2 Integrated clock generator: PLL 1 0 bits Vth1 D AC1 nor6 4 _0 <0 :6 3 > O R64 1 0 bits Power pulsing mode nor6 4 _1 <0 :6 3 > Vth0 D AC0 nor6 4 _2 <0 :6 3 > 5 1 0 bits

Analog Part: FSB Linearity 50% trigger efficiency (DAC units) vs Fast shaper outputs (mV) vs Qinj (fC) Qinj (fC) FSB0: 5 s noise limit= 15 fC FSB0 FSB1 FSB2 Up to 10 pC Up to 50 pC Dynamic range: 15fC - 50 pC 6

Gain correction / Scurves Qinj=100fC HR2 gain correction 50% point 50% point ± 5fC ± 25fC HR3: extracted 50% Scurves point vs Channel number Before: ± 17 DACU After: ± 8 DACU (± 6 fC) 7

New Slow Control: I2C • I2C standard protocol access (max 127 chip / line) • Possibility to broadcast a default configuration to all the chips • Read and write access to a specific chip with its geographical address • Triple voting for each parameter (redundancy) • Read back of control bit (even if the chip is running / copy) Master Slave Slave Slave Slave 1 2 3 x Clock Data Write frame: S Slave address W A Reg address A data A P Read frame: S Slave address W A Reg address A P S Slave address R A data A P 8

I2C measurements - I2C Write acces : Chip number (ID): 0xE2 / Reg @: 0x73 / WrData: 0x83 - I2C Read acces : Chip number (ID): 0xE2 / Reg @: 0x73 9

PLL measurements 2 clocks are needed to start the chip Slow Clock (1-10 MHz) related to the beam train (for Time stamping and data readout) Fast clock (40-50MHz) for internal the state 5MHz 40 MHz machines A PLL (clock multiplier) has been designed to generate the fast clock Multiplication factor is (N+1) / N is a SC parameter (1 to 31) Full chain tested using PLL PowerOnD Duty Cycle in % vs OutFreq in MHz T lock = 260 µs 50 Freq input fixed @ 5MHz 49 Duty Cycle in % 48 Out_PLL 47 46 45 1 10 20 30 40 Output frequency in MHz 0

Zero suppress: Memory mapping • Chip ID is the first to be outputted during readout (MSB first) 0 B C ID c hn 63 : 12 bits E 1 E 0 P 576 B C ID + C ha rge of C H 63 : m a x 8 w ords E 1 E 0 B C ID c hn 63 : 12 bits P 0 • MSB of each word indicates type of data: 0 B C ID c hn 62 : 12 bits E 1 E 0 P B C ID + C ha rge – “1”: g eneral data (Hit ch number and number of of C H 62 : m a x 8 w ords events) B C ID c hn 62 : 12 bits E 1 E 0 P 0 – “0”: BCID + encoded data R E A D (re a d o u t) • A parity bit/word B C ID c hn 1 : 12 bits P 0 E 1 E 0 B C ID + C ha rge of C H 1 : m a x 8 w ords • Up to 9232 bits (577x16) during readout E 1 E 0 0 B C ID c hn 1 : 12 bits P 0 B C ID c hn 0 : 12 bits E 1 E 0 P B C ID + C ha rge of C H 0 : m a x 8 w ords • Example of number of bits during B C ID c hn 0 : 12 bits E 1 E 0 P 0 readout: C hn # (6 bit) # e vt 4b 0 0 0 P 1 0 HR2 HR3 G e ne ra l da ta : m a x 64 w ords C hn # (6 bit) # e vt 4b 0 0 0 P 1 0 1 chn hit 160 48 0 0 0 0 0 0 7-bit C hipID P 1 1 0 8 chn hit 1280 272 15 7 0 4 chn hit @ same time 160 144 10 chn hit @ same time 160 336 11

Zero suppress: Tests • Zero suppress (only hit channels are readout): test OK Signal injected ch 20 and ch 43 • Roll mode SC : test OK If RollMode = “0” Backward compatibility with 2Gen ROC chips behavior – • Only the N first events are stored If RollMode = “1” 3Gen ROC chips behaviour – • Use the circular memory mode • Only the N last events are stored • “Noisy Evt ” SC: 64 triggers => Noisy event => no data stored : test OK • “ARCID” SC (Always Read Chip ID): test OK If ARCID = 0 Backward compatibility: No event No readout – 12 If ARCID= 1 New behavior: No event Read CHIP ID –

Power pulsing in HR chips Power pulsing: Bandgap + ref Voltages + master I: switched ON/OFF Shut down bias currents with vdd always ON • Compared to HR2, HR3 power consumption is higher due to: – The extended dynamic range (from 15pC to 50pC) – The integration of the zero suppress algorithm PWR ON • If the PLL is used, the power consumption is increased by 25 µs 3% (due to the PLL VCO) HR3 with LVDS HR2 with LVDS HR2 Power supply (5M + 40M) (5M + 40M) Trigger µW / channel µW / channel PowerOnA (Analog) 1650 1325 Only PowerOnDAC 55 50 DAC output (Vth) Only PowerOn D 725 50 Power-On-All 2430 1425 1 Power-On-All 12,2 7,5 3 @ 0,5% duty cycle

Power pulsing: Testbeam HR2 1m 2 RPC [IPNL] – 144 ASICS – SDHCAL technological proto with up to 5 0 layers (7200 HR2 chips) built in 2010-2011. – Scalable readout scheme successfully tested – Complete system in TB with 460 000 channels , AUTOTRIGGER mode and power pulsing (5%) 1 m 3 RPC detector, 40 layers 370 000 channels Vth0 Vth1 Vth2 @IPNL Lyon 1 4

Summary and next steps Good analog performances Dynamic range extended up to 50 pC Circuit is able to work with only 1 external clock (thanks to PLL) New I2C tested successfully New digital features validated on testboard Zero suppress, roll mode, ARCID mode and Noisy event mode External trigger available to be able to check the status of each channel Next steps Production run (HR3 + 11 others chips) will be submitted mid-February 2015 2-3m long RPC chambers to be built and equipped with HR3 in 2015 Moving SPIROC / SKIROC to 3 rd generation Much more complicated due to internal ADC / TDC / SCA management Integration and tests of HR3 on the 2-3m long RPC will be very helpful 15

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.