GraVF: GraVF: A Vertex-Centric A Vertex-Centric Graph Processing - PowerPoint PPT Presentation

GraVF: GraVF: A Vertex-Centric A Vertex-Centric Graph Processing Graph Processing Framework Framework on FPGA on FPGA Nina Engelhardt August 31, 2016 Graphs and Graph Traversal Algorithms 1 Vertex-centric Programming Model: From POV of

GraVF: GraVF: A Vertex-Centric A Vertex-Centric Graph Processing Graph Processing Framework Framework on FPGA on FPGA Nina Engelhardt August 31, 2016

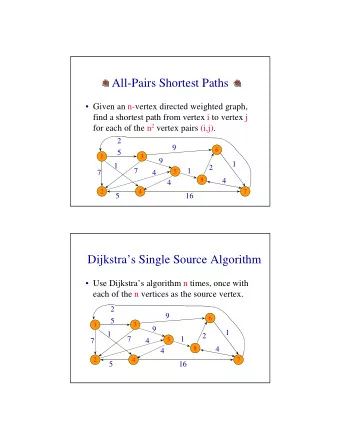

Graphs and Graph Traversal Algorithms 1 Vertex-centric Programming Model: From POV of an individual vertex Receive messages from neighbors, calculate, send messages to neighbors Global barrier after each iteration 2 / 9

Synchronous Vertex-centric Programming Model Advantages: naturally distributed only very short kernel to write Challenges: barrier means stragglers can unduly delay whole computation have to store all messages from one superstep to the next → Floating barrier [1]: PE broadcasts barrier message when it finishes superstep, allowing overlapping of supersteps 3 / 9

Architecture modifications ... PE PE PE PE Apply Scatter ... PE PE PE update Apply Scatter queue Kernel Kernel ... ... ... ... Vertex Edge Storage Storage ... PE PE PE Split Vertex Kernel in 2 phases: Apply and Scatter Everything is pipelined: free to move registers 4 / 9

Barrier Synchronization PE0 from PE 0 Arbiter from PE 1 Apply Scatter ... update queue from PE n-1 barrier message for superstep i message for superstep i+1 Apply ahead of Scatter: messages processed immediately update queue only 2 | V | entries instead of | V | 2 5 / 9

Results Weak Scaling Strong Scaling 1600 25 PR 1400 BFS Edges traversed per cycle 20 1200 x1000 Cycles 1000 15 800 10 600 400 5 200 PR BFS 0 0 1 2 4 8 16 12 4 8 16 32 Number of PEs Number of PEs 3-3.5 GTEPS: comparable to hand-implemented solutions 6 / 9

Future Work Extend communication to multiple FPGA boards Include data transfers: direct SSD access from FPGA 7 / 9

Thank you for listening 8 / 9

Works Cited I 1 Betweenness Centrality; By Claudio Rocchini, CC BY 2.5, https://commons.wikimedia.org/w/index.php?curid=1988980 Qingbo Wang, Weirong Jiang, Yinglong Xia, and V. Prasanna. A message-passing multi-softcore architecture on FPGA for breadth-first search. In Field-Programmable Technology (FPT), 2010 International Conference on , pages 70–77, Dec 2010. 9 / 9

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.