Global Trigger Processor Emulator Dr. Katerina Zachariadou Athens - PowerPoint PPT Presentation

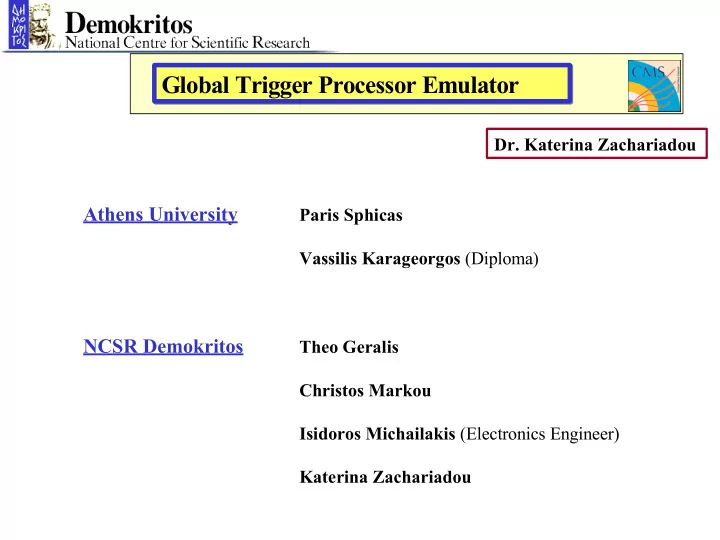

Global Trigger Processor Emulator Dr. Katerina Zachariadou Athens University Paris Sphicas Vassilis Karageorgos (Diploma) NCSR Demokritos Theo Geralis Christos Markou Isidoros Michailakis (Electronics Engineer) Katerina Zachariadou Global

Global Trigger Processor Emulator Dr. Katerina Zachariadou Athens University Paris Sphicas Vassilis Karageorgos (Diploma) NCSR Demokritos Theo Geralis Christos Markou Isidoros Michailakis (Electronics Engineer) Katerina Zachariadou

Global Trigger Processor Timing, Trigger & Control RTP TPG FES optical network LV1 TTC FED BackPressure GTP TTS FRL GTP BackPressure A RCN RU 1 V L EVM BCN BDN BU

TTC Global Trigger Emulator GTP TTS Tasks: Generate Level-1 triggers (according to trigger rules). EVM Sent triggers to T iming T rigger C ontrol system Generate Event Number, BX counts and Trigger record data to be sent to the Event Manager (via S-Link64) Receive T rigger T hrottling S ystem levels (Ready, Busy, Error)

GTP-EVM-TTS simulation Vassilis Karageorgos University of Athens Global Trigger Processor Diploma work Running on PC#1 Intercommunication between programs via sockets over TCP/IP Trigger Throttling System Running on PC#3 Event Manager Running on PC#2

Hardware components (final) TTC-ex TTC-vi FEDs VME TTS PC#3: Wind. 2000 1GB, 2.6GHz L V Quartus + PCI-MXI2-VME 1 A DK1: c c FPGA code G3 PC#1 : Linux OS S-LINK64 Control VME G3 Control G3 PCIbus GTP emulation PC#2: Linux OS PCIbus EVM emulation PIII 512MB,550MHz

GENERIC-III , S-LIN64 B E D A C F A. FPGA (APEX –Altera 200K usable logic gates) B. 32 MB SDRAM (133Mhz) C. 1 MB Flash D. S_Link64 connectors (data transmission) E. User connectors F. PCI interface for 32b/64b @33/66MHz S-LINK64

S-LIN64 Data link to connect front-end to readout at any stage in a dataflow environment Data movement,error detection, return channel for flow control CMC receiver card: CMC transmitter card: Converts LVDS signals to S-LINK64 signals Converts S-LINK64 signals to LVDS format On-board FIFO(32Kbytes) buffers incoming data

Hardware components (Actual) TTC-ex TTC-vi FEDs VME Dig. Oscilloscope TTS PC#3: Wind. 2000 HP54615B For hardware tests PIV 250MB, 800MHZ LV1Acc Quartus + PCI-MXI2-VME DK1: PC#1: Linux OS FPGA code G3 Labview 6.1/RUlib Control PCI bus S-LINK64 Control G3 G3 LV1Acc PCIbus GTP emulation PC#2: PCIbus EVM emulation Linux OS

GTP emulator schematic VHDL, AHDL DK1.1 Celoxica design software In Handel-C Quartus 2.2-Altera software PCI control GTP SDRAM control emulation SLINK-64 control OS: Linux OS: WindowsXX PCI bus PC Parallel port with a byte-blaster

PCI control PCI Controller: •PCI communication (Dominique Gigi-CERN) •Registers for Control, Status, Error, Reset operations (Isidoros Michailakis)

GTP- transmitter S-LINK64 GTP PCI control Command -transmitter CONTROL MEM_FULL S-LINK64 WRITE_MEM (Back_Pressure) GTP Local FIFO DATA[63..0] MEM_FULL DATA[63..0] S-LINK64

EVM-receiver S-LINK64 PCI control Command CONTROL Local FIFO DATA[63..0] DATA[63..0] S-LINK64

S-LINK64 control S-LINK64 Controller (by Isidoros) Read local fifo Transfer data transmitter PCI BackPressure

GTP- part Lemo Output LV1A bxn BX_gen BX Bx_Rndm evn Write_evm S-LINK64 BackPressure FIFO_full (Backpressure) Local FIFO DATA[63..0] GTP_to_EVM_data (evn[31:12]+bxn[11:0])

BX generator module DK1 module that generates the LHC proton beam structure (40.8MHz) 3564 bunches = {[(72b +8e)x3+30e]x2+[(72b+8e)x4+31e]}x3 + {[(72b+8e)x3+30e]x3+81e} Clock = 80 MHz (for tests used the PCI clock @33MHz ) • BX is created as in LHC Simulator output: • LV1Acc occurs only on full bunches

BX_Rndm module Lemo Output LV1A bxn BX_gen BX Bx_Rndm evn Write_evm S-LINK64 BackPressure FIFO_full (Backpressure) Local FIFO DATA[63..0] GTP_to_EVM_data (evn[31:12]+bxn[11:0])

BX_rndm module BX_rndm module tasks: Random number generator (22 bits long Period = 4x10 6 events) At non empty BXs generates LV1Accept signals randomly at a frequency of 100KHz (or at any frequency [4Hz, 100KHz]) Associates a BX Number [0,3563] and an Event Number

CLK BX_rndm module BX BXN DK1 Handel-C code Edif file LV1-A rate Symbol for BX_rndm in Quartus EVN LV1A

LV1A on the scope For this test LV1A @ 50KHz

Write_Evm module Lemo Output LV1A bxn BX_gen BX Bx_Rndm evn Write_Evm S-LINK64 BackPressure FIFO_full (Backpressure) Local FIFO DATA[63..0] GTP_to_EVM_data (evn[31:12]+bxn[11:0])

Write_Evm module BX number 1. Prepares data to be sent to the local FIFO event number 2. Checks the FIFO full flag (BackPressure) 3. Writes data in FIFO if not full. If the local FIFO is full the data are lost. FIFO DATA[63..0] full WEN

Write_Evm module timing

Local FIFO Lemo Output LV1A bxn BX_gen BX Bx_Rndm evn Write_evm S-LINK64 BackPressure FIFO_full (Backpressure) Local FIFO DATA[63..0] GTP_to_EVM_data (evn[31:12]+bxn[11:0])

Local FIFO LOCAL FIFO (by Isidoros) FIFO : 1024 x 64 bits words, rw MUX for accessing the Control, Status etc registers

GTP EVM via SLINK-64 tests GTP vi running on PC#1: Generate Level1 Accept triggers at user Receiver vi running on PC#2: defined frequency Get data Send data to the Event Manager

Summary Dig. Oscill Quartus + DK1: TTC FPGA code LV1A Control TTS GTP G3+VME SLINK-64 EVM GTP EVM GTP emulator conceptual design LHC beam structure, LV1A signal , EVN, BXN SLINK-64 control GTP EVM via SLINK-64

Future Plans TTC Further tests of the design+integration tests of all components in a complete GTP emulator : LV1A FED TTS BackPressure signals from TTS & EVM Generate Level-1 triggers according to trigger rules GTP Implement Trigger Summary Block BackPressure EVM Standard (FEDkit) receiver TTS signals Ready Busy inhibit set of Trigger Rules : Synchr. failure inhibit + synchr command via TTC to FED’s “No more than N Level-1 Triggers in (reset counters) a given time interval”. Overflow reduction of trigger rate

RECEIVER GTP emulator G3 SLINK to the Byteblaster scope

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.