Fluctuation Smoothing Production Control at IBMs 200mm Wafer - PowerPoint PPT Presentation

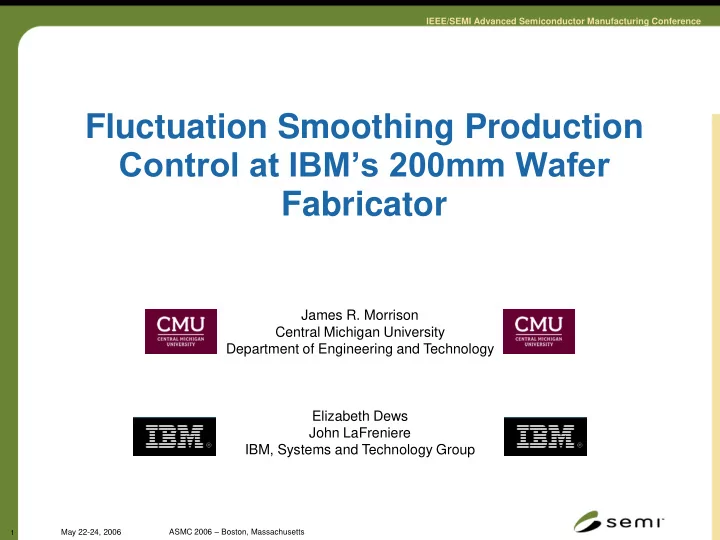

IEEE/SEMI Advanced Semiconductor Manufacturing Conference Fluctuation Smoothing Production Control at IBMs 200mm Wafer Fabricator James R. Morrison Central Michigan University Department of Engineering and Technology Elizabeth Dews John

IEEE/SEMI Advanced Semiconductor Manufacturing Conference Fluctuation Smoothing Production Control at IBM’s 200mm Wafer Fabricator James R. Morrison Central Michigan University Department of Engineering and Technology Elizabeth Dews John LaFreniere IBM, Systems and Technology Group ASMC 2006 – Boston, Massachusetts May 22-24, 2006 1

IEEE/SEMI Advanced Semiconductor Manufacturing Conference Presentation Overview • IBM’s 200mm wafer fabricator • Competing control methodologies • Multiple cycle time FSVCT policy • Estimation of cycle times • Implementation challenges • Performance evaluation • Concluding remarks ASMC 2006 – Boston, Massachusetts May 22-24, 2006 2

IEEE/SEMI Advanced Semiconductor Manufacturing Conference IBM’s 200mm Fabricator Lots enter • Reentrant process flow – 30 or more visits to certain tool groups Tool Group 1 • Products Tool Group 5 Tool Group 2 – More than 30 different semiconductor Tool Group 6 Tool Group 3 technologies – Dozens of products within each Tool Group 4 technology • Up to 400 stages of processing Tool Group 7 • Over 200 distinct tool groups Tool Group 8 • Production capacity about 1000 Tool Group 12 Tool Group 9 wafers/day Tool Group 10 • Cycle time about 40 to 60 days with Tool Group 11 production time around 20 days ASMC 2006 – Boston, Massachusetts May 22-24, 2006 3

IEEE/SEMI Advanced Semiconductor Manufacturing Conference Competing Control Methodologies Objective: Minimize overall cycle time and meet due date targets Increasing Implementation Effort Variant of continuous flow manufacturing Roughly Increasing Optimality Existing policy Produce fixed amount per day Loading changes require updates Prioritization to implement preference Critical ratio (CR) KANBAN Due date based policy Finite queue lengths Considered easy to implement Fluctuation smoothing for the variation of cycle time (FSVCT) Reduce variation of cycle time by driving all lots to the same average CT FSVCT and related policies successful in many simulations/implementations Deterministic finite – horizon Fluid limit inspired policies mathematical programming Cycle time optimization Requires optimization and model ILOG software product Requires detailed data and setup ASMC 2006 – Boston, Massachusetts May 22-24, 2006 4

IEEE/SEMI Advanced Semiconductor Manufacturing Conference Multiple Cycle Time FSVCT Policy • First “law” of queueing: Variation leads to cycle time – At 95% loading: D/D/1 normalized CT = 1 – At 95% loading: M/D/1 queue normalized CT = 10.5 – Fluctuation Smoothing for the Variation of Cycle Time (FSVCT) Policy [Lu-Ramaswamy-Kumar, 1994] • Cycle time expectations for a group of lots g – Common route, common expected pace – CT g = total expected cycle time h g ( l ) = expected remaining cycle time for lot l – Expected total cycle time • MCT – FSVCT Slack: CT h NOR Slack ( l ) : [ Time in fab ( l )] g CT g – Serve lot l with the least slack Drives lots from g to same cycle time ASMC 2006 – Boston, Massachusetts May 22-24, 2006 5

IEEE/SEMI Advanced Semiconductor Manufacturing Conference Multiple Cycle Time FSVCT Policy Expected total • MCT – FSVCT Slack: cycle time CT h NOR Slack ( l ) : [ Time in fab ( l )] g CT g – Serve lot l with the least slack Drives lots from g to same cycle time • Examples: Lot l 1 Lot l 2 Lot l 3 Time in Fab 10 10 20 h g ( l ) 23 17 46 CT g 30 30 60 33 27 66 - CT NOR - CT NOR - CT NOR Slack( l ) 30 30 60 = -(1.1)CT NOR = -(0.9)CT NOR = -(1.1)CT NOR ASMC 2006 – Boston, Massachusetts May 22-24, 2006 6

IEEE/SEMI Advanced Semiconductor Manufacturing Conference Estimation of Expected Cycle Times Lots enter • Fundamental parameters for MCT – Tool Group 1 FSVCT: – CT g = total expected cycle time Tool Group 5 Tool Group 2 h g ( l ) = expected remaining cycle – time for lot l Tool Group 6 Tool Group 3 Tool Group 4 • Absence of plant model combining: – Routes – Capacities Tool Group 7 – Cycle times • Tool Group 8 How to determine cycle times? – Simulation? Costly to create model Tool Group 12 Tool Group 9 and maintain – Measure and use existing CTs Tool Group 10 – Set some CTs (preferred customers) determine CT imposed on Tool Group 11 remaining lots ASMC 2006 – Boston, Massachusetts May 22-24, 2006 7

IEEE/SEMI Advanced Semiconductor Manufacturing Conference Estimation of Expected Cycle Times Little’s Law: l g = N g / CT g • • EXAMPLE: – • N g is mean number of g lots Group 1 and group 2 lots are similar – CT g is mean cycle time for a g lot Total L = 4500 lot * stages/day • • Let lots of group g require P g stages • Group 1 lots: of production – P 1 = 300 stages, N 1 = 100 lots, CT = 20 – Aggregate rate of completion of L 1 = (300)(100)/(20) = 1500 lot * stages/day – stages of production L g – = P g N g / CT g • Group 2 lots: – P 2 = 300 stages, N 2 = 400 lots, CT = ? L 2 = L – L 1 – = 3000 lot * stages/day • For groups of lots with similar = (300)(400)/CT 2 production path: – CT 2 = 40 days P N L L g g : g g c g c CT • Assuming equality holds Predict CT for g • use in MCT-FSVCT Assume holds in the face of control changes (subject to feasibility) ASMC 2006 – Boston, Massachusetts May 22-24, 2006 8

IEEE/SEMI Advanced Semiconductor Manufacturing Conference Implementation Challenges • Cycle time targets must be mutable – Management directed reprioritization of WIP – CT’ g Update: CT g Update: h g ( l ) h ’ g ( l ) – – Arrival dates must be updated: a( l ) a’( l ) Current Expected Stage Stage Initial Final Stage Stage Final Initial Current Expected Stage Stage Stage Stage – a ' ( l ) Now [ a ( l ) Now ] * [ CT ' g CT / ] g • Patience and maintenance of focus • Programming resource allocation • Operators need not follow the dictates of the policy ASMC 2006 – Boston, Massachusetts May 22-24, 2006 9

IEEE/SEMI Advanced Semiconductor Manufacturing Conference Performance Evaluation • Multiple cycle time FSVCT Cycle Time Performance Curves for – Manufacturing Systems Implementation date: April 2005 5 4.5 • Performance evaluation challenges 4 – Normalized Cycle Time No fabricator cycle time model 3.5 – Ever changing load and mix 3 – Loading reduction prior and subsequent to implementation 2.5 – Queueing time consists of roughly 2 30% of the cycle time 1.5 1 0.5 • Alternative considerations 0 – Cycle time variation reduction 0 0.2 0.4 0.6 0.8 1 – Variation as a function of cycle time Loading (Utilization) – Throughput as a function of WIP M/M/1 - Cycle Time M/D/1 - Cycle Time Practical System - Approximate Cycle Time ASMC 2006 – Boston, Massachusetts May 22-24, 2006 10

IEEE/SEMI Advanced Semiconductor Manufacturing Conference Standard Deviation Performance • For the same cycle time: M/M/1 has greater standard deviation of cycle time than M/D/1 • Does our change in control policy shift the standard deviation performance of the fabricator? M/D/1 Standard Deviation is Less than M/M/1 Standard Deviation at Constant Cycle Time 5 Standard Deviation of Cycle Time 4 3 2 1 0 1 2 3 4 5 Normalized Cycle Time M/M/1-STD M/D/1-STD ASMC 2006 – Boston, Massachusetts May 22-24, 2006 11

IEEE/SEMI Advanced Semiconductor Manufacturing Conference Standard Deviation Performance • Reduction in fabricator loading • Queueing time about 30% of the cycle time • Reduction in standard deviation of cycle time Monthly Standard Deviation of Cycle Time: Before and After Implementation of FSVCT Standard Deviation of Normalized Cycle Time Normalized Cycle Time (X Factor) After FSVCT - Standard Deviation Before FSVCT - Standard Deviation ASMC 2006 – Boston, Massachusetts May 22-24, 2006 12

IEEE/SEMI Advanced Semiconductor Manufacturing Conference Throughput and WIP Performance • For the same fixed level of work in process (WIP): – Exponential server has less throughput than deterministic • Does our change in control policy shift the throughput performance of the fabricator? Throughput as a Function of WIP: Consequences of Randomness 1.2 Mean Throughput (Normalized) 1 0.8 0.6 To achieve 90% of maximum 0.4 throughput, 9 lots in the system 0.2 0 0 2 4 6 8 10 Lots in System Ideal Throughput Mean Throughput: Exponential Service ASMC 2006 – Boston, Massachusetts May 22-24, 2006 13

IEEE/SEMI Advanced Semiconductor Manufacturing Conference Throughput and WIP Performance • Reduction in work in process (WIP) within fabricator • Throughput and WIP reduction observed • Low loading regime (30% of cycle time due to queueing) Throughput Performance as a Function of WIP Weekly Data for IBM BTV 200mm Completed Daily (Throughput) Total Stages of Production Wafers in the Fabricator/Tool Throughput - Pre-FSVCT Estimated Ideal Throughput Throughput - Post-SVCT Post-FSVCT ASMC 2006 – Boston, Massachusetts May 22-24, 2006 14

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.