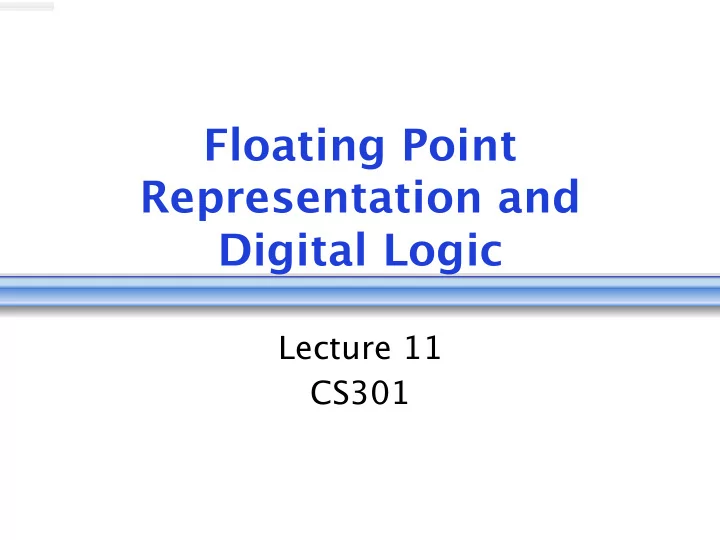

Floating Point Representation and Digital Logic Lecture 11 CS301 - PowerPoint PPT Presentation

Floating Point Representation and Digital Logic Lecture 11 CS301 Administrative Daily Review of todays lecture w Due tomorrow (10/4) at 8am Lab #3 due Friday (9/7) 1:29pm HW #5 assigned w Due Monday 10/8 at 5pm Program

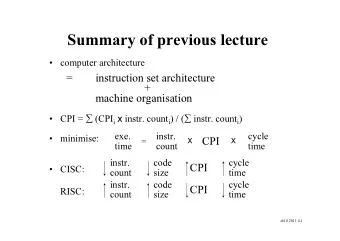

Floating Point Representation and Digital Logic Lecture 11 CS301

Administrative • Daily Review of today’s lecture w Due tomorrow (10/4) at 8am • Lab #3 due Friday (9/7) 1:29pm • HW #5 assigned w Due Monday 10/8 at 5pm • Program #1 assigned w Due Thursday, 10/18 at 11:59pm • Read Appendix C.1-C.3, C.5

Digital Logic (How do we construct a processor?)

Multi-Million Transistor Chips Intel Core i7 Extreme Edition - 731 million transistors, 263 mm^2 area

MOS Semiconductor Transistors Drain Wire Gate Wire Source Wire + + + + + + + + + e - + + + + e - n-type Si + + + Gate + + + + + + + + + e - e - e - e - e - + + + + + + + + + e - Source Drain n-type Si + + + e - + + + e - + + + e - e - Oxide + + + + + + + + + + + + + + e - e - + e - + e - + + Silicon Bulk (p-type) + + + + + + + + e - + e - + P-type silicon: Excess positive charges (electron holes) N-type silicon: Excess negative charges (electrons) Oxide: Insulator In this state, current (electrons) cannot flow between source and drain – switch is OPEN Gate: Metal pad

MOS Semiconductor Transistors Drain Wire Gate Wire +5V Source Wire + + + + + + + + + + + + + + + + + + n-type Si + + + + Gate + + + + + + + e - + + + + e - e - e - e - e - + + e - + + + + + e - e - e - e - e - e - e - e - e - + + + e - Source Drain n-type Si + + + + + + e - e - + + + e - Oxide + + + + + + + + + + + + + + + + + + Silicon Bulk (p-type) + + + + + + + + + + Place a positive charge on the gate wire (gate = +5V) The gate’s positive charge attracts negatively-charged electrons This row of electrons forms a channel connecting the Source and Drain – Current can flow – Switch is CLOSED

Transistors +5V • Transistors Pull-up pMOS w Emits 0 or 1 when on transistor or off Z w Can connect A transistors in series Pull-down nMOS or parallel to create transistor GND larger building blocks CMOS Inverter created called gates from two transistors

Digital Logic • Voltages represent values w Logically false - 0 w Logically true - 1 • Values are complements or inverses

Gates: Basic Building Blocks: • Depending on organization of transistors, different inputs give specific outputs • Basic gates equivalent to boolean operators w INVERTER or NOT, ! A A w AND, && w OR, || A • Combinational logic A • B B w Outputs based on inputs w No memory A A + B B

Truth Tables A Z NOT • Functionality fully 0 1 specified by truth 1 0 table A B Z 0 0 0 • n inputs 0 1 0 AND w n input columns 1 0 0 w 2 n input rows 1 1 1 • m outputs A B Z w m output columns 0 0 0 0 1 1 OR 1 0 1 1 1 1

Combinational Logic • Gates can be A A combined in A w Series Y w Parallel Z B • Any combination of both possible A B Y Z 0 0 1 0 0 1 1 0 1 0 0 0 1 1 0 1

Other Important Gates • NAND A B Z A 0 0 1 A B B 0 1 1 1 0 1 1 1 0 • NOR A B Z A 0 0 1 A + B B 0 1 0 1 0 0 1 1 0

Universal Gates • Any other gate can be constructed from some arrangement of universal gates w Examples: NAND / NOR • Important because frequently less expensive to design chips with “homogeneous” gates

Universal Gates (NAND) • NOT A A AA A A A 0 1 1 1 0 0

Universal Gates (NAND) • NOT A A AA A A A 0 1 1 1 0 0 • AND A B AB 0 0 0 0 1 0 1 0 0 1 1 1

Universal Gates (NAND) • NOT A A AA A A A 0 1 1 1 0 0 • AND A B AB AB A A B B 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0

Universal Gates (NAND) • OR A B A+B 0 0 0 0 1 1 1 0 1 1 1 1

Universal Gates (NAND) • OR A B A+B AB 0 0 0 0 A AB 0 1 1 1 B 1 0 1 1 1 1 1 1

For Fun: XOR A B A ⊕ B 0 0 0 0 1 1 1 0 1 1 1 0

For Fun: XOR A B A ⊕ B 0 0 0 0 1 1 1 0 1 1 1 0

Few Final Notes • Gates can have more than 2 inputs w Generally keep number small due to electrical engineering issues • Circuits that create current computers are constructed from these basic gates

Equivalent • Truth tables • Circuit • Boolean algebra expression Truth tables are great for evaluating when circuit or Boolean expression evaluate to true

Combinatorial Logic: Multiplexor Really a selector: One of the inputs is selected by the control C = (A * ~S) + (B * S) 23

Combinational Logic: Multiplexor n:1 2 n inputs 1 output MUX n control n control lines select which of 2 n inputs goes to output n possible input lines requires ceiling(log 2 n) control lines. Equivalently, n control lines with 2 n input lines.

1-bit MUX AS + BS

Combinational Logic: De-Multiplexor n:1 1 input 2 n outputs DEMUX n control n control lines select which of 2 n outputs input goes to

1 to 2 De-multiplexor

Combinational Logic: Decoder 2 n outputs n control n control lines select which of 2 n outputs set to 1

1 to 8 De-multiplexor

Combinational Logic: Encoder 2 n inputs n bit output One of 2 n inputs set to 1. Output encodes which input set to 1.

4 to 2 Encoder

8 to 3 Encoder 33

Combinational Logic • Comparator w Given 2 inputs, sets output to 1 if inputs match

Combinational Logic • Half-Adder w No carry in

Combinational Logic • Half-Adder w No carry in Carry A B Sum Out 0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 1 A ⊕ B AB

1-bit Full Adder • Three inputs: w A w B w C in • Two outputs: w Sum = (A ⊕ B) ⊕ C in w C out = AB + (A ⊕ B) C in

Ripple Carry Adder • Construct n-bit adder with n 1-bit adders • Delay is problem • Faster alternative: w Carry-lookahead adder

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.