Fast Transient Power Converter Using Switched Current Conversion - PowerPoint PPT Presentation

Fast Transient Power Converter Using Switched Current Conversion Laurence McGarry Advanced Engineering Technology Manager Hong Kong & China Astec Power A Division of Emerson Network Power. Abstract: Next generation microprocessors continue

Fast Transient Power Converter Using Switched Current Conversion Laurence McGarry Advanced Engineering Technology Manager Hong Kong & China Astec Power A Division of Emerson Network Power.

Abstract: Next generation microprocessors continue to require power supplies capable of supporting fast transient loading. Conventional approaches to solving the fast transient issue focus on the use of interleaved buck converters. This approach is fundamentally limited due to the presence of the output inductance, limiting the converter response to a load transient. This paper introduces a novel switched current converter. The converter will switch current to the load or to ground depending on the load transient requirement, providing a theoretically infinite transient response. The research investigates the practical limitations of the converter topology, using simulation to evaluate and optimize the system design. Finally, simulation models and results are presented and suggestions for further design improvements are discussed.

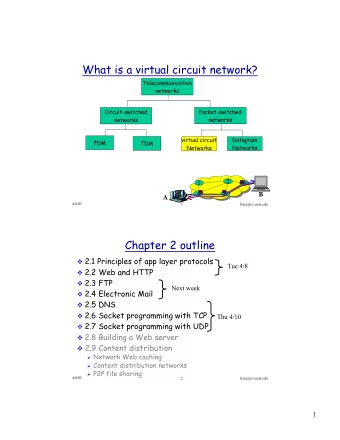

Common Industry Trends • Intel CPU requirement for VRM Intel CPU voltage and Current Roadmap Processor trends well documented : � Higher Current Requirements � Lower Voltage Processors, tighter regulation range � Higher Frequencies � Faster Transient Response

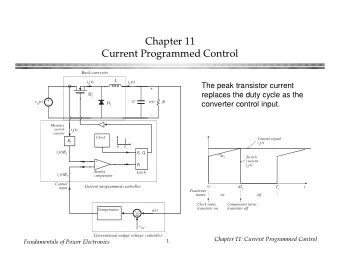

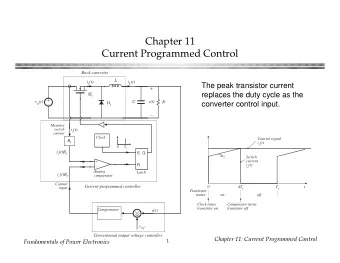

Conventional Industry Approaches � Standard approach to resolving the challenge is to use interleaved Buck converters � Response time inherently limited by the presence of the output inductor � Problem compounded by interconnect and PCB parasitics � Continued silicon integration, drive to higher frequencies and possibly an increased number of phases will continue to be a trend regardless of the architecture utilized � Switched Current Techniques offer an alternative approach � An infinite transient response possible, in theory at least 2 2 Conventional Buck Converter Volterra 300A/uS Module 369mm

Switched Current Concepts � Currents are switched to the load or to the return path � Parallel switching Current Paths are utilized � Transient can be supported in the time that it takes to turn the FET On/Off � When output current follows processor demand current, significant reduction in output capacitance can be observed � The constant current source is derived from a Buck Converter driving a matrix Transformer configuration 2

Constant Current Source � Front end Buck converter provides the constant current source � Push Pull Converter operating at 100% duty using a ‘Matrix transformer’ provides the input to the current switches at the load side � Matrix Transformer: series (primary), parallel (secondary) ferrite cells forming individual isolation for each phase � LHS source is constant current and could be remote from the end application. � RHS Switches could be co- located with the processor to reduce interconnect parasitics and enhance transient response 2

System Overview and Simulation Model � Front End Buck Converter providing constant current source � Push-Pull Converter with Matrix Transformer provides constant current parallel paths � Output Current switches; switching current to the load in response to transients or to ground � Simulation model: 3 Stage Conversion - 12V input to 1V, 100A output - 10 parallel switching paths

Constant Current Source Buck Converter � Buck Constant Current Converter � Simple Hysteretic Control Implemented 5.6u IC=10.5 DRV1s Iout � No Output Capacitance Q3 X1 L2 10k irf 7822 R8 irf 7822 � 2 level Threshold Control Ireturn 12 MAX473 10A-11A V15 Q4 3.3k 10m 1K R15 R13 � Synch Rectification is used to R14 +5Vcc reduce power loss Vref High 10k U19 Vcc IN+ R1 max961 � Switching Frequency Varies NQ IN- according to the Buck Output Q SHDN 1 U17 SET D HC74D Q GND LE voltage, reaching maximum QN RST while Voutput Buck=0.5Vin E3 +5Vcc 1 10k U18 Vcc IN+ � Voltage on the output of the R2 max961 NQ IN- Vref Low Buck is n X Vo Q SHDN E4 - Where n is the number of switches GND LE turned to the load

Constant Current Source Buck Converter(cont) Simulation Results light load Simulation Results Light load • Buck output voltage=0.5V • Output current =10.87A • Switching Duty cycle=5.55% • Switching Frequency=110kHz • Current ripple =694mA Simulation Results Full load Simulation Results Full load • Buck output voltage=11V • Output current =10.69A • Switching Duty cycle=93% • Switching Frequency=133kHz • Current ripple =760mA

Constant Current Source Buck Converter(cont) Simulation Results Dynamic load • Output voltage slew rate=46V/us • Output current =10.8A • Current ripple =828mA Simulation result on dynamic load fs vs Vo Curve Input Buck Frequency Variation L=5.6uH, ∆ I=1A • The highest frequency =518kHz 6 . 10 5 (output voltage =5.5V) 4 . 10 5 • All components are ideal fs Vo ( ) 2 . 10 5 0 0 5 10 Vo

Push Pull Converter B ranch 1 2n 2n � Fixed Duty Cycle of 50% TX 1 Q1 L5 L2 irf6603 � Leakage Inductance causes 10.5 increased voltage stress on I 1 Primary FETs 2n 2n Q2 L4 L3 irf6603 � Gate Drive Timing for Primary 4.7n 2k 4.7n 2k irf540ns C1 R1 irf540ns C3 R7 FETs and secondary Synchronous Q3 Q4 Rectification FETs is critical D1 D3 I DEA L I DEA L

Push Pull Converter – Matrix Transformer � Matrix Transformer Structure: Core Size 11.8 X 6 X 4 mm � Coupling Coefficients: Pri-Sec 0.996, Pri-Pri 0.994, Sec-Sec 0.994 � Important for the Matrix Transformer cells and SRs to be in close proximity � Staggered placement of the Matrix Cells on either side of the PCB facilitates optimum layout

Matrix Transformer Modeling Standalone With Primary Termination In The Middle 0.5mm 4.5mm Magnetising Inductance 2.07uH 2.07uH Leakage S-P 2.72nH 3.27nH 8.04nH Leakage S-S 7.11nH 7.79nH Leakage P-P 10.94nH 11.61nH Equivalent R 1.38mOhm 1.41mOhm 2.08mOhm Primary R 0.476mOhm Secondary R 0.934mOhm Magnetising Current 1.063A Core Loss 0.375W

Push Pull Converter – Drive Signal Timing Primary Gate Drive Overlapping � First, overlapping drive is considered to G1 avoid breaking current source path G2 � Two primary windings are shorted during the period of overlapping and a current gap occurs � Spike across the drain source is caused by the energy stored in leakage inductor Primary Gate Drive Non-Overlapping � Non-overlapping avoids shorting the primary winding � Spike on drain is caused by the current transient � Current gap occurs during this period as the two primary FETs are off � Non-overlapping gate drive is used. Adjusting dead time optimizes the current gap � Device capacitance is sufficient to provide current continuity during commutation

Push Pull Converter – Drive Signal Timing (cont) � Reverse Recovery of Synch Rect. for non-overlapping � Simulation waveform under 100mOhm Load. 100nS primary deadtime, 150nS leading SR delay. 60nS SR trailing edge delay. � Note reverse recover current during SR off time � The spike due to reverse recover current depends on the parasitic inductance of trace on PCB

Switched Current Converter 1m Vo Q1 I1 irf6601_1 4.7u irf6601_1 C1 Vcc 10 D2 U1 10 R3 IDEAL Q2 R2 max962 D3 OUT N1 IDEAL VSp ARB2 OUT N1 Qout_p VINp Qout_n VINn Vref1 ARB1 VSn Gnd � Output Capacitance is necessary but smaller � Voltage feedback � Current supplied to the load is determined by voltage drop on the capacitor � Delay of control loop requires a larger capacitance � ESR and ESL of Output Capacitance is critical to the step control � Gate drive timing stops current to load before short current to ground

Switched Current Converter(cont) Simulation on dynamic load = 400A/us Simulation condition: � Load current is changed from 5A to 95A (blue) � Load current slew rate = 400A/us Simulation result: � Load voltage is varied from 1.022V to 0.975V (light green) � The red line Ic is the current waveform before output capacitance � The light green line is the buck output current waveform

Switched Current Converter(cont) Simulation on dynamic load = 1000A/us Simulation condition: � Load current is changed from 5A to 95A (blue) � Load current slew rate = 1000A/us Simulation result: � Load voltage is varied from 1.022V to 0.975V (light green)

Switched Current Converter(cont) Simulation on dynamic load = 2000A/us Simulation condition: � Load current is changed from 5A to 95A (blue) � Load current slew rate = 2000A/us Simulation result: � Load voltage is varied from 1.022V to 0.975V (light green) � The Slew Rate has no obvious effect on the Output Voltage Deviation

Switched Current Converter(cont) Modeling The Interconnect: All the previous simulations include the parasitics associated with � the a representative system interconnect � The simulations do not include PCB parasitics and depend on component simulation accuracy 100p 40u R5 L1 180u 560u C1 C5 V R M Future Processor 300u 300u M odel R3 R6 current output V R M decoupling inter-connection capacitors output cap

System Measurements – Actual results � Load changed from 0-50%, 5 phases switching � Early results indicate that the 927A/uS can be achieved on rise time � Optimisation continues…..

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.