ECOC2010 Invited Paper DA and AD Converters in SiGe Technology: - PowerPoint PPT Presentation

ECOC2010 Invited Paper DA and AD Converters in SiGe Technology: Speed and Resolution for Ultra High Data Rate Applications Tobias Ellermeyer, Rolf Schmid, Anna Bielik, Jrg Rupeter and Michael Mller MICRAM Microelectronic GmbH, Bochum,

ECOC2010 Invited Paper DA and AD Converters in SiGe Technology: Speed and Resolution for Ultra High Data Rate Applications Tobias Ellermeyer, Rolf Schmid, Anna Bielik, Jörg Rupeter and Michael Möller MICRAM Microelectronic GmbH, Bochum, Germany www.micram.com SEPTEMBER 19-23, 2010 – TORINO, ITALY T. Ellermeyer et al.: DA and AD Converters in SiGe Technology.

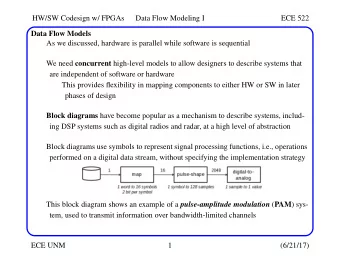

Introduction TX RX ADC DAC TIA DSP 90° DSP ADC DAC TIA Simple example w/o PolMux Simple example w/o PolMux / direct detection DA converter needed for: AD converter needed for: • Pre-Emphasis • Equalization in binary transmission • Higher Level QAM / DQPSK • Higher Level QAM / DQPSK • OFDM • OFDM • Multi-Format / Adaptive Transmitters • Multi-Format / Adaptive Receivers page 2 T. Ellermeyer et al.: DA and AD Converters in SiGe Technology. SEPTEMBER 19-23, 2010 – TORINO, ITALY

State-of-the-Art converters CMOS SiGe HBT/BiCMOS III/V HBT Phys. resolution 8 bit 6 bit D Rise/fall time (20/80) tr > 24 ps tr = 12 ps Full scale swing A 0.8 Vpp 1.6 Vpp C 8 bit 6 bit 6 bit 6 bit tr > 30 ps tr n/a tr = 30ps tr n/a 1.0 Vpp 1.0 Vpp 0.3 Vpp n/a 12 GSa/s 20 GSa/s 32 GSa/s 43 GSa/s 50 GSa/s 34 GSa/s Phys. resolution 3 bit 4 bit 6 bit 8 bit A ENOB 2.3 bit 3.2 bit 3.9 bit 5.7 bit f(ENOB) GHz 10 GHz 8 GHz 18 GHz 17 GHz D Full scale swing 1.0 Vfs 0.24 Vfs 1.2 Vfs 1.0 Vfs C 5 bit 6 bit 4 bit 3.5 bit 4 bit 3.2 bit 10 GHz 22 GHz 15 GHz 1.0 Vfs 0.28 Vfs 0.5 Vfs 10 GSa/s 20 GSa/s 30 GSa/s 40 GSa/s 56 GSa/s 24 GSa/s 35 GSa/s page 3 T. Ellermeyer et al.: DA and AD Converters in SiGe Technology. SEPTEMBER 19-23, 2010 – TORINO, ITALY

Technology Choice (ADC) T/H T/H AD C T/H AD C 0° 17 GHz (100G) >30 GHz (400G) AD C T/H T/H TIA/AGC AD C T/H T/H 90° f S /n T/H CLK/n 17 GHz (100G) 100GbE: 28/56 GSa/s; >30 GHz (400G) >4 GHz (100G) CLK 180° >7.5 GHz (400G) 17 GHz BW T/H ADC 400GbE: 56-224 GSa/s; 270° 17 GHz (100G) f S /4 28-112 GHz BW >30 GHz (400G) CLK/4 Bottleneck CMOS SiGe TIA / AGC - External IC (or add. bits instead - Integrated on ADC AGC) First T/H Stage - Bandwidth - Resolution / Droop - Driving of next stages - Clock jitter - Clock jitter AD conversion - Slow ADC cores - Fast ADC cores - Synchronization / calibration - No complex logic - Signal / Clock distribution page 4 T. Ellermeyer et al.: DA and AD Converters in SiGe Technology. SEPTEMBER 19-23, 2010 – TORINO, ITALY

Technology Choice (DAC) Interleaving of DA converter cores Single core DA converter 100G: 17 GS/s MUX DAC 100G: 34 GS/s MUX DAC AMUX 100G: 17 GS/s MUX DAC • Needs analog multiplexer (AMUX) • Significantly lower switching noise • Switching noise visible at output • Better accuracy/linearity • AMUX needs • Better device matching • High bandwidth • Good linearity • AMUX sensitive to pattern effects (e.g. through self heating) SiGe: Goal is to omit modulator driver. Max. output swing of latest SiGe devices is 0.8Vse/1.6Vdiff. page 5 T. Ellermeyer et al.: DA and AD Converters in SiGe Technology. SEPTEMBER 19-23, 2010 – TORINO, ITALY

Pros/Cons of SiGe Devices Pro‘s Con‘s • Bandwidth >25 GHz possible • Only medium complexity possible (50k BJT) • High Gain => DSP needs CMOS • High output swing • Two chips: Massive bus between CMOS • Good device matching and SiGe required • Include TIA/AGC and MZM driver Two Chip solution 3D Packaging with Through Silicon Vias (TSV) Additional benefits: • Always best digital CMOS node • Any proprietary DSP possible • DAC / ADC independent of CMOS Ref: Roger Allan in Electronic Design page 6 T. Ellermeyer et al.: DA and AD Converters in SiGe Technology. SEPTEMBER 19-23, 2010 – TORINO, ITALY

Topologies for High Speed DA-Converter Cores a) R2R Ladder J J All stages have identical devices K K Resistor matching R 2R 2R R R 2R 2R R R R R OUT n L Output impedance matching L OUT p R R R L L Timing matching D D 0 D D 1 D D 2 D D 3 0 1 2 3 L Power (much power dissipated L I 0 I 0 I 0 I 0 in internal resistors) Examples: 4-bit cores b) Weighted currents R R J J Common current summing point OUT n => better impedance matching OUT p D D 0 D D 1 D D 2 D D 3 0 1 2 3 J J less power J smaller area J I 0 I 0 I 0 I 0 8 4 2 K K Timing also critical (diff. currents in CML stages) … continued on next slide … page 7 T. Ellermeyer et al.: DA and AD Converters in SiGe Technology. SEPTEMBER 19-23, 2010 – TORINO, ITALY

Topologies for High Speed DA-Converter Cores c) Segmented DAC (continued) R R J J Strongly reduces glitches J No additional current J D D 0 D D 1 K K 0 K K 1 K K 2 0 1 0 1 2 for output stage K K K 0 1 2 L Additional logic required L Binary Equal I weighted I I currents I 0 I 0 0 0 0 D D K K K 8 4 2 2 3 2 2 1 0 2 0 0 0 0 0 0 1 0 0 1 1 0 0 1 1 1 1 1 1 1 D D 2 3 6-bit Segmented DAC 6-bit Binary weighted currents (3 LSB binary weighted / 3 MSB thermometer code) page 8 T. Ellermeyer et al.: DA and AD Converters in SiGe Technology. SEPTEMBER 19-23, 2010 – TORINO, ITALY

DAC30 Demonstrator Chip • 6 bit segmented DAC • Demonstrator with FPGA interface (24 serial lines) • 34 GSa/s • Single core • Half rate clock • Configuration register 5.07 mm 5.07 mm page 9 T. Ellermeyer et al.: DA and AD Converters in SiGe Technology. SEPTEMBER 19-23, 2010 – TORINO, ITALY

DAC30 Demonstrator Chip Integral Nonlinearity vs. Code Sampling rate dc – 34 GSa/s 0,2 0,15 Resolution 6 bit 0,1 Rise/Fall (20/80%) 12 ps 0,05 INL < 0.2 LSB INL (LSB) 0 800 mV,se -0,05 Full scale swing 1600 mV,diff 1250mVpp -0,1 1600mVpp -0,15 ENOB 5.27 1900mVpp -0,2 SFDR 46.9 dB 0 8 16 24 32 40 48 56 64 Code Total power diss. 12.5 W DAC output voltage vs. code 1000 Converter core power 0.4 W 750 Output (differential) mV 5 . 0 7 x 5 . 0 7 Die size 500 mm ² 250 I n f i n e o n Technology 0 b7hf200 540mVpp -250 0 . 4 0 x 0 . 4 3 1060mVpp Converter core size -500 mm ² 1640mVpp -750 DA core incl. last mux/ 0 . 8 0 x 1 . 3 0 1930mVpp FF mm ² -1000 0 8 16 24 32 40 48 56 64 ( ‡ 28 GSa/s, 875 MHz sine wave output, Code measured with spectrum analyser up to Nyquist page 10 T. Ellermeyer et al.: DA and AD Converters in SiGe Technology. frequency) SEPTEMBER 19-23, 2010 – TORINO, ITALY

DAC30 Output Waveforms l Measurements performed with chips mounted in sockets (cf. Slide “Measurement setup“) l Driven by Virtex-4 (overclocked to 7 Gb/s) l Measured with Tektronix CSA8000 sampling scope (50 GHz bandwidth) page 11 T. Ellermeyer et al.: DA and AD Converters in SiGe Technology. SEPTEMBER 19-23, 2010 – TORINO, ITALY

Signal Impairments through Passive Components • Signal impairments due to passive components (e.g. traces, cables, connectors, package, etc.) DAC r 2 r 1 • Essential but challenging to maintain high frequency performance and effective resolution. • For example: Reflection • Reflection should be less than 1 LSB: 1 ¡ ¡ ¡ ¡ ¡ ¡ ¡ ¡ ¡ ¡ ¡ Number ¡ of ¡ bits r r b ⋅ ≤ = 1 2 b 2 • Written in dB: r r 1 2 b 6 . 02 ≤ − ⋅ − dB dB For 8-bit resolution and | r1 |=| r2 | : Reflections in DAC output signal è Return loss < -24 dB over the whole bandwidth on both ends (6-bit: <-18 dB) page 12 T. Ellermeyer et al.: DA and AD Converters in SiGe Technology. SEPTEMBER 19-23, 2010 – TORINO, ITALY

Topologies for High Speed AD-Converter Cores a) Massive Parallelization (SAR) T/H ADC T/H • ADC cores typically SAR converters J SAR: Slow but simple architecture / binary J output ADC T/H J J Bandwidth is determined by first set of T/H T/H L L Clock distribution difficult T/H ADC L Lots of calibration L ADC T/H b) Flash ADC Massive Parallelization J J Extremely fast K K Only low resolution: 6 bit => 2^(n-1)=63 comparators in parallel DECODE L L Complex logic (thermometer code to binary) Thermometer -> Binary • Also often used: Half-Flash/Pipeline Flash FF FF FF FF FF FF FF FF c) Interpolation/Folding J J Fast flash type converter J J Number of comparators reduced to 2^(n-1)/m T/H by folding m times (typ. m=2) L L Complex logic (thermometer code) Flash Converter K Analog stages required K page 13 T. Ellermeyer et al.: DA and AD Converters in SiGe Technology. SEPTEMBER 19-23, 2010 – TORINO, ITALY

Topologies for High Speed AD-Converter Cores Integer Binary Gray d) Serial ripple converter 0 6‘b000000 6‘b000000 K Little bit slower than flash K 1 6‘b000001 6‘b000001 J Simple architecture (number of amps / flip-flops equal J 2 6‘b000010 6‘b000011 to resolution) … … … J J Direct output of gray coded binary 31 6‘b011111 6‘b010000 32 6‘b100000 6‘b110000 K Highly analog concept K 33 6‘b100001 6‘b110001 K Propagation delay through each stage critical K … … … 62 6‘b111110 6‘b100001 63 6‘b111111 6‘b100000 Vin=V5 V4 V3 V2 V1 V0 CLK Q5 Q4 Q3 Q2 Q1 Q0 V5 V4 V3 V2 V1 V0 Vin Q5 Q4 Q3 Q2 Q1 Q0 page 14 T. Ellermeyer et al.: DA and AD Converters in SiGe Technology. SEPTEMBER 19-23, 2010 – TORINO, ITALY

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![Drivers Prof. S. Ben-Yaakov , DC-DC Converters [8- 2] Driving a MOSFET L D V in V o R L C 1](https://c.sambuz.com/1030065/drivers-s.webp)

![1 Prof. S. Ben-Yaakov , DC-DC Converters [8- 4] Gate Current V S 15V L D V in V o t V gs R g](https://c.sambuz.com/1030433/1-s.webp)