Cyber-Physical Systems Sensors and Actuators IECE 553/453 Fall 2020 - PowerPoint PPT Presentation

Cyber-Physical Systems Sensors and Actuators IECE 553/453 Fall 2020 Prof. Dola Saha 1 What is a sensor? An actuator? A sensor is a device that measures a physical quantity Input / Read from physical world An actuator is a

Cyber-Physical Systems Sensors and Actuators IECE 553/453– Fall 2020 Prof. Dola Saha 1

What is a sensor? An actuator? Ø A sensor is a device that measures a physical quantity Ø à Input / “Read from physical world” Ø An actuator is a device that modifies a physical quantity Ø à Output / “Write to physical world” 2

The Bridge between Cyber and Physical Ø Sensors: Ø Actuators: § Cameras § Motor controllers § Accelerometers § Solenoids § Gyroscopes § LEDs, lasers § Strain gauges § LCD and plasma displays § Microphones § Loudspeakers § Magnetometers § Switches § Radar/Lidar § Valves § Chemical sensors Ø Modeling Issues: § Pressure sensors § Physical dynamics, Noise, Bias, § Switches Sampling, Interactions, Faults 3

Sensor-Rich Cars Ø Source: Analog Devices 4

Sensor-Rich Cars Source: Wired Magazine Ø 5

Self-Driving Cars Google self-driving car 2.0 Berkeley PATH Project Demo, 1999, San Diego. 6

Kingvale Blower Ø Berkeley PATH Project, March 2005 7

Sensor Model Ø Linear and Affine Functions 𝑔 𝑦 𝑢 = 𝑏𝑦 𝑢 𝑔 𝑦 𝑢 = 𝑏𝑦 𝑢 + 𝑐 Ø Affine Sensor Model 𝑔 𝑦 𝑢 = 𝑏𝑦 𝑢 + 𝑐 + 𝑜 Ø Sensitivity (a), Bias (b) and Noise (n) § Sensitivity specifies the degree to which the measurement changes when the physical quantity changes 8

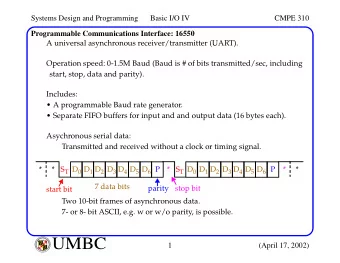

Analog-to-Digital Converter (ADC) Ø ADC is important almost to all application fields Ø Converts a continuous-time voltage signal within a given range to discrete-time digital values to quantify the voltage’s amplitudes x(t) x(n) ADC quantize continuous-time discrete-time analog signal digital values 9

Analog-to-Digital Converter (ADC) Ø Three performance parameters: § sampling rate – number of conversions per unit time § Resolution – number of bits an ADC output § power dissipation – power efficiency Ø Many ADC implementations: § sigma-delta (low sampling rate, high resolution) § successive-approximation (low power data acquisition) § Pipeline (high speed applications) 10

Successive-approximation (SAR) ADC 11

Successive-approximation (SAR) ADC Ø A sample and hold circuit to acquire input voltage(V in ) Ø An analog voltage comparator § compares V in to the output of the internal DAC and outputs the result of the comparison to the successive approximation register (SAR) Ø A successive approximation register subcircuit § Supplies an approximate digital code of V in to the internal DAC Ø An internal reference DAC § for comparison with V REF , supplies the comparator with an analog voltage equal to the digital code output of the SAR in . 12

Digital Quantization Ø SAR Control Logic performs Binary Search algorithm § DAC output is set to 1/2V REF § If V IN > V REF , SAR Control Logic sets the MSB of ADC, else MSB is cleared § V DAC is set to ¾ V REF or ¼ V REF depending on output of previous step § Repeat until ADC output has been determined Ø How long does it take to converge? 13

Successive-approximation (SAR) ADC • Binary search algorithm to gradually approaches the input voltage • Settle into ± ½ LSB bound within the time allowed T !"# = T $%&'()*+ + T #,*-./$),* T #,*-./$),* = N×T !"#_#(,12 T !"#$%&'( is software configurable 14

ADC Conversion Time T !"# = T $%&'()*+ + T #,*-./$),* Ø Suppose ADC CLK = 16 MHz and Sampling time = 4 cycles For 12-bit ADC T !"# = 4 + 12 = 16 cycles = 1µs For 6-bit ADC T !"# = 4 + 6 = 10 cycles = 625ns 15

Determining Minimum Sampling Time Ø When the switch is closed, the voltage across the capacitor increases exponentially. t= time required for the sample capacitor voltage 3 4 to settle to within one- V # t = V )* ×(1 − e 5 ! ) fourth of an LSB of the input voltage Sampling time is often software programmable! Smaller sampling error Larger sampling time Tradeoff Slower ADC speed 16

Resolution Resolution is determined by number of bits (in binary) to represent an analog input. Ø Example of two quantization methods (N = 3) Ø ½ Δ Δ V V Digital Result = 8loor 2 0 × Digital Result = round 2 0 × V 123 V 123 Max quantization error = Δ = V REF /2 3 Max quantization error = ± ½ Δ = ± V REF /2 4 round x = 8loor(x + 0.5) 17

Quantization Error Ø For N-bit ADC, it is limited to ±½ Δ Ø Δ = is the step size of the converter. Δ Ø Example: for 12-bit ADC and input voltage range [0, 3V] 𝑁𝑏𝑦 𝑅𝑣𝑏𝑜𝑢𝑗𝑨𝑏𝑢𝑗𝑝𝑜 𝐹𝑠𝑠𝑝𝑠 = 1 3𝑊 2 ∆= 2×2 45 = 0.367𝑛𝑊 Ø How to reduce error? 18

Aliasing Ø Example 1: § Consider a sinusoidal sound signal at 1 kHz : 𝑦 𝑢 = cos(2000𝜌𝑢) § Sampling interval T = 1/8000 § Samples 𝑡 𝑜 = 𝑔 𝑦 𝑜𝑈 = cos(𝜌𝑜/4) Ø Example 2: § Consider a sinusoidal sound signal at 9 kHz : 𝑦′ 𝑢 = cos(18000𝜌𝑢) § Sampling interval T = 1/8000 § Samples 𝑡 6 7 = 𝑔 𝑦 𝑜𝑈 897 97 97 = cos = cos : + 2𝜌𝑜 = cos = 𝑡(𝑜) : : Ø There are many distinct functions x that when sampled will yield the same signal s. 19

Minimum Sampling Rate Ø In order to be able to reconstruct the analog input signal, the sampling rate should be at least twice the maximum frequency component contained in the input signal Ø Example of two sine waves have the same sampling values. This is called aliasing. Nyquist–Shannon Sampling Theorem Ø Antialiasing § Pre-filtering: use analog hardware to filtering out high-frequency components and only sampling the low-frequency components. The high-frequency components are ignored. § Post-filtering: Oversample continuous signal, then use software to filter out high- frequency components 20

ADC Conversion Ø Input Range § Unipolar (0, V ADCMAX ) § Bipolar (-V ADCMAX , +V ADCMAX ) § Clipping: o If |V IN | > | V ADCMAX |, then |V OUT | = | V ADCMAX | 21

Automatic Gain Control (AGC) Ø Closed loop Feedback regulating circuit in an amplifier Ø Maintains a suitable signal amplitude at its output, despite variation of the signal amplitude at the input Ø The average or peak output signal level is used to dynamically adjust the gain of the amplifiers Ø Example Use: Radio Receivers, Audio Recorders, Microphone 22

Range and Dynamic Range Ø Range Ø Dynamic Range Ø Precision ( p ) 23

Power and RMS of Signal 670 3 = 1 Ø Average Power of a signal |𝑦 2 | 1 𝑄 𝑂 + 245 𝐷 = |𝑦 89:; | Ø Crest Factor 𝑦 -./ Ø Square root of the arithmetic mean of the squares of the values 1 𝑜 (𝑦 01 + 𝑦 11 + ⋯ + 𝑦 21 ) 𝑦 -./ = Ø Crest Factor § Sine Wave ~ 3.01dB, OFDM ~12dB 24

PAPR Ø Crest Factor in dB |𝑦 89:; | 𝐷 <= = 20𝑚𝑝 05 𝑦 -./ Ø Peak to Average Power Ratio (PAPR) 𝑄𝐵𝑄𝑆 = |𝑦 89:; | 1 𝑦 -./1 |𝑦 89:; | 1 𝑄𝐵𝑄𝑆 <= = 10𝑚𝑝 05 = 𝐷 <= 𝑦 -./1 25

Noise Ø Measured signal – Actual signal Ø Sensor Distortion Function: Sensor imperfections and errors due to quantization can be modeled as noise 26

Noise measured Ø The root mean square (RMS) of the noise is equal to the square root of the average value of n(t) 2 Ø Noise Power Ø Signal to Noise Ratio (SNR) 27

Noise modeled as statistical property Ø x(t) is a random variable with uniform distribution ranging from 0 to 1 Ø n(t) = f(x(t)) – x(t) § ranges from −1/8 to 0 28

Precision and Accuracy Ø Precision: how close the two measured values can be Ø Accuracy: how close is the measured value to the true value 29

Noise & Signal Conditioning |X d ( w ) | 2 |X n ( w ) | 2 w Filter: F ( w ) w Filtered signal: |X d ( w ) F ( w ) | 2 |X n ( w ) F ( w ) | 2 w 30

Example Gain Control Ø AD8338 31

Digital-to-analog converter (DAC) Converts digital data into a voltage signal by a N-bit DAC Ø :;< × 𝐸𝑗𝑗𝑢𝑏𝑚 𝑊𝑏𝑚𝑣𝑓 𝐸𝐵𝐷 678978 = 𝑊 2 = For 12-bit DAC Ø :;< × 𝐸𝑗𝑗𝑢𝑏𝑚 𝑊𝑏𝑚𝑣𝑓 𝐸𝐵𝐷 678978 = 𝑊 4096 Many applications: Ø § digital audio § waveform generation Performance parameters Ø § speed § resolution § power dissipation § glitches 32

DAC Implementations § Pulse-width modulator (PWM) § Binary-weighted resistor (We will use this one as an example) § R-2R ladder (A special case of binary-weighted resistor) 33

Binary-weighted Resistor DAC - V ref D 3 D 2 D 1 D 0 R ref R/8 R/4 R/2 R V out ]^_ × 𝑆 ]^_ ×(𝐸 ` ×2 ` + 𝐸 a ×2 a + 𝐸 b ×2 + 𝐸 c ) 𝑊 Z[\ = 𝑊 𝑆 34

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.