DRAMA: Exploiting DRAM Addressing for Cross-CPU Attacks Peter - PowerPoint PPT Presentation

S C I E N C E P A S S I O N T E C H N O L O G Y DRAMA: Exploiting DRAM Addressing for Cross-CPU Attacks Peter Pessl, Daniel Gruss, Clmentine Maurice, Michael Schwarz, Stefan Mangard IAIK, Graz

S C I E N C E P A S S I O N T E C H N O L O G Y DRAMA: Exploiting DRAM Addressing for Cross-CPU Attacks Peter Pessl, Daniel Gruss, Clémentine Maurice, Michael Schwarz, Stefan Mangard IAIK, Graz University of Technology, Austria Usenix Security 2016, August 11 u www.iaik.tugraz.at

www.iaik.tugraz.at Pessl, Gruss, Maurice, Schwarz, Mangard 2 Usenix Security 2016, August 11

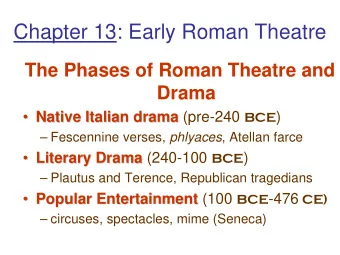

www.iaik.tugraz.at Setting – Cloud Servers Multi-CPU (multi-socket) systems Multiple tenants separate VMs dedicated CPUs no shared cache No shared memory no cross-VM memory deduplication Previously slow covert channel (< 1 kbps) no side channel Pessl, Gruss, Maurice, Schwarz, Mangard 3 Usenix Security 2016, August 11

www.iaik.tugraz.at Overview Cross-CPU attacks using DRAM a ddressing ( DRAMA ) fast covert channel (up to 2 Mbps) first side-channel attack Reverse-engineered DRAM addressing two approaches Improving existing attacks Pessl, Gruss, Maurice, Schwarz, Mangard 4 Usenix Security 2016, August 11

www.iaik.tugraz.at DRAM Organization Hierarchy of MC CPU 1 DRAM Bus CPUs Interconnect MC CPU 2 DRAM Bus Pessl, Gruss, Maurice, Schwarz, Mangard 5 Usenix Security 2016, August 11

www.iaik.tugraz.at DRAM Organization Hierarchy of DIMM DIMM CPUs Channels Channel A DIMMs MC CPU Channel B DIMM DIMM Pessl, Gruss, Maurice, Schwarz, Mangard 6 Usenix Security 2016, August 11

www.iaik.tugraz.at DRAM Organization Hierarchy of CPUs Bank 1 Channels Bank 2 DIMMs .. .. Bank 8 Ranks Banks Pessl, Gruss, Maurice, Schwarz, Mangard 7 Usenix Security 2016, August 11

www.iaik.tugraz.at DRAM Banks Row 1 Row 2 Row N Row Buffer Memory array rows of columns Row Buffer buffers one entire row (8 KB) Pessl, Gruss, Maurice, Schwarz, Mangard 8 Usenix Security 2016, August 11

www.iaik.tugraz.at The Row Buffer Behavior similar to a cache row hits fast access row conflicts slow access Pessl, Gruss, Maurice, Schwarz, Mangard 9 Usenix Security 2016, August 11

www.iaik.tugraz.at Reverse Engineering of DRAM Addressing Pessl, Gruss, Maurice, Schwarz, Mangard 10 Usenix Security 2016, August 11

www.iaik.tugraz.at Reverse-Engineering DRAM Addressing Mapping to banks using physical-address bits „Complex“ addressing functions distribute traffic to channels/banks undisclosed (Intel) Two approaches to reverse engineer Presumption: linear functions (XORs) Pessl, Gruss, Maurice, Schwarz, Mangard 11 Usenix Security 2016, August 11

www.iaik.tugraz.at Approach 1: Probing the Memory Bus Probing of control signals CS, BA, … measure voltage with Osci. recover logic value Repeated access to address until value is determined Function reconstruction linear algebra over bits Pessl, Gruss, Maurice, Schwarz, Mangard 12 Usenix Security 2016, August 11

www.iaik.tugraz.at Approach 2: Fully Automated SW-based Exploit timing differences Measuring phase build sets of same-bank addresses alternating access to two addresses measure avg. access time Reconstruction phase exhaustive search over linear functions with up to n set coefficients Total time: seconds Pessl, Gruss, Maurice, Schwarz, Mangard 13 Usenix Security 2016, August 11

www.iaik.tugraz.at Comparison Probing recover function labels find a ground truth equipment and access to internals of machine SW-based fully automated ability to run remotely, sandboxed, and on mobile devices Pessl, Gruss, Maurice, Schwarz, Mangard 14 Usenix Security 2016, August 11

www.iaik.tugraz.at Some Results - Desktop BA0 BA1 Rank BA2 ... 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 ... Ch. Intel Haswell (desktop system) – DDR3 Pessl, Gruss, Maurice, Schwarz, Mangard 15 Usenix Security 2016, August 11

www.iaik.tugraz.at Some Results – Server System BG0 CPU Rank BG1 BA0 BA1 ... 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 ... Ch. Dual-CPU Intel Haswell-EP – DDR4 Pessl, Gruss, Maurice, Schwarz, Mangard 16 Usenix Security 2016, August 11

www.iaik.tugraz.at Some Results – Mobile Rank BA0 BA1 BA2 ... 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 ... Ch. Samsung Exynos 7420 (Galaxy S6) – LPDDR4 Pessl, Gruss, Maurice, Schwarz, Mangard 17 Usenix Security 2016, August 11

www.iaik.tugraz.at Cross-CPU Attacks …and how it continues with Romeo and Juliet Pessl, Gruss, Maurice, Schwarz, Mangard 18 Usenix Security 2016, August 11

www.iaik.tugraz.at High-speed covert channel Pessl, Gruss, Maurice, Schwarz, Mangard 19 Usenix Security 2016, August 11

www.iaik.tugraz.at Concept Occupy different rows in the same bank Sender Sender Sender send 1: continuously access row Receiver Receiver Receiver s end 0: don‘t do anything Receiver access row and measure avg. time Row Buffer infer sent bits based on time Pessl, Gruss, Maurice, Schwarz, Mangard 20 Usenix Security 2016, August 11

www.iaik.tugraz.at Implementation Each bank is a channel use up to 8 banks in parallel multithreading Performance: desktop: 2.1 Mbps multi-CPU server: 1.2 Mbps Intel Haswell (desktop system) Pessl, Gruss, Maurice, Schwarz, Mangard 21 Usenix Security 2016, August 11

www.iaik.tugraz.at Performance Comparison Performance Cross-CPU No Shared Memory Ours 2.1 Mbps Prime+Probe [2] 536 Kbps Flush+Reload [2] 2.3 Mbps Flush+Flush [2] 3.8 Mbps Memory Bus Contention [3] 746 bps Deduplication [4] 90 bps Pessl, Gruss, Maurice, Schwarz, Mangard 22 Usenix Security 2016, August 11

www.iaik.tugraz.at Low-noise side-channel attack Pessl, Gruss, Maurice, Schwarz, Mangard 23 Usenix Security 2016, August 11

www.iaik.tugraz.at Spying on Memory Accesses Memory in the same row/bank row size 8 KB / page size 4 KB Victim Victim Victim Spy activates conflict row Victim Spy Spy Spy Victim computes and possibly accesses shared row Spy accesses shared row Row Buffer fast row hit victim access Pessl, Gruss, Maurice, Schwarz, Mangard 24 Usenix Security 2016, August 11

www.iaik.tugraz.at Example Keystrokes in Firefox address bar Pessl, Gruss, Maurice, Schwarz, Mangard 25 Usenix Security 2016, August 11

www.iaik.tugraz.at Implementation high spatial accuracy (down to 512 B) very low number of false positives monitor single events Finding addresses: template attack [1] automatic location of vulnerable addresses scan large fraction of memory (4 KB pages) Pessl, Gruss, Maurice, Schwarz, Mangard 26 Usenix Security 2016, August 11

www.iaik.tugraz.at Countermeasures to DRAMA Restrictions of rdtsc clflush Multi-CPU: separating DRAM for tenants only access to CPU-local memory degradation into single-CPU system Detection via high number of cache misses / row conflicts Pessl, Gruss, Maurice, Schwarz, Mangard 27 Usenix Security 2016, August 11

www.iaik.tugraz.at Improving Attacks - Rowhammer Rowhammer inducing bit flips in DRAM by quickly switching rows requires addressing functions First documented bit flips on DDR4 Jan. 2016 Pessl, Gruss, Maurice, Schwarz, Mangard 28 Usenix Security 2016, August 11

www.iaik.tugraz.at The End … of Romeo and Juliet Pessl, Gruss, Maurice, Schwarz, Mangard 29 Usenix Security 2016, August 11

www.iaik.tugraz.at Source code for reverse-engineering tool and side-channel attack at https://github.com/IAIK/drama Pessl, Gruss, Maurice, Schwarz, Mangard 30 Usenix Security 2016, August 11

www.iaik.tugraz.at S C I E N C E P A S S I O N T E C H N O L O G Y DRAMA: Exploiting DRAM Addressing for Cross-CPU Attacks Peter Pessl, Daniel Gruss, Clémentine Maurice, Michael Schwarz, Stefan Mangard IAIK, Graz University of Technology, Austria Usenix Security 2016, August 11 Pessl, Gruss, Maurice, Schwarz, Mangard 31 u www.iaik.tugraz.at Usenix Security 2016, August 11

www.iaik.tugraz.at Bibliography [1] Gruss, Spreitzer, Mangard. Cache Template Attacks: Automating Attacks on Inclusive Last-Level Caches. In Usenix Security 2015 Gruss, Maurice, Wagner, Mangard. Flush+Flush : A Fast and Stealthy Cache Attack. In DIMVA’16 [2] [3] Wu, Xu, Wang. Whispers in the Hyper-space: High-bandwidth and Reliable Covert Channel Attacks Inside the Cloud. In Usenix Security 2012 [4] Xiao, Xu, Huang, Wang. Security implications of memory deduplication in a virtualized environment. In DSN‘13 Pessl, Gruss, Maurice, Schwarz, Mangard 32 Usenix Security 2016, August 11

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.